Chip packaging structure and preparation method thereof

A chip packaging structure and chip technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as high cost, chip damage, and easy warpage, and achieve warpage control and low material cost , the effect of expanding the utilization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

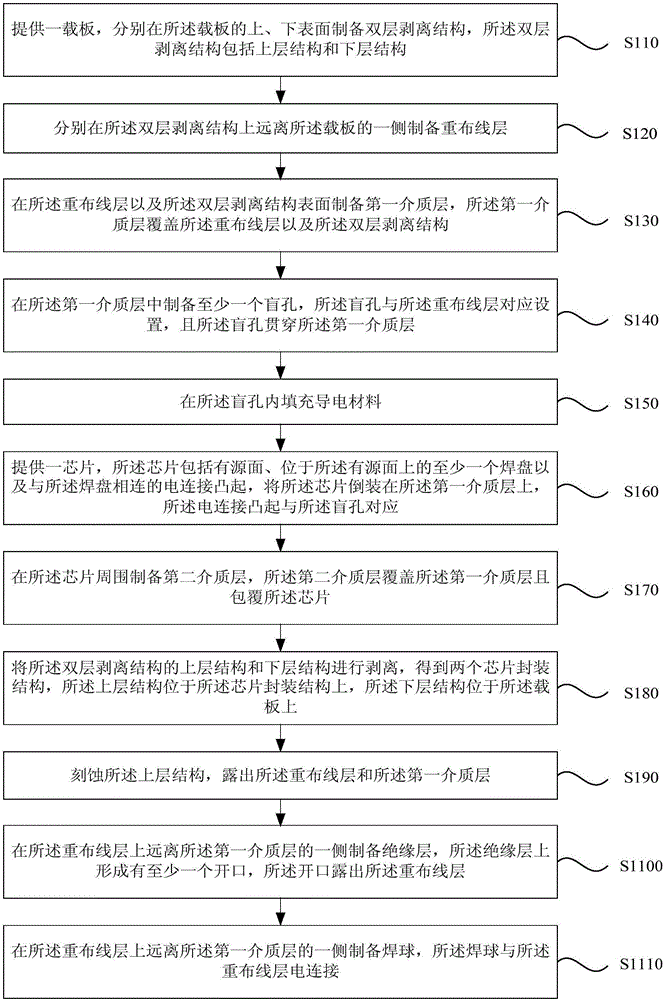

[0042] Embodiments of the present invention provide a chip packaging structure and a manufacturing method thereof. figure 1 It is a schematic flow chart of a method for preparing a chip packaging structure provided by an embodiment of the present invention, such as figure 1 As shown, the method for preparing the chip package structure provided by the embodiment of the present invention may include the following steps:

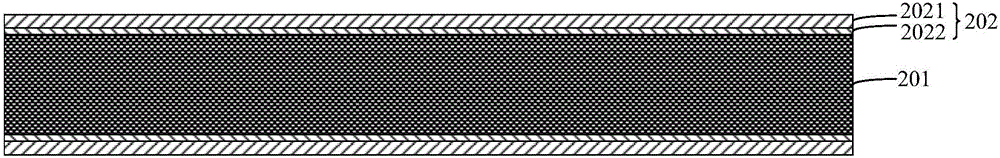

[0043] S110. Provide a carrier plate, prepare a double-layer peeling structure on the upper and lower surfaces of the carrier plate, and the double-layer peeling structure includes an upper layer structure and a lower layer structure.

[0044] Exemplary, figure 2 is a schematic cross-sectional view of the carrier plate provided by the embodiment of the present invention, such as figure 2 As shown, the material of the carrier 201 can be silicon, silicon dioxide, ceramics, glass, metal, alloy, and organic material, etc., and the shape of the carrier can be re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More