Functional test method for SiP (system in package) embedded memory

A technology of functional testing and memory, which is applied in the direction of electronic circuit testing, instruments, measuring electronics, etc. It can solve problems such as difficult fault detection, high reliability requirements, and limited signals, so as to improve test efficiency, increase fault coverage, The effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

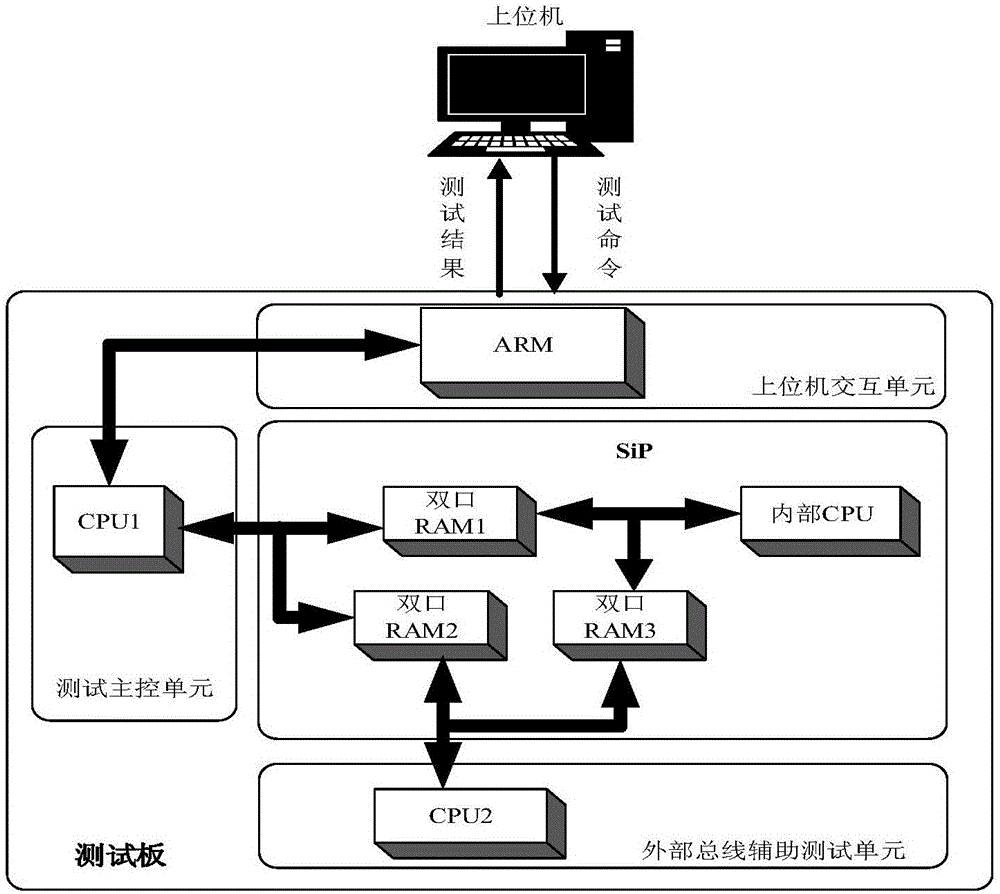

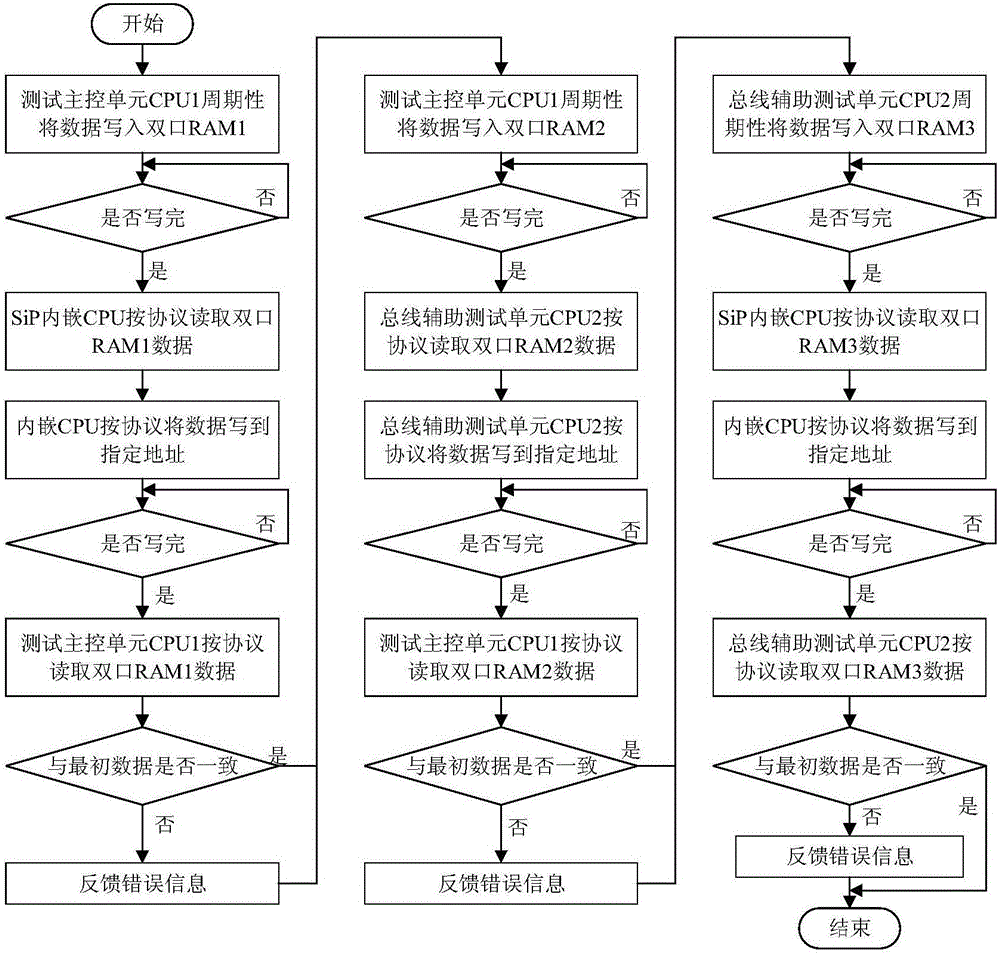

[0042] This embodiment applies the test flow and test method of the technical solution of the present invention, based on the functional test requirements of a certain SiP dual-port RAM, the test connection structure diagram of the dual-port RAM is shown in the attached figure 1 As shown, perform a functional test on it;

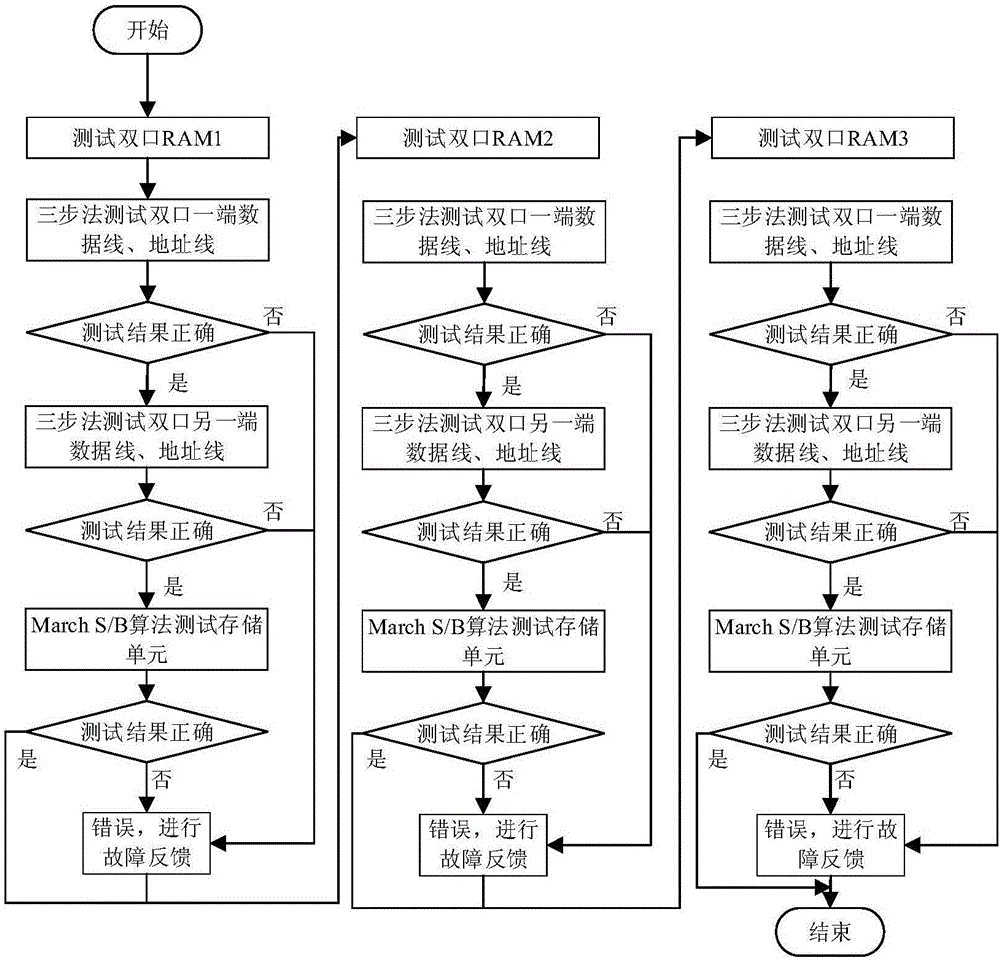

[0043] Firstly, the screening test is carried out, and the independent screening test process of dual-port RAM is attached figure 2 Shown:

[0044] (1) Test the main control unit CPU1 using a three-step method to test the data bus and address bus on the side of the dual-port RAM1 connected to the test main control unit CPU1;

[0045](2) the test main control unit judges whether there is a fault in the data bus and the address bus test of the dual-port RAM1 this side, if there is a fault, the test is interrupted and the fault is fed back to the test user; if there is no fault, continue the test, and go to step (3) );

[0046] (3) The test main control uni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More