CMOS clock generator

A technology of clock generator and comparator, which is applied in the direction of pulse generation, electric pulse generation, electrical components, etc., can solve the problem of reducing the accuracy of the clock cycle, and achieve the effect of improving accuracy and reducing temperature coefficient

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

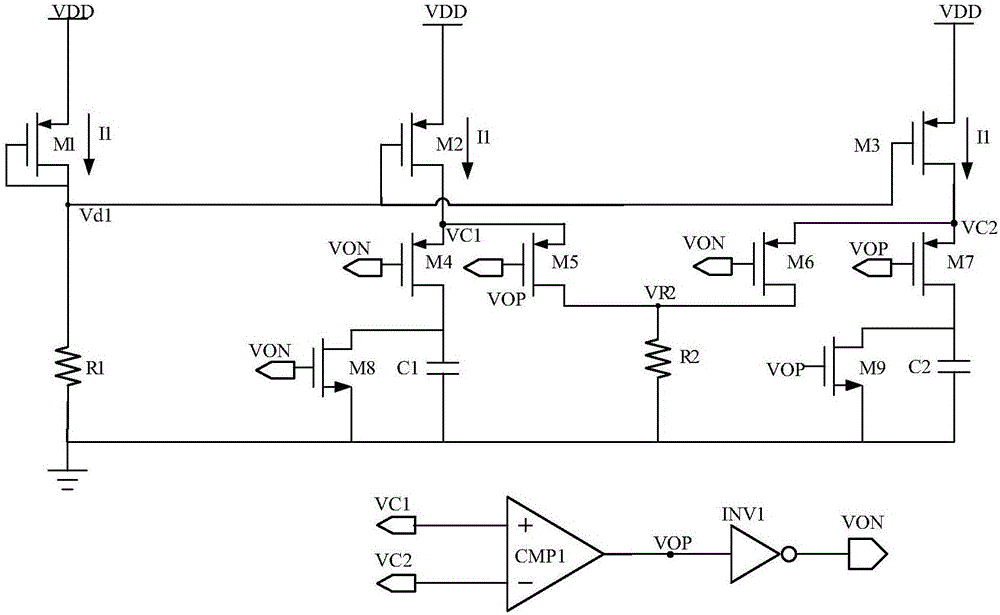

[0027] Embodiments of the present invention will now be described with reference to the drawings, in which like reference numerals represent like elements. As mentioned above, the present invention provides a CMOS clock generator. The clock period of the clock signal produced by the CMOS clock generator of the present invention has nothing to do with the delay of the comparator, which avoids the delay caused by the difference of the comparator under different temperature conditions. The problem of different output clock periods reduces the temperature coefficient and improves the accuracy of the clock period.

[0028] Please refer to figure 2 , figure 2 It is a structural block diagram of the CMOS clock generator of the present invention. As shown in the figure, the CMOS clock generator of the present invention includes a current generating unit, a periodic signal generating unit, a voltage negative feedback unit and a square wave signal generating unit. The current gener...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com