Direct memory operation implementation method based on coherent acceleration interface

An implementation method and consistent technology, applied in the direction of instruments, electrical digital data processing, etc., to maximize the efficiency utilization, improve the transmission reliability, and simplify the system complexity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical solution of the present invention will be further introduced in detail below in conjunction with the accompanying drawings of the description.

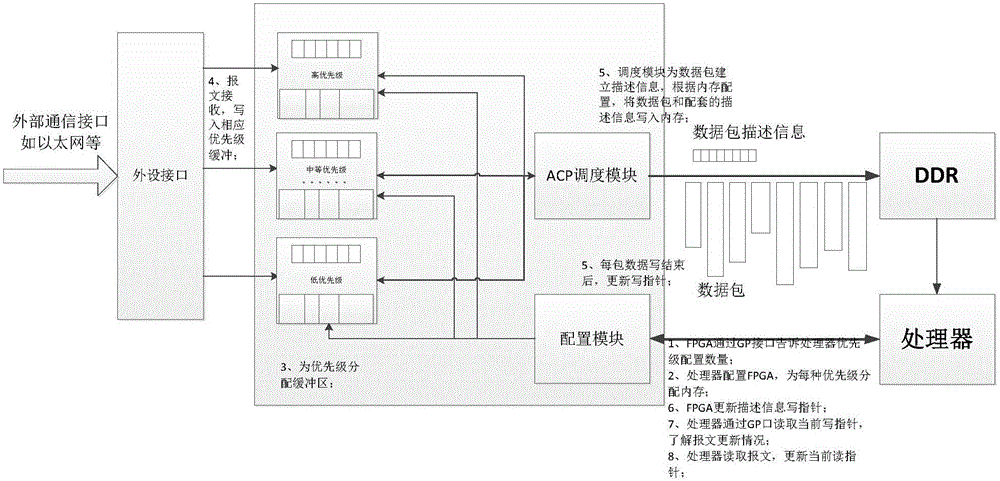

[0027] This application discloses an active variable-length DMA implementation method based on a consistent acceleration interface, as shown in the attached image 3 shown.

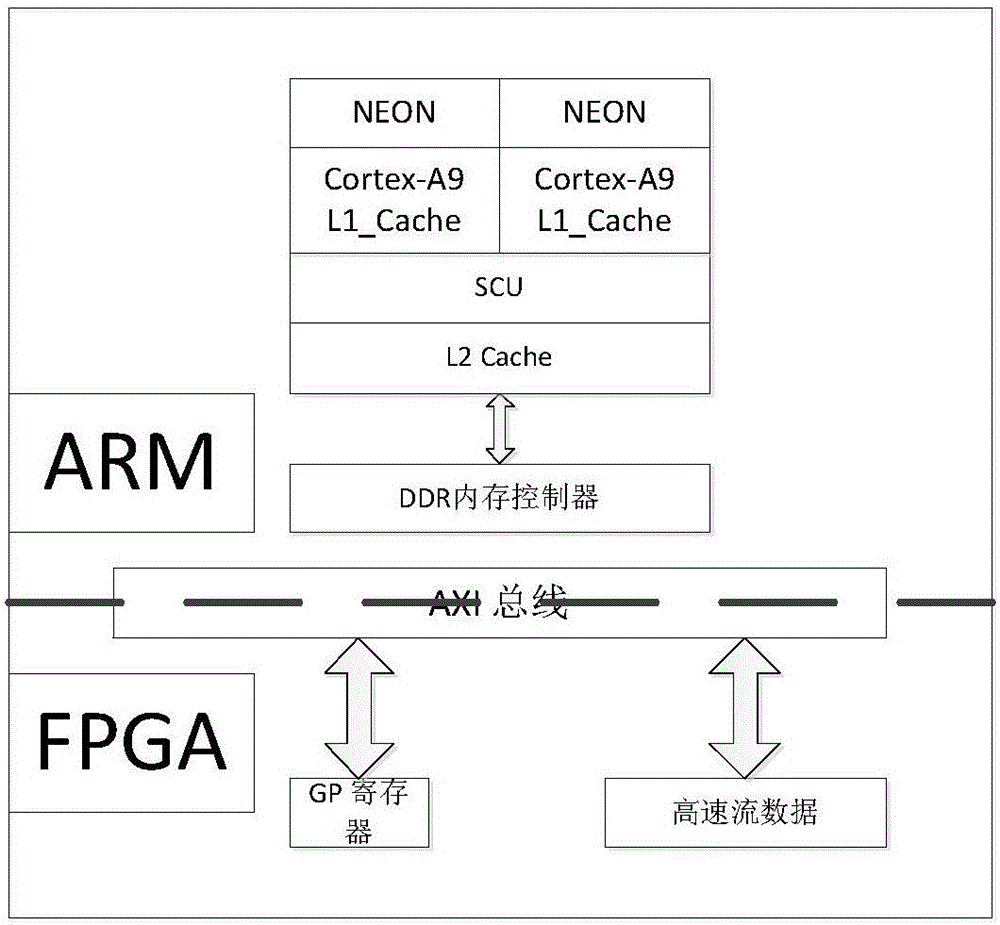

[0028] Described Zynq chip is the Zynq dual-core series chip of Xilinx Company, is made up of dual-core ARM and FPGA, is connected by the advanced extensible interface (AXI) bus in chip between dual-core ARM and FPGA, and dual-core ARM and FPGA share external memory. The internal hardware structure is as figure 1 shown.

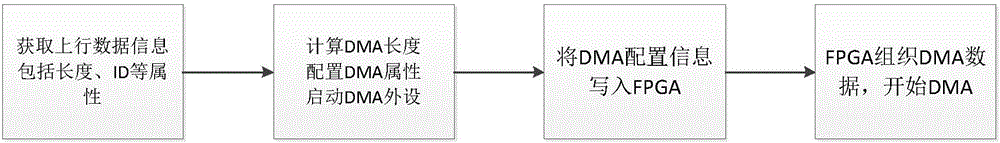

[0029] attached figure 2 In the existing processor + FPGA implementation scheme, to complete a DMA task, the processor first needs to read the summary information of the uplink data from the FPGA. The processor calculates the transmission length of the DMA based on the summary information, starts the DMA receiving task, ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap