Chip internal logic verify system and method

A technology of internal logic and verification system, applied in the field of electronics, can solve problems such as inevitable internal defects of products, affecting stable operation of the system, economic losses, etc., to achieve the effect of improving test efficiency and test coverage, saving test time, and reducing workload

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the technical problems, technical solutions and advantages to be solved by the present invention clearer, the following will describe in detail with reference to the accompanying drawings and specific examples.

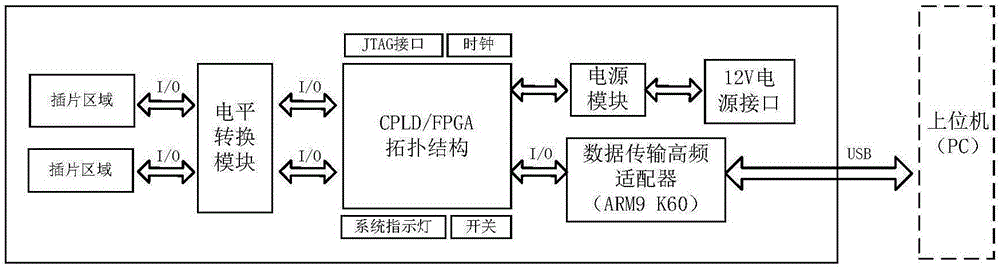

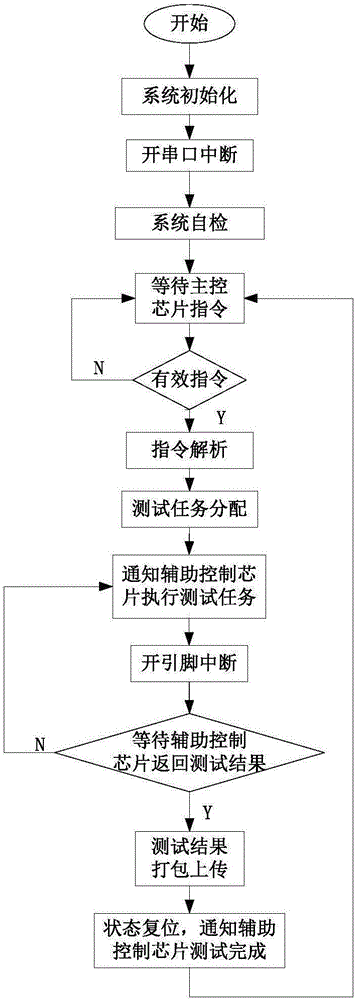

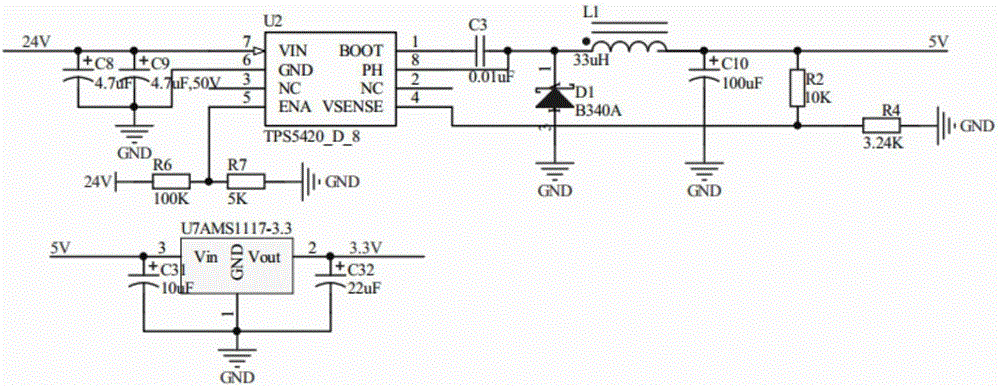

[0035] The principle of the embodiment of the present invention is: design through hardware platform design, utilize CPLD (programmable logic controller) and its peripheral circuit to simulate the internal input and output situation of the specified system, complete the configuration of I / O pulse signal, and load the excitation signal to The chip to be tested is to test some chips used by the specified system to judge whether its output logic is consistent with the standard output, so as to verify the correctness of the chip and ensure that the internal program files of the chip are correctly programmed and downloaded.

[0036] Such as figure 1 As shown, the internal logic verification system of the chip according to the embodiment of the prese...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More