FPGA transistor size adjustment method

An adjustment method and transistor technology, applied in the field of FPGA architecture exploration, can solve problems such as reducing the efficiency of architecture exploration, and achieve the effects of reducing the amount of training data, fast transistor size adjustment, and accurate results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention provides an accurate transistor size adjustment method, which can quickly find a result that meets the design target under the requirement of a large number of design iterations, and the finally obtained optimization result can be applied to an architecture exploration tool to speed up the architecture exploration process. The specific technical scheme is as follows:

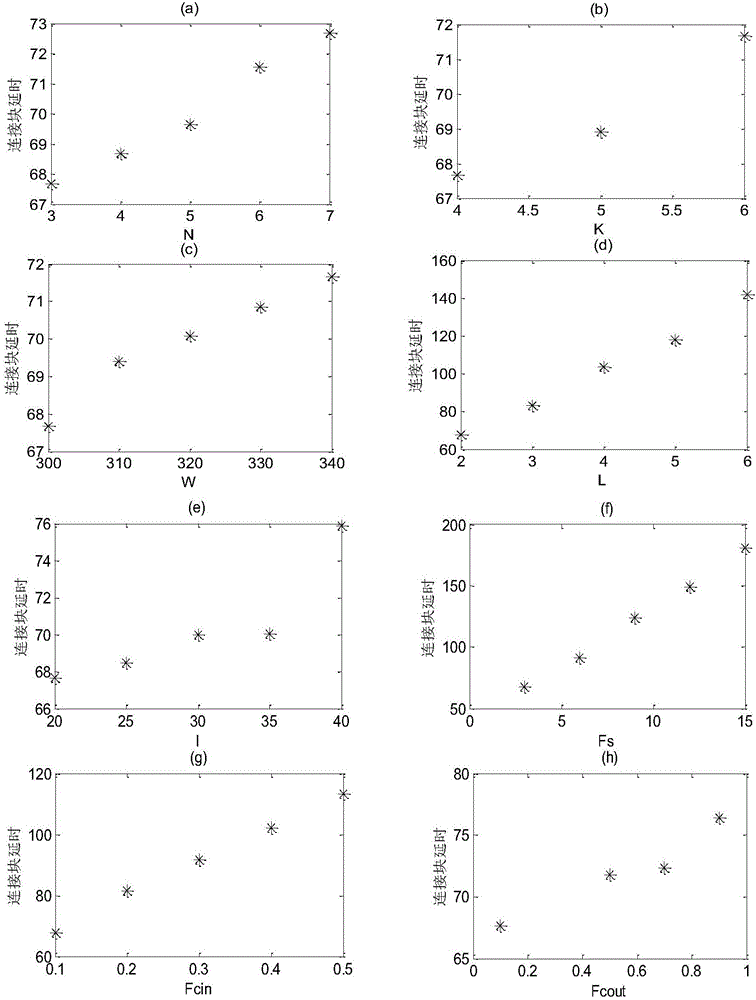

[0030] 1) Determine the key parameters that affect the FPGA delay.

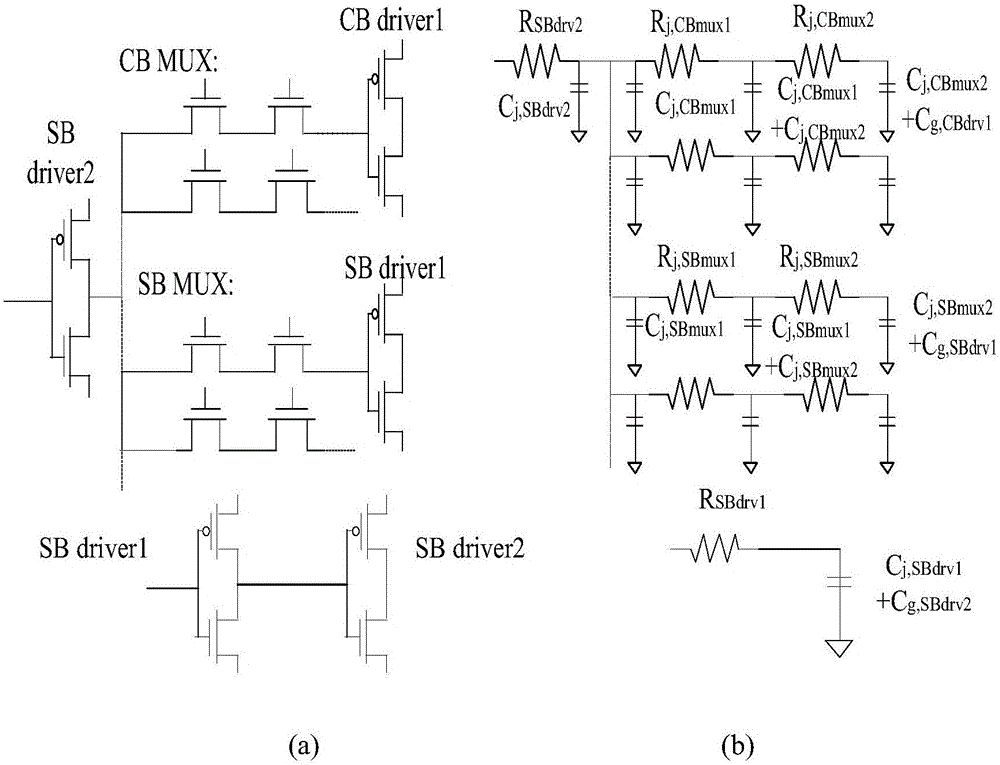

[0031] 2) According to the impact of parameters on the delay of each sub-circuit in the FPGA, a corresponding Elmore delay model is established for each circuit.

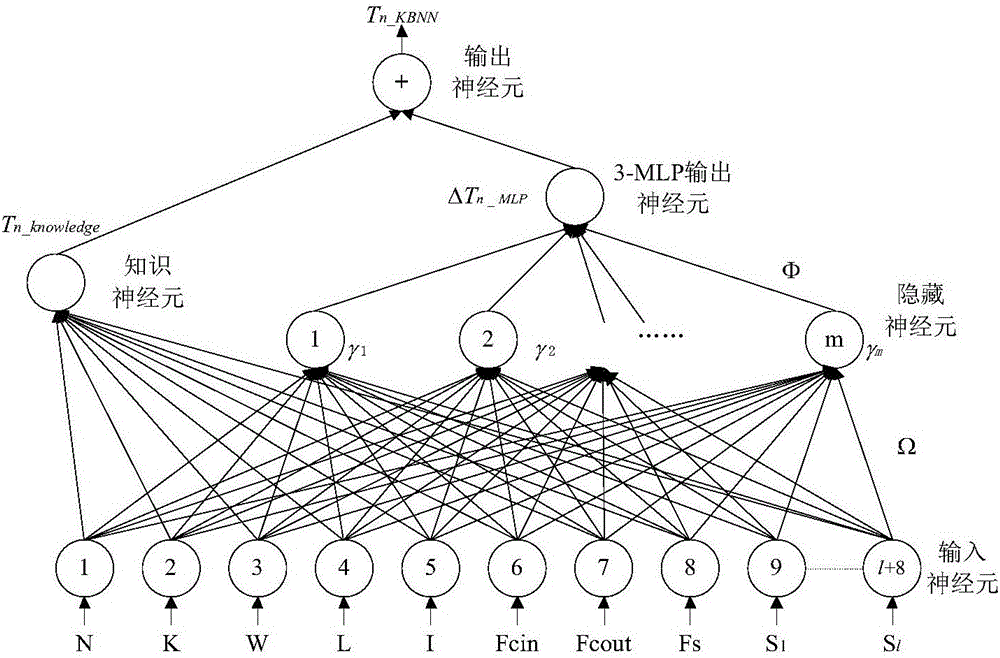

[0032] 3) Combine the Elmore delay model of FPGA with the neural network to establish the KBNN delay model and train it to determine the training error E t and validation error E v Minimum weights Ω and Φ and number of hidden neurons m.

[0033] 4) Establish an improved minimum-width transistor area model to estimate the area of the FPGA island.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More