Method for designing internal interface of real-time emulator of active power distribution network based on multi-FPGA (field programmable gate array)

A technology of real-time simulation and design method, which is applied in the fields of instruments, electrical digital data processing, etc., and can solve the problems of limited computing power of real-time simulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

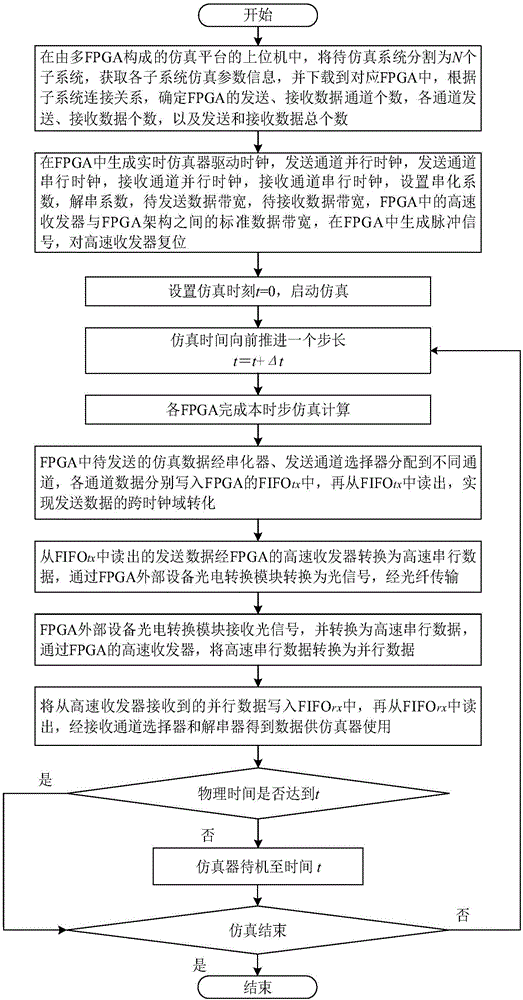

Method used

Image

Examples

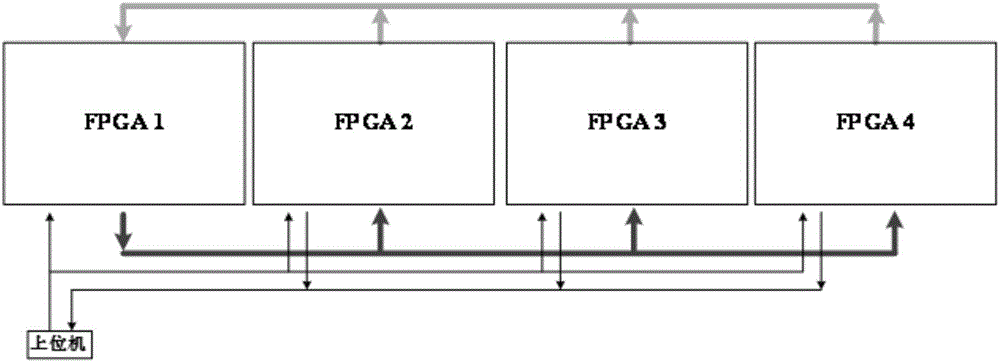

specific example

[0051] In this example, the multi-FPGA-based real-time simulator uses four Stratix V series FPGA5SGSMD5K2F40C2N from Altera and its supporting official development boards to complete the real-time simulation of the active distribution network with photovoltaics and batteries. Simulation platform such as image 3As shown, optical fiber is used to realize signal transmission between FPGA development boards. The entire real-time simulator is driven by a 125MHz clock, the parallel clock of the sending channel is 125MHz, the serial clock of the sending channel is 2500MHz, the parallel clock of the receiving channel is 125MHz, the serial clock of the receiving channel is 2500MHz, and the single-channel data transmission rate between FPGAs is 2500Mbps .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More