Chip protection ring, semiconductor chip, semiconductor wafer and packaging method

A technology for chip packaging and guard rings, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as chip 10 failure, solder balls are too large, and cannot be re-bonded

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046]In order to make the purpose and features of the present invention more obvious and understandable, the specific implementation of the present invention will be further described below in conjunction with the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments.

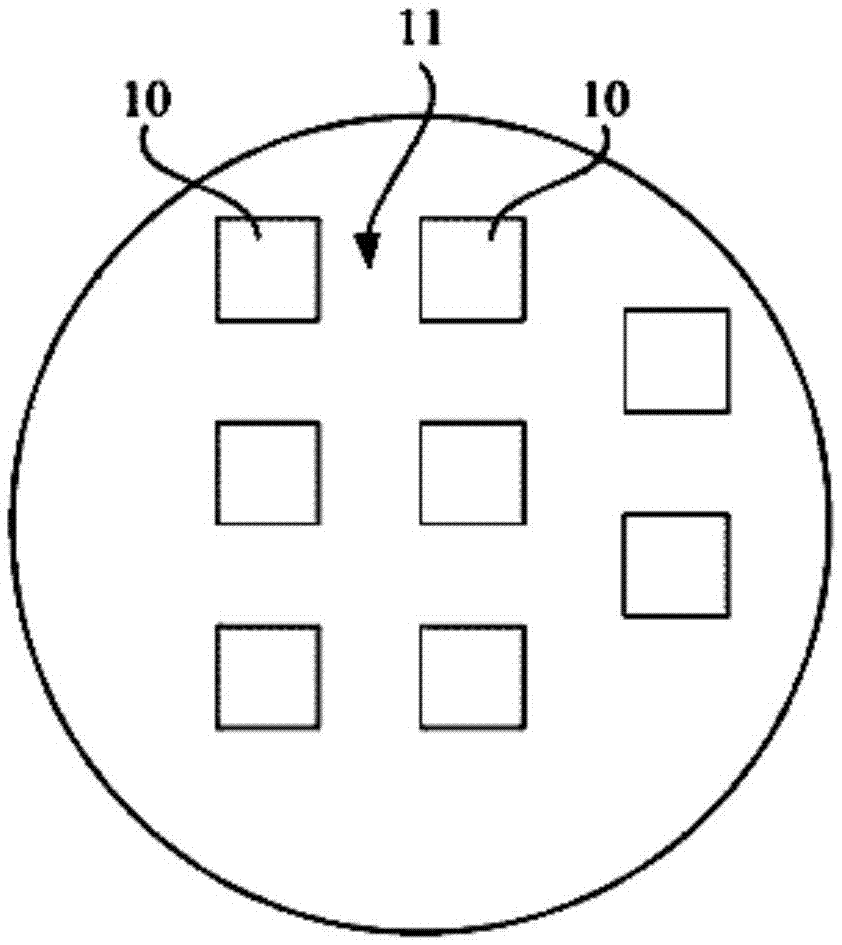

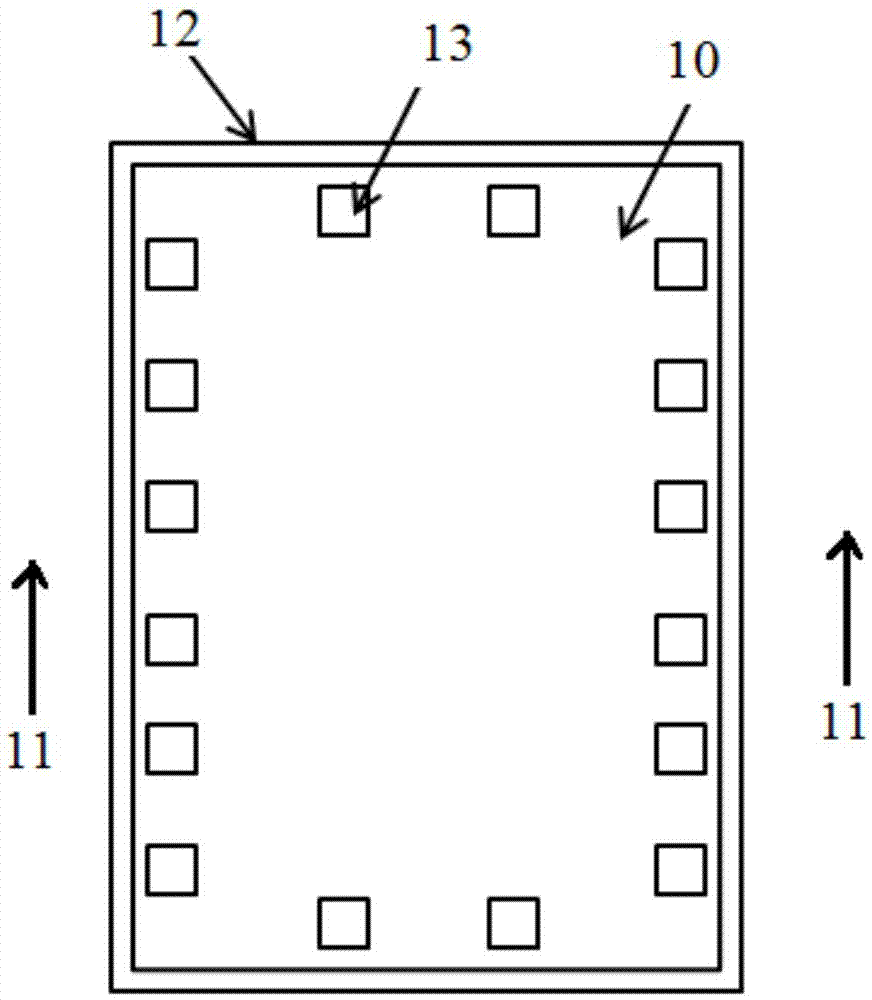

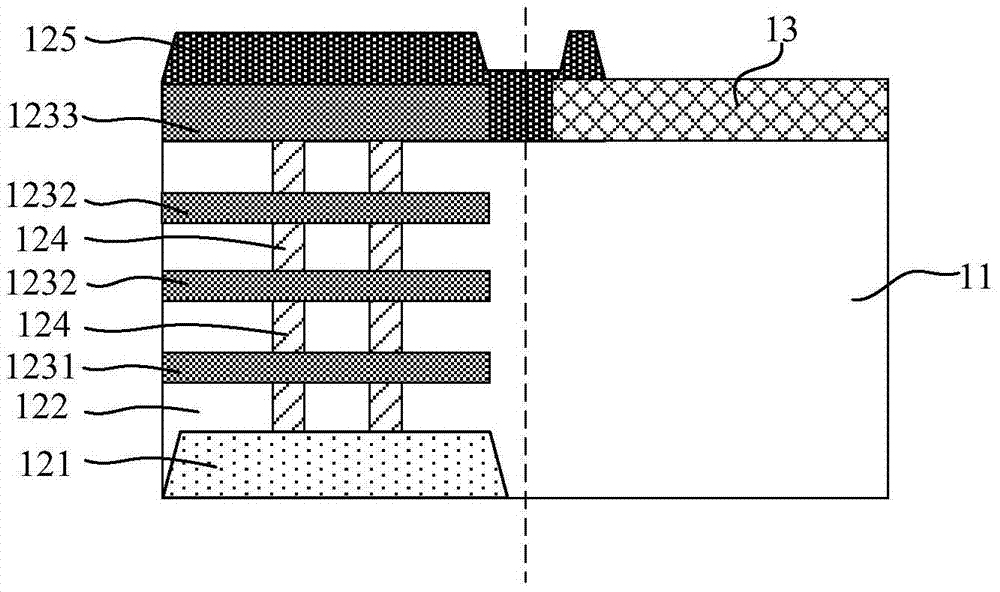

[0047] Please also refer to Figures 5A to 5D , the present invention proposes a chip protection ring (seal ring) 12, arranged around a chip and formed on the same semiconductor substrate (not shown) with the chip, the chip protection ring 12 includes a seal ring supported by the semiconductor substrate Several metal rings 123 stacked in sequence and conductive plugs 124 arranged between adjacent metal rings, and each metal ring 123 is arranged around the chip, wherein the top metal ring (top metal, TM) 1231 is Discontinuous metal rings are disconnected between adjacent bonding pads (Pad) 13 of the chip, the radius of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More