NBTI (negative bias temperature instability) degradation detection system for SoC (system on chip)

A detection system and switch tube technology, applied in the field of microelectronics, can solve the problems of complex test methods and low test convenience

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

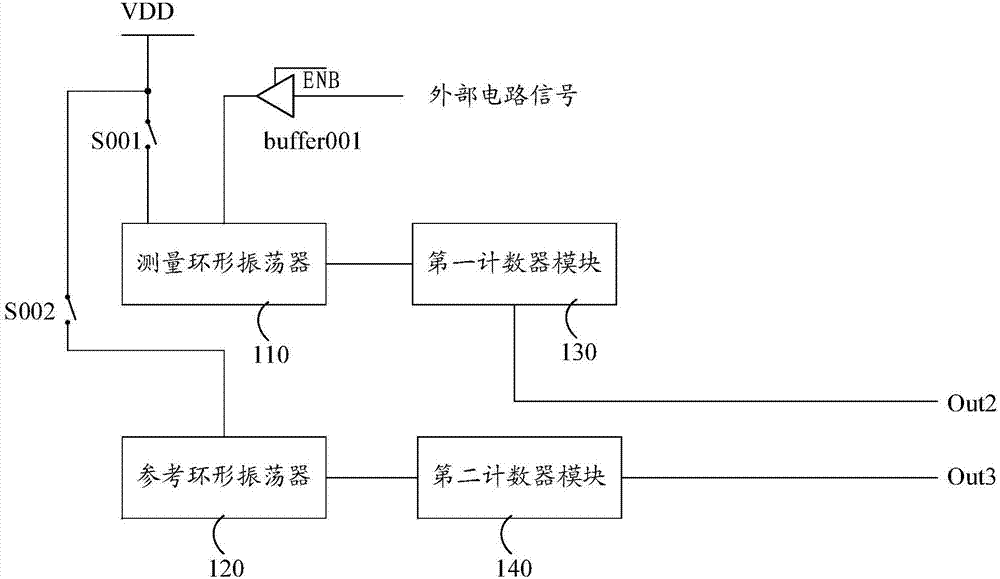

[0015] In one embodiment, an SoC on-chip NBTI degradation detection system, such as figure 1 As shown, it includes a measurement ring oscillator 110, a reference ring oscillator 120, a first counter module 130 and a second counter module 140, the measurement ring oscillator 110 is connected to the power supply terminal VDD and the first counter module 130, and the reference ring oscillator 120 is connected to The power terminal VDD and the second counter module 140 .

[0016] The measurement ring oscillator 110 is used to receive an external circuit signal representing the same aging environment as the circuit under test on the SoC chip, and after stopping receiving the external circuit signal, it is connected to the power supply terminal VDD input simultaneously with the reference ring oscillator 120 voltage and start to oscillate, the measurement ring oscillator 110 and the reference ring oscillator 120 output waveforms to the first counter module 130 and the second counter ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com