Microcontroller architecture for embedded CPU core and complete hardware operation system

A microprocessor and operating system technology, applied in the direction of program control, computer control, general control system, etc., to achieve the effect of improving the efficiency of task switching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

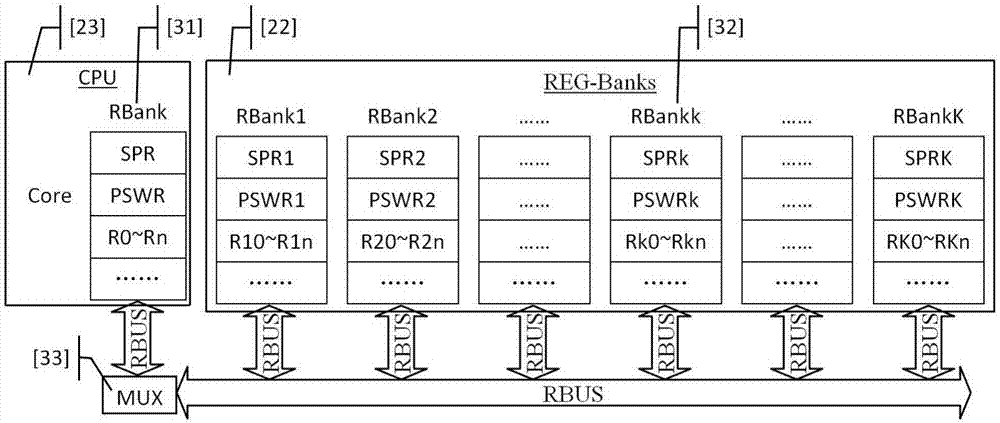

[0043] This embodiment selects the MCS-51 microprocessor core as the microprocessor core CPU-Core, and the embedded real-time operating system μC / OS-II is hardwareized as the semi-hardware operating system h-HRTOS, according to the register group RBank of MCS-51 Extended mapped register bank REG-Banks; integrate MCS-51 microprocessor core, mapped register bank REG-Banks and hardwareized μC / OS-II semi-hardware operating system h-HRTOS into one chip to form an embedded MCS-51 microcontroller (microcontroller) with complete hardware operating system: HCPU-51, such as Figure 7 As shown, HCPU-51 is a microprocessor core integrating MCS-51 processor core, mapping register REG-Banks group and μC / OS-II semi-hardware operating system h-HRTOS. MCS-51 is a standard MCS-51 core, including register bank RBank=[SP,A,B,PSW,DPTR,R0~R7]; REG-Banks is a 64-group register bank library extended to RBank, RBankk=[SPk ,Ak,Bk,PSWk,DPTRk,R0~R7k],k∈[1,K]; MUX is a demultiplexer, RBUS is a register...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More