Integrated circuit layout data processing task allocation method and device and cluster system

A technology for layout data and processing tasks, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems that affect cluster parallel acceleration ratio and efficiency, large time difference, and calculation time difference, etc., to reduce communication The overhead and time difference are small, and the effect of improving the parallel acceleration ratio and efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

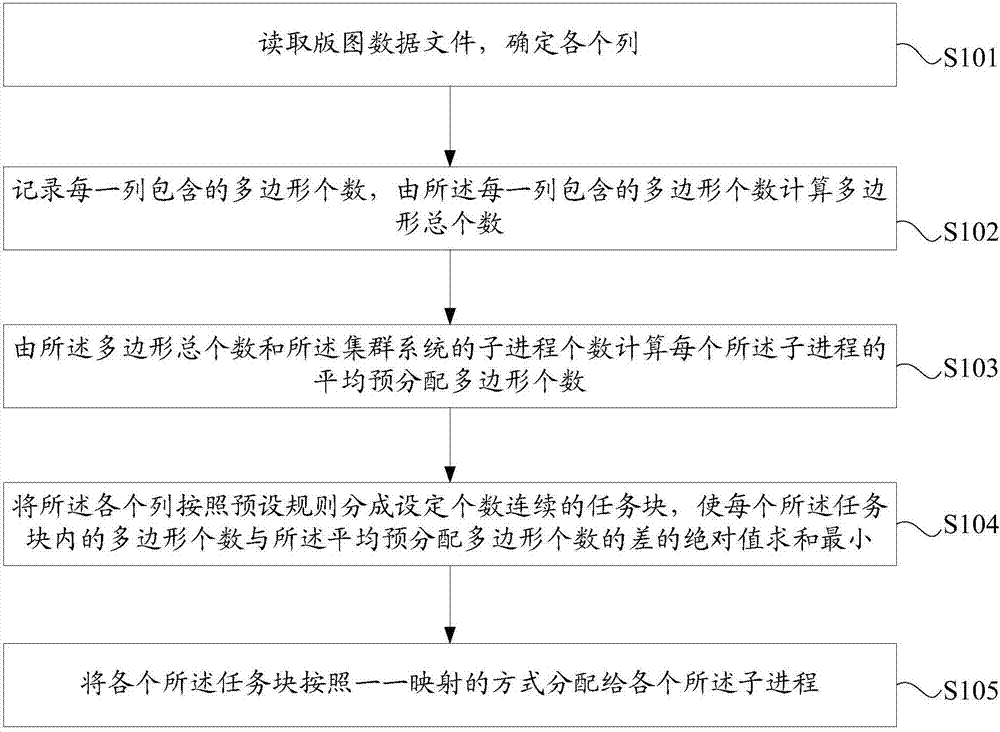

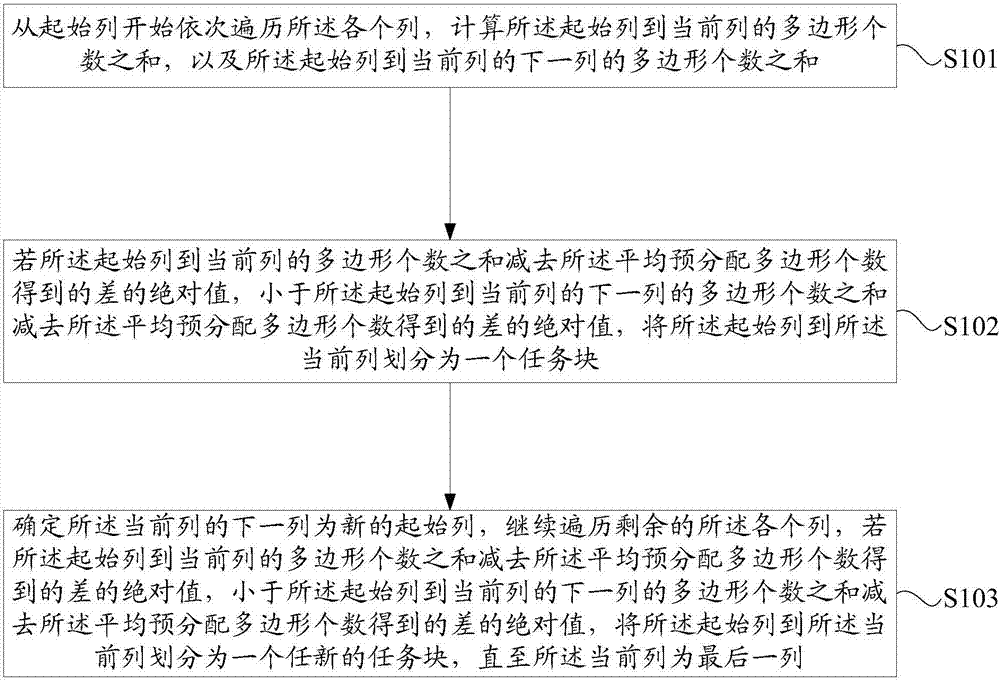

[0045] see figure 1 , figure 1 It is a flow chart of a method for allocating integrated circuit layout data processing tasks provided by an embodiment of the present invention. This method is applied to cluster systems such as figure 1 shown, including:

[0046] Step S101, read the layout data file, and determine each column;

[0047] Specifically, the layout data file is read row by row, and each column is determined.

[0048] Step S102, recording the number of polygons contained in each column, and calculating the total number of polygons from the number of polygons contained in each column;

[0049] Step S103, calculating the average number of pre-allocated polygons for each sub-process based on the total number of polygons and the number of sub-processes of the cluster system;

[0050] Specifically, divide the total number of polygons by the number of sub-processes to obtain the average number of pre-allocated polygons for each sub-process. Optionally, if the quotien...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com