Sorting method suitable for FPGA implementation

A sorting method and a suitable technology, applied in the field of heap sorting, can solve the problems of large data volume sorting time consumption, unable to meet real-time requirements, etc., to achieve the effect of facilitating data access, reducing sorting time complexity, and reducing delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will be described below in conjunction with the accompanying drawings.

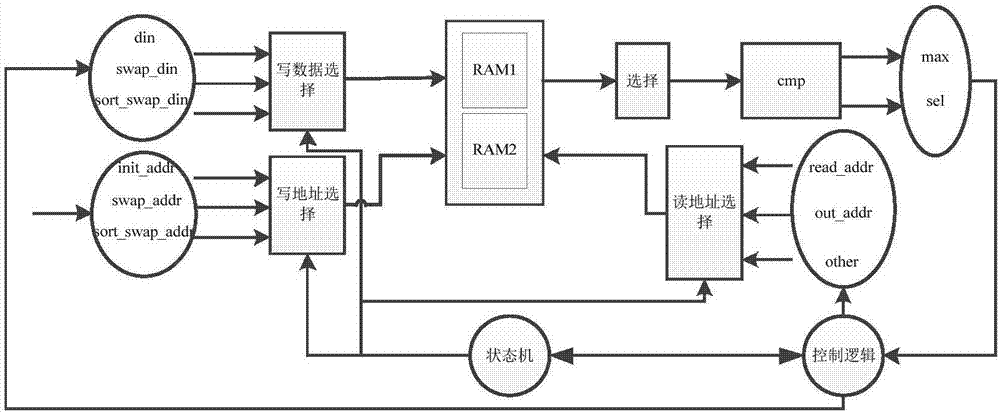

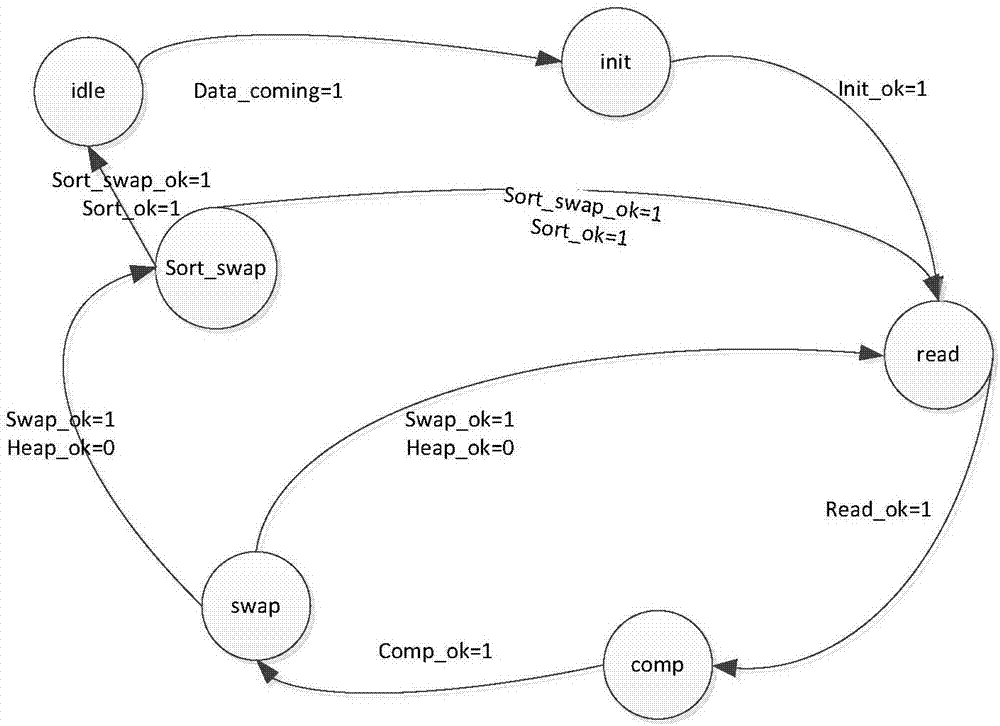

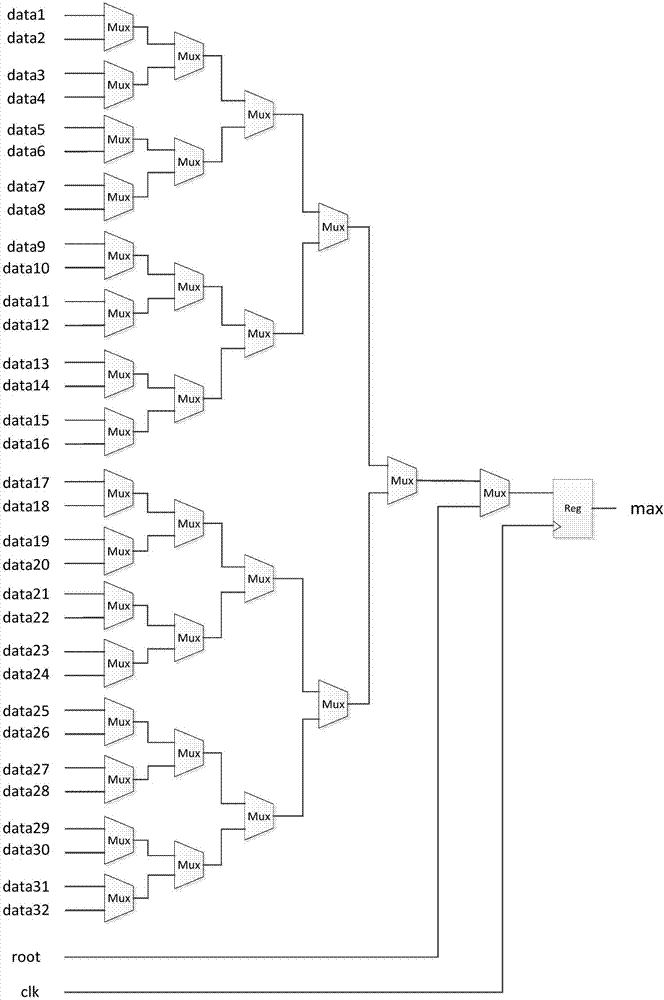

[0023] In this embodiment, the ISE integrated development tool and the modelsim simulation platform are used for running experiments. The simulation parameters are: the sequence length n=128, the element number of the tree is 32, namely k=5, and the data bit width is 16. Two dual-port RAMs with a depth of 128 are used to store the data to be sorted, which are used to read non-leaf nodes and child nodes of non-leaf nodes respectively, reducing data reading time. The write bit width of both RAM1 and RAM2 is 16, and the read bit width of RAM1 is 512. One clock can read 32 data, and all child nodes of non-leaf nodes can be read at one time. The output bit width of RAM2 is 16. Use For reading non-leaf nodes, the address of reading non-leaf nodes in RAM2 is the same as the address of child nodes of non-leaf nodes in RAM1. attached figure 1 is the structural block diagram of the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More