Scheduler device and method for dynamic loop-to-processor mapping

A technology for scheduling equipment and number of cycles, applied in the field of multi-parallel computing, can solve problems such as infeasibility and high computing time, achieve the effect of minimum power consumption limit, solve optimization problems, and reduce user workload

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062] In the drawings, the same reference symbols denote the same or equivalent elements. Additionally, it should be noted that not all figures are drawn to scale.

[0063] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the drawings in the embodiments of the present invention.

[0064] Apparently, the described embodiments are only some embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts fall within the protection scope of the present invention.

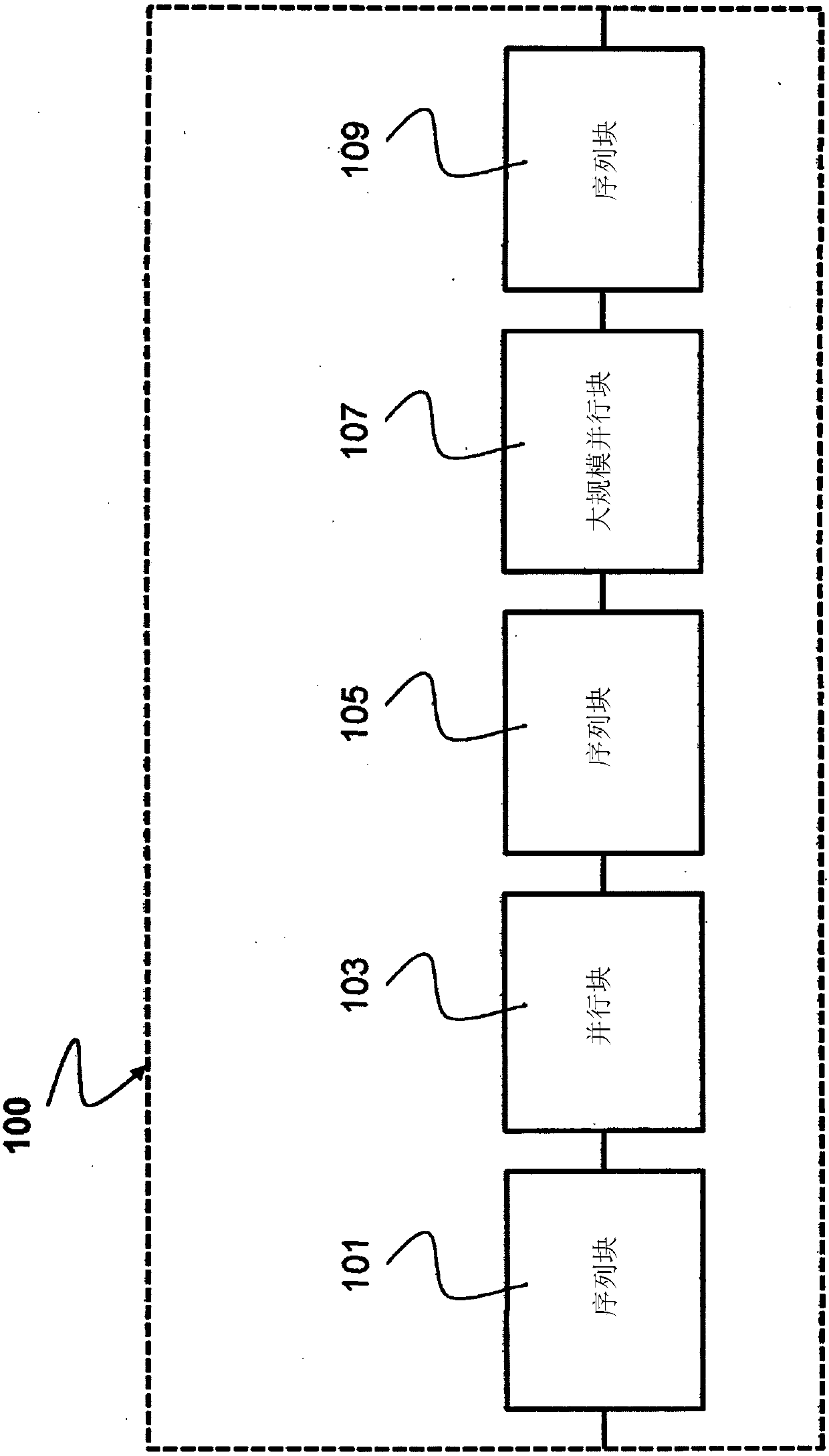

[0065] figure 1 An example of a conventional program structure is shown.

[0066] Each program may consist of a series of blocks 101, 103, 105, 107, 109, such as figure 1 shown in . The first block 101 and the last block 109 are sequential blocks, but all other intermediate blocks 103,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More