Insulated gate bipolar transistor

A bipolar transistor and insulated gate technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of increasing turn-on energy consumption and large Miller capacitance, and achieve the effect of reducing Miller capacitance and turn-on energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

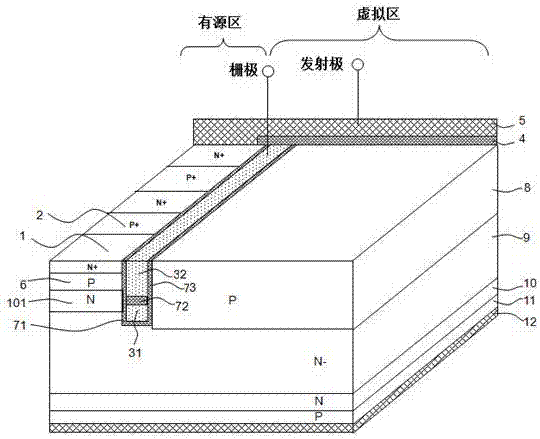

[0026] The structure of an insulated gate bipolar transistor of the present invention is as follows figure 2 As shown, including metal collector 12, P-type collector 11, N-type field stop layer 10 and N-drift region 9 on the back, the top of the transistor includes active original cell and dummy original cell, active original cell and dummy original cell Separated by trenches; the polysilicon filled in the trenches is separated into an upper polysilicon layer 32 and a lower polysilicon layer 31 by a dielectric layer 72, the upper polysilicon layer 32 and the oxide layer 73 on the upper part of the trench are in contact with each other, and the lower polysilicon layer 31 and the lower part of the trench are oxidized The layers 71 are in contact with each other; the upper polysilicon layer 32 is connected to the gate electrode, and the lower polysilicon layer 31 is connected to the emitter electrode; the active cell includes one or more N+ emitter regions 1 and a plurality of P+...

Embodiment 2

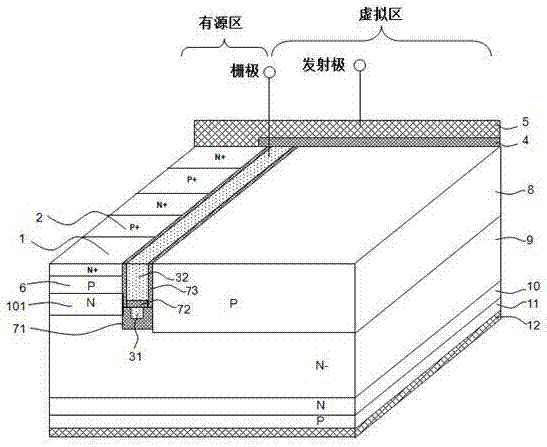

[0028] image 3 Shown is a modified structure of the present invention. Compared with the transistor structure of Embodiment 1, the thickness of the oxide layer 71 at the lower part of the trench is greater than the thickness of the oxide layer 73 at the upper part of the transistor in this embodiment. The advantage of this structure is that because the electric field at the bottom of the trench is relatively large, thickening the oxide layer at the bottom of the trench can enhance the reliability of the device.

[0029] The working principle of the present invention is as follows:

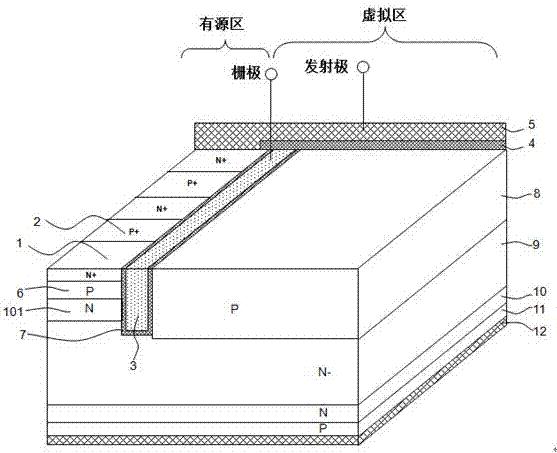

[0030] figure 1 In the structure shown, the polysilicon 3 inside the trench is connected to the gate electrode. The polysilicon 3 fills the entire trench, so the Miller capacitance caused by the polysilicon 3 is relatively large, which will adversely affect the performance of the device. For example, the voltage drop rate will be slower during the turn-on process, increasing the turn-on energy c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More