Chip package structure and package method

A chip packaging structure and chip packaging technology, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems of high preparation cost of lead frame structure, labor and time cost, unfavorable heat dissipation at the bottom of the chip, etc., to achieve the advantage of fixing Effects of connection, simplification of packaging process, and prevention of shifting or dropping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0056] This embodiment provides a chip packaging method, such as Figure 1-12 shown, including the following steps:

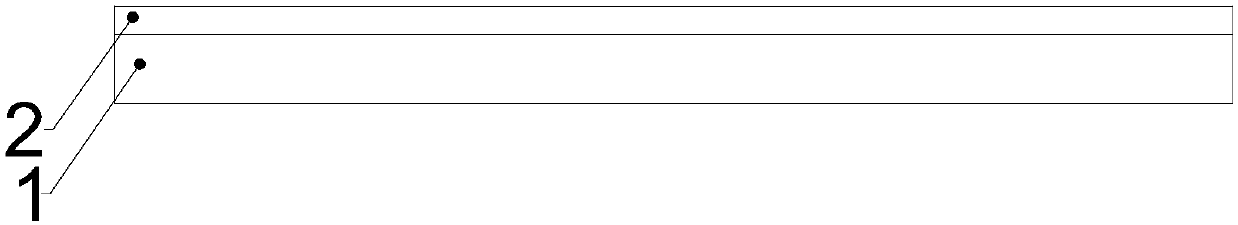

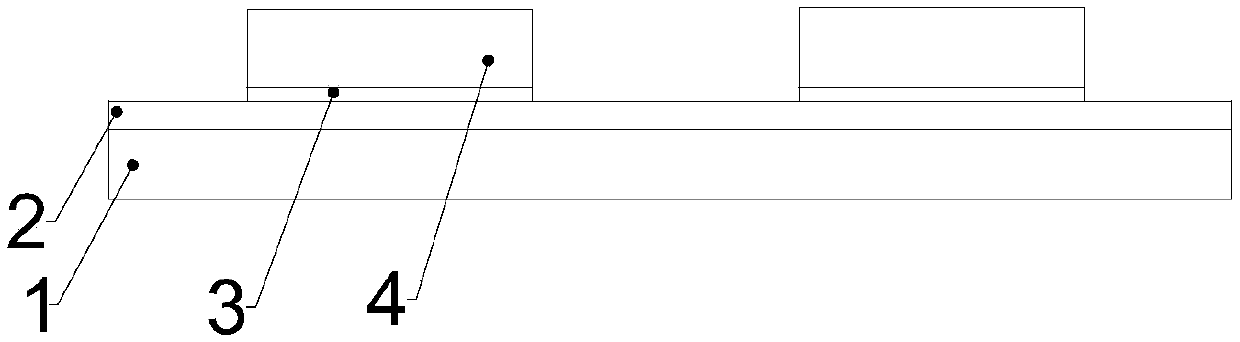

[0057] Step S1, providing a carrier 1, the carrier 1 is selected from but not limited to glass or stainless steel.

[0058] Step S2 , forming a first adhesive layer 2 on the carrier 1 , specifically, spin-coating a photosensitive temporary bonding glue, such as UV glue, etc. on the carrier 1 by spin coating. When the carrier board 1 is made of stainless steel, a heat-peelable film can also be provided on the carrier board 1 as the first adhesive layer 2; a second adhesive layer 3 is formed on the bottom of several chips 4 to be packaged. As an embodiment of the present invention, in this embodiment, specifically, a DAF adhesive film is provided on the bottom of the chip 4 to be packaged.

[0059] The formation of the first adhesive layer 2 and the second adhesive layer 3 is conducive to the fixed connection between the subsequent chip 4 and the carrier 1, pre...

Embodiment 2

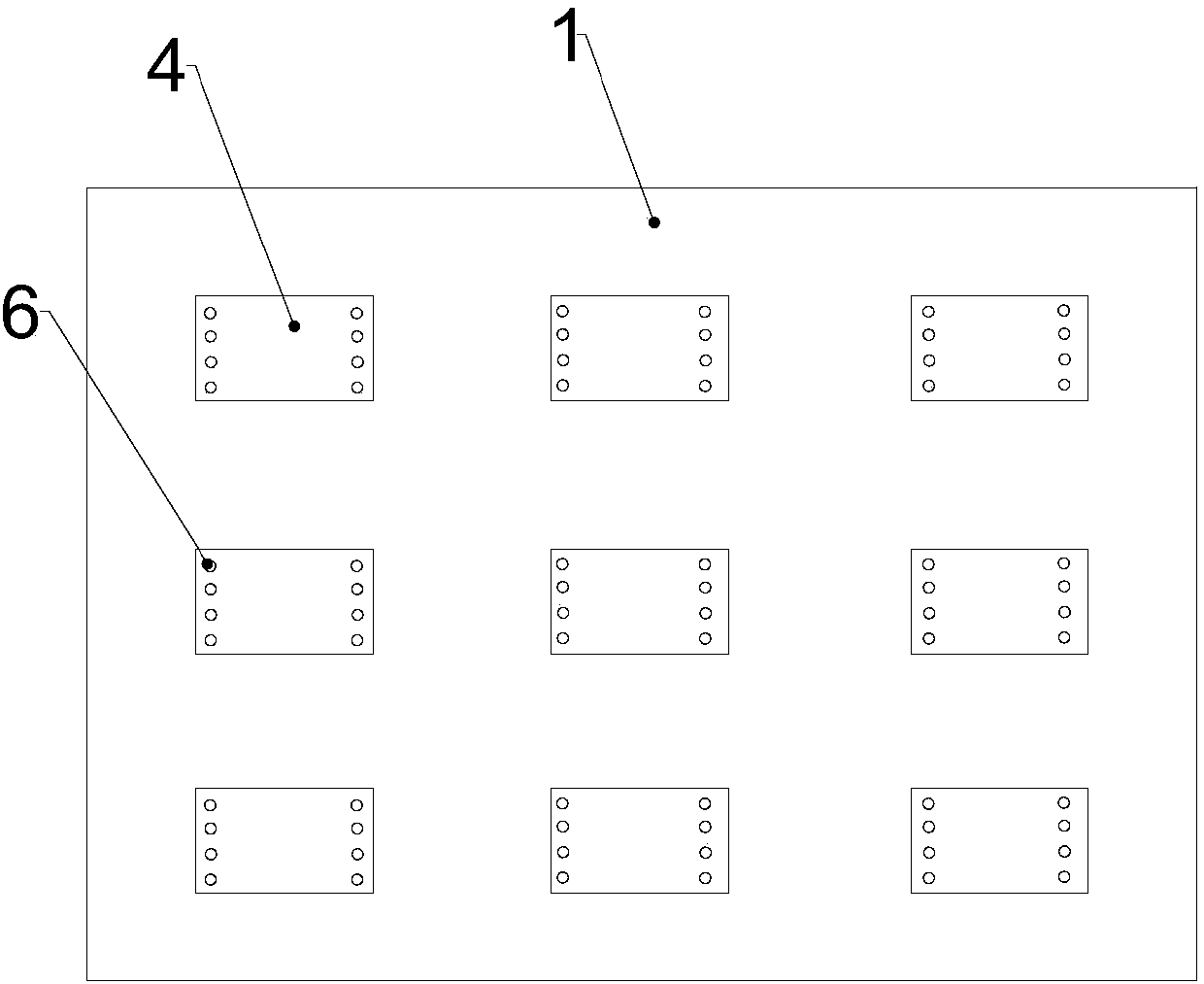

[0088] This embodiment provides a chip packaging structure, such as Figure 9 As shown, it includes a carrier board 1 , a connector 5 , a plastic package 7 and a conductive layer 9 .

[0089] The carrier 1 is used to place several chips 4, the carrier 1 is selected from but not limited to glass or stainless steel, and the chips 4 are arranged in a matrix and distributed on the carrier 1;

[0090] The connector 5 is used to connect adjacent chips 4, specifically, the connector 5 is a bonding wire, which can be a gold wire or a silver wire, and the connector 5 protrudes outward in an arched shape;

[0091] The plastic package 7 is used to wrap the chip 4 and the connector 5, and expose the top of the connector 5. The exposed area can be determined according to the actual situation, wherein the material of the plastic package 7 is powder resin or liquid resin;

[0092] The conductive layer 9 is used to cover the exposed area on the top of the connector 5 and also covers part of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More