Manufacturing method of grid insulation layer

A gate insulating layer and radio frequency power technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve the problems of removing trapped charges, difficulty, and charge capture on the surface of the gate insulating layer, achieving high reliability performance, high yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

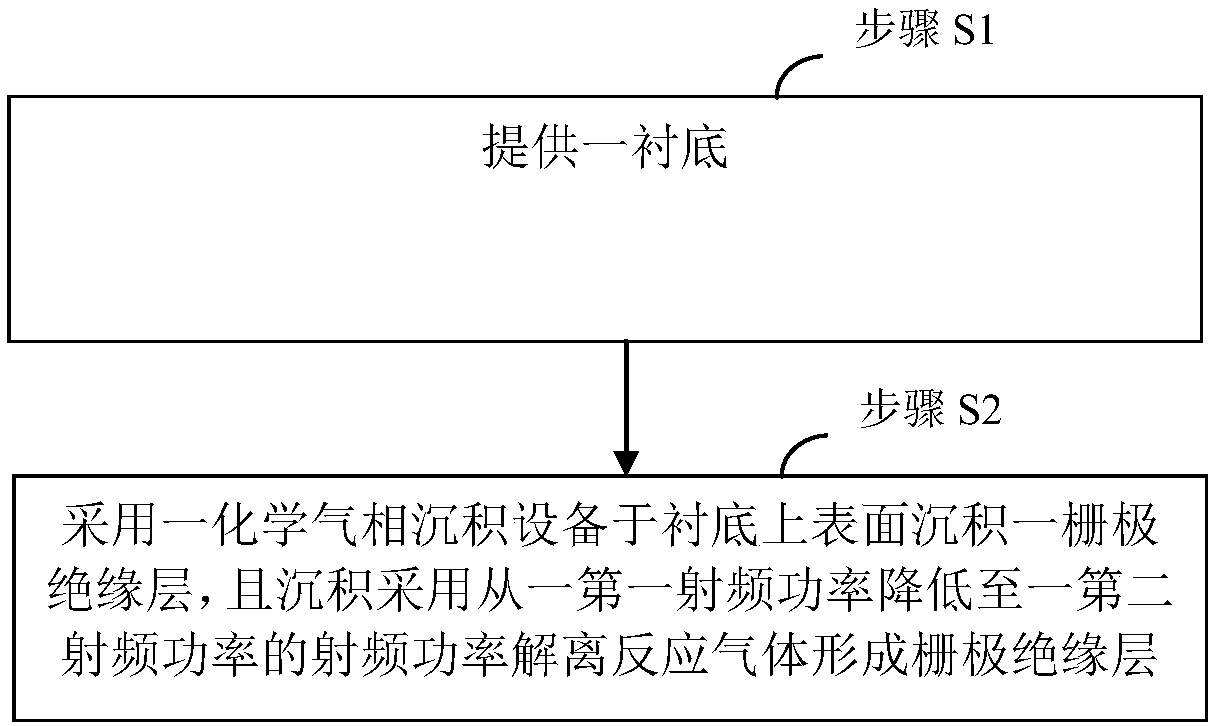

[0021] In a preferred embodiment, as figure 1 As shown, a method for preparing a gate insulating layer is proposed, which may include:

[0022] Step S1, providing a substrate;

[0023] Step S2, using a chemical vapor deposition apparatus to deposit a gate insulating layer on the upper surface of the substrate, and depositing the gate insulating layer by using a radio frequency power reduced from a first radio frequency power to a second radio frequency power to dissociate a reactive gas;

[0024] Wherein, the second radio frequency power is 0-50W (W).

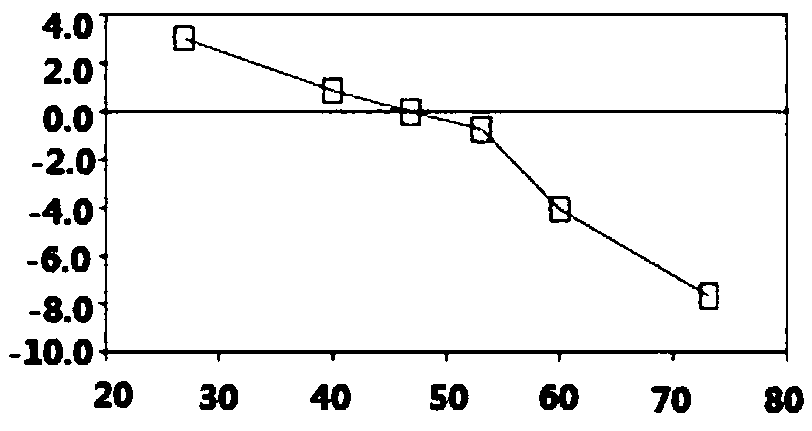

[0025] In the above technical solution, the second radio frequency power should be smaller than the first radio frequency power; the chemical vapor deposition equipment initially uses a higher first radio frequency power to dissociate the reaction gas to ensure the dissociation efficiency, and then gradually reduces to the second radio frequency power. The second RF power range is 0-50W, so there is no problem of charge trapp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com