Self-alignment dual composition method, semiconductor device and manufacturing method therefor, and electronic apparatus

A semiconductor, self-aligned technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical solid-state devices, etc., can solve problems such as load effects, and achieve good yield and performance, less dents, and consistent pattern density.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

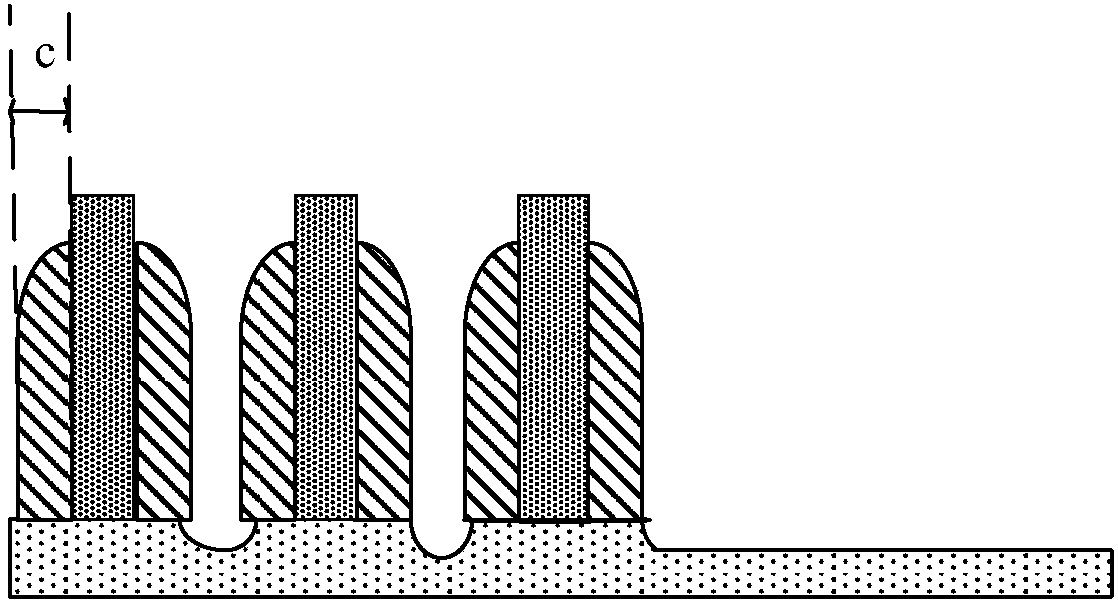

[0042] The following will refer to Figure 4A ~ Figure 4I A method for fabricating a semiconductor device according to an embodiment of the present invention will be described in detail.

[0043] First, if Figure 4A As shown, a semiconductor substrate 400 is provided. The semiconductor substrate 400 includes a storage region 400A and a peripheral region 400B. A gate stack is formed on the storage region 400A and a peripheral region 400B. The gate stack includes a tunneling Oxide layer (not shown), floating gate material layer 401, gate dielectric layer 402 and control gate material layer 403, a first hard mask layer 404, a second hard mask layer are formed on the gate stack layer 405 and patterned sacrificial layer 406.

[0044] Wherein, the semiconductor substrate 400 can be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP or other III / V compound semiconductors, and also includes multiple semiconductors composed of these semiconducto...

Embodiment 2

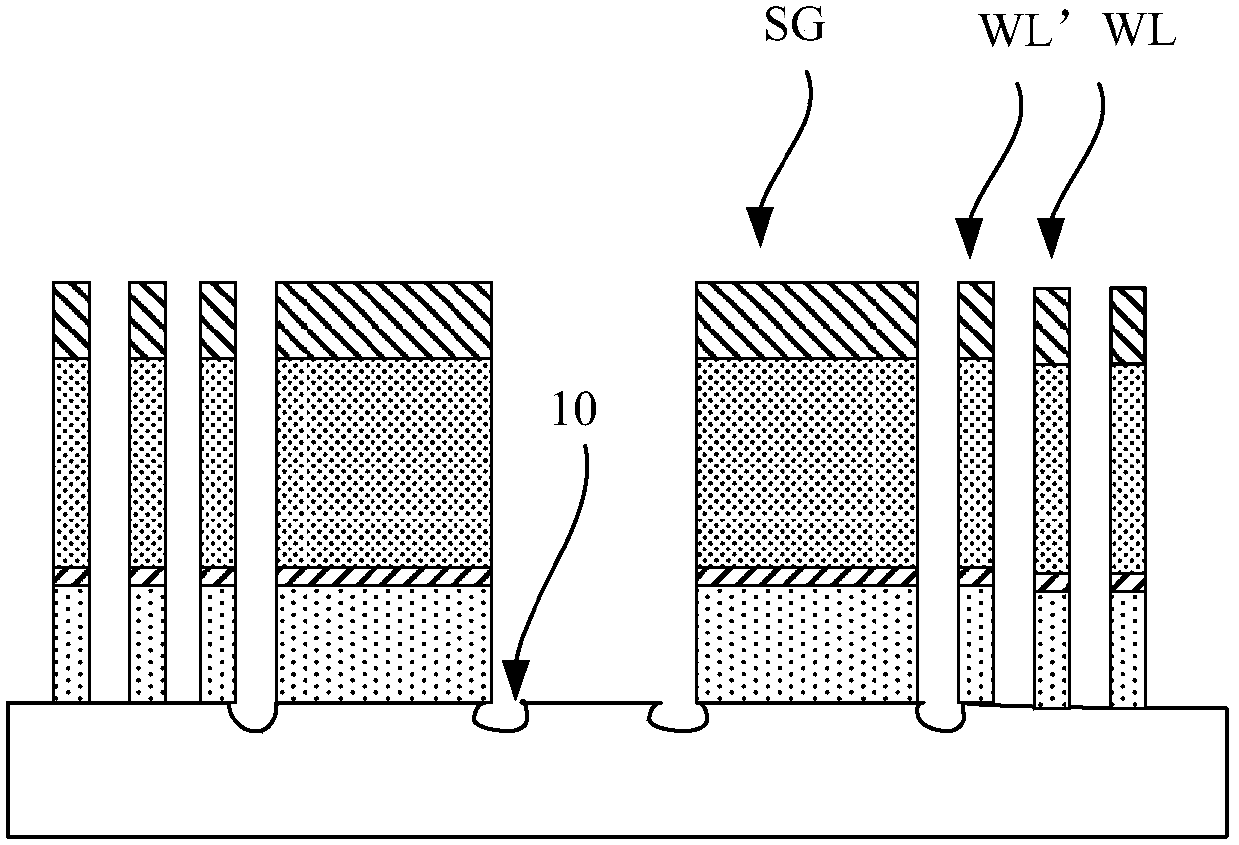

[0079] The present invention also provides a semiconductor device fabricated by the above method, such as Figure 5 As shown, the semiconductor device includes: a semiconductor substrate 500, the semiconductor substrate 500 includes a storage area 500A and a peripheral area 500B, a word line WL and a selection gate SG are formed on the storage area 500A, and in the peripheral area 500B is formed with a logic gate Gate, a source and a drain, wherein the word line includes a word line WL for programming and a dummy word line WL' adjacent to the selection gate SG, and the word line for programming The spacing between WL is the same as the spacing between the dummy word line WL' and the select gate SG.

[0080] Wherein the semiconductor substrate 500 can be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP or other III / V compound semiconductors, and also includes multilayers composed of these semiconductors The structure or the like may be s...

Embodiment 3

[0085] Still another embodiment of the present invention provides an electronic device, including a semiconductor device and an electronic component connected to the semiconductor device. Wherein, the semiconductor device includes: a semiconductor substrate, the semiconductor substrate includes a storage area and a peripheral area, a word line and a selection gate are formed on the storage area, a logic gate, a source electrode are formed on the peripheral area and a drain, wherein the word lines include a word line for programming and a dummy word line adjacent to the select gate, and the spacing between the word lines for programming is the same as that of the dummy word line and the select gate. The spacing between the grids is the same.

[0086] The semiconductor substrate can be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP or other III / V compound semiconductors, including multilayer structures composed of these semiconductors e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More