Dual-side SiP three-dimensional package structure

A three-dimensional packaging and packaging structure technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of difficult balance of various materials, complex packaging, warping deformation, etc., to reduce chip loss and improve high frequency. The effect of performance, high yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

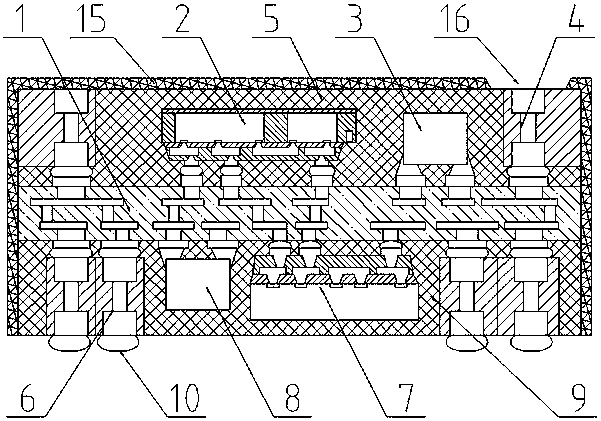

[0039] see figure 1 , a double-sided SiP three-dimensional packaging structure in this embodiment, which includes a core interposer 1, and the front side of the core interposer 1 is mounted with a fan-out wafer-level packaging structure 2 and a first passive component 3 , the fan-out wafer level packaging structure 2 and the first passive element 3 are provided with a first 3D conductive component 4, and the fan-out wafer level packaging structure 2, the first passive element 3 and the first 3D conductive The component 4 is encapsulated with a first molding compound 5, the front of the first 3D conductive component 4 is exposed to the first molding compound 5, and a chip 7 and a second passive component 8 are mounted on the back of the core adapter board 1, and the chip 7 A second 3D conductive component 6 is arranged on the periphery of the second passive component 8, and the chip 7, the second passive component 8 and the second 3D conductive component 6 are encapsulated with...

Embodiment 2

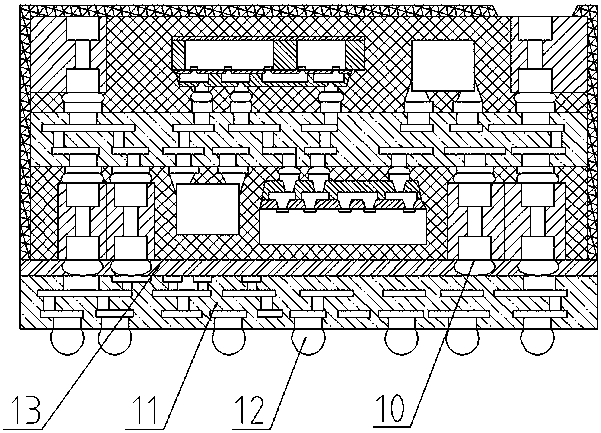

[0043] see figure 2 , the difference between embodiment 2 and embodiment 1 is: a first substrate 11 is arranged under the package structure, the package structure is connected to the front of the first substrate 11 through the first metal ball 10, and the back of the first substrate 11 Second solder balls 12 are provided, and underfill glue 13 is provided between the packaging structure and the first substrate 11 .

Embodiment 3

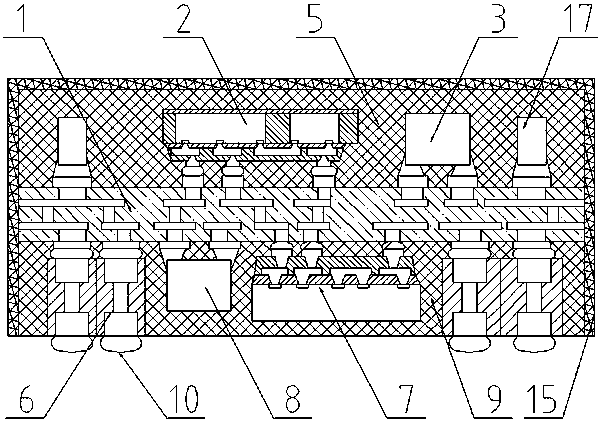

[0045] join image 3 , a double-sided SiP three-dimensional packaging structure in this embodiment, which includes a core interposer 1, and the front side of the core interposer 1 is mounted with a fan-out wafer-level packaging structure 2 and a first passive component 3 , the fan-out wafer level packaging structure 2 and the first passive element 3 are provided with metal bumps 17 on the periphery, and the fan-out wafer level packaging structure 2, the first passive element 3 and the metal bump 17 are encapsulated There is a first molding compound 5, a chip 7 and a second passive component 8 are mounted on the back of the core interposer 1, and a second 3D conductive component 6 is arranged on the periphery of the chip 7 and the second passive component 8, and the chip 7. The second passive element 8 and the second 3D conductive component 6 are encapsulated with a second molding compound 9, the back of the second 3D conductive component 6 is provided with first solder balls 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More