LDMOS (Lateral Diffusion MOS) structure

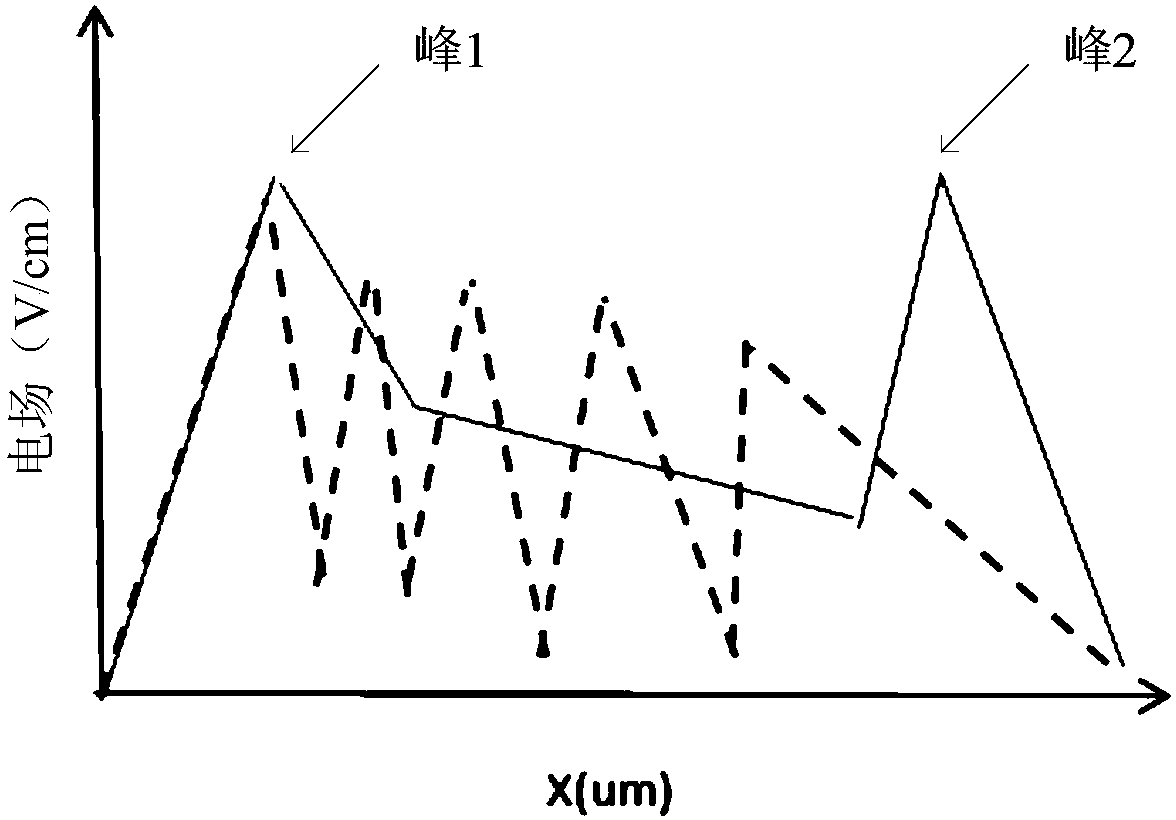

A transistor and isolation structure technology, applied in the field of LDMOS transistor structure, can solve problems such as avalanche breakdown of LDMOS structure, achieve the effects of reducing impact ionization, high breakdown voltage and saturation leakage current, and controlling production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

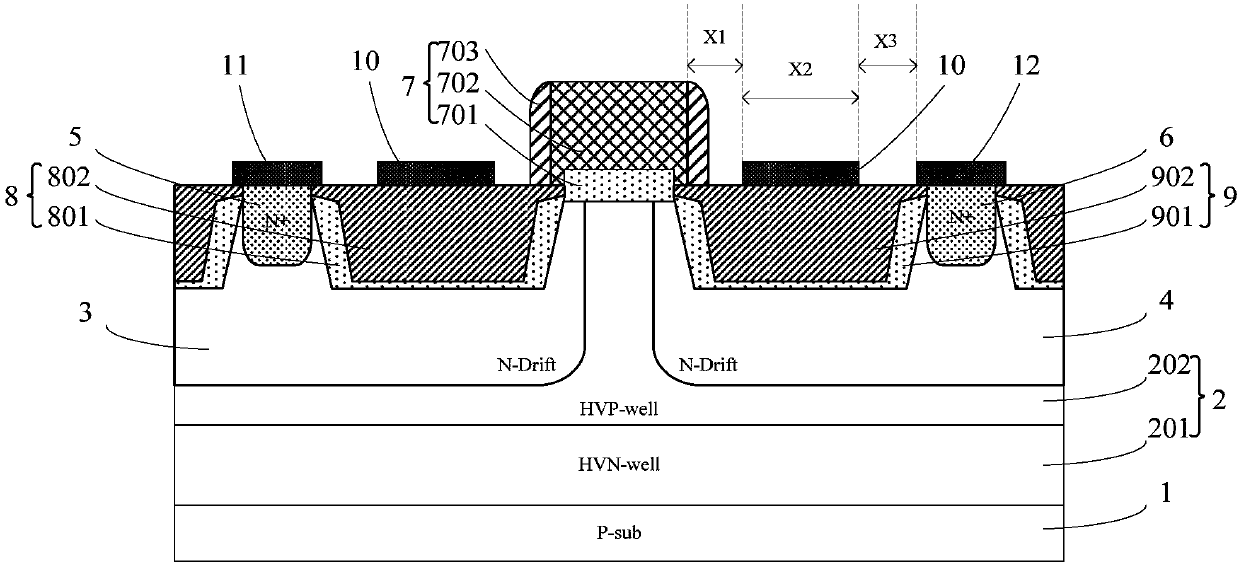

[0053] The present invention provides a LDMOS transistor structure, please refer to figure 1 , Shown as a schematic cross-sectional structure diagram of the LDMOS transistor structure, including:

[0054] Semiconductor substrate 1;

[0055] A first drift region 3 and a second drift region 4 located in the semiconductor substrate 1 and arranged separately;

[0056] A source 5 located in the first drift region 3 and a drain 6 located in the second drift region 4;

[0057] A gate structure 7 located on the semiconductor substrate 1 and contacting the first drift region 3 and the second drift region 4 on both sides;

[0058] A first isolation structure 8 located in the first drift region 3 and separating the source electrode 5 from the gate structure 7; located in the second drift region 4 and separating the drain electrode 6 from the gate structure 7 The second isolation structure 9 isolated by the gate structure 7; wherein:

[0059] A floating field plate 10 is provided on the first isol...

Embodiment 2

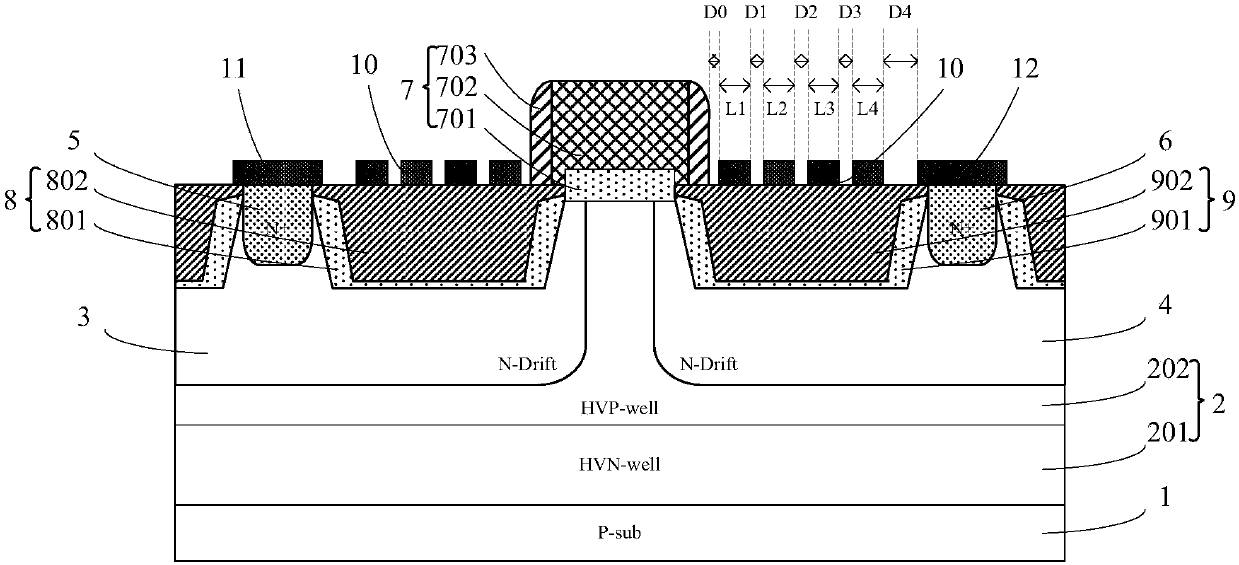

[0077] The difference between this embodiment and the first embodiment is that in the first embodiment, the first isolation structure 8 and the second isolation structure 9 are each provided with a floating field plate 10. In this embodiment, the first isolation structure and the second isolation structure are each provided with a plurality of discrete floating field plates.

[0078] See figure 2 , Showing a schematic cross-sectional structure diagram of the LDMOS transistor structure in this embodiment, including:

[0079] Semiconductor substrate 1;

[0080] A first drift region 3 and a second drift region 4 located in the semiconductor substrate 1 and arranged separately;

[0081] A source 5 located in the first drift region 3 and a drain 6 located in the second drift region 4;

[0082] A gate structure 7 located on the semiconductor substrate 1 and contacting the first drift region 3 and the second drift region 4 on both sides;

[0083] A first isolation structure 8 located in the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More