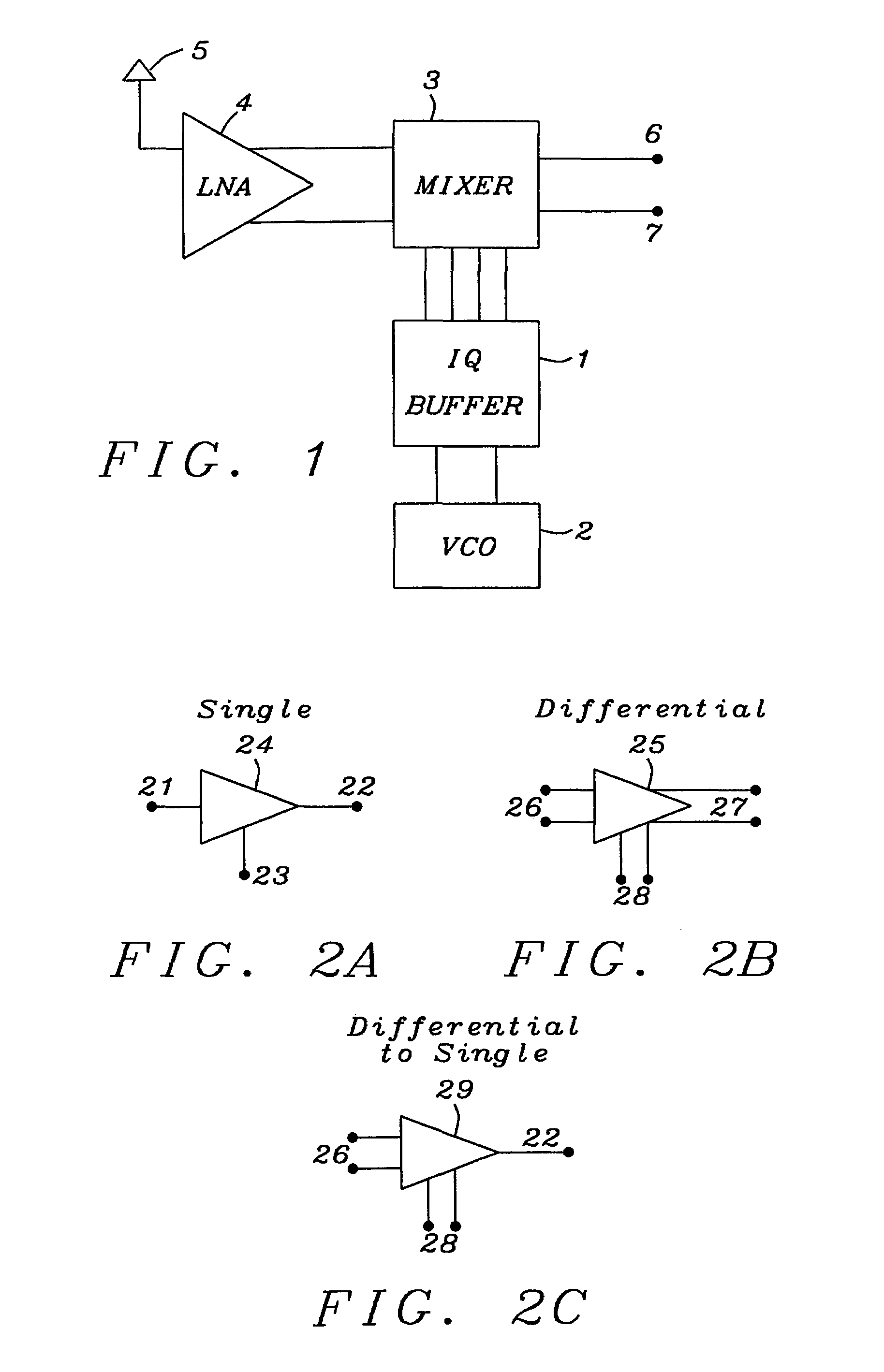

Patents

Literature

90 results about "Gate source capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

There is always capacitance between drain and gate which can be a real problem. A common MOSFET is the FQP30N06L (60V LOGIC N-Channel MOSFET). The Miller capacitance is the reverse transfer capacitance listed above and the input capacitance is the gate-source capacitance. Output capacitance is from drain to source.

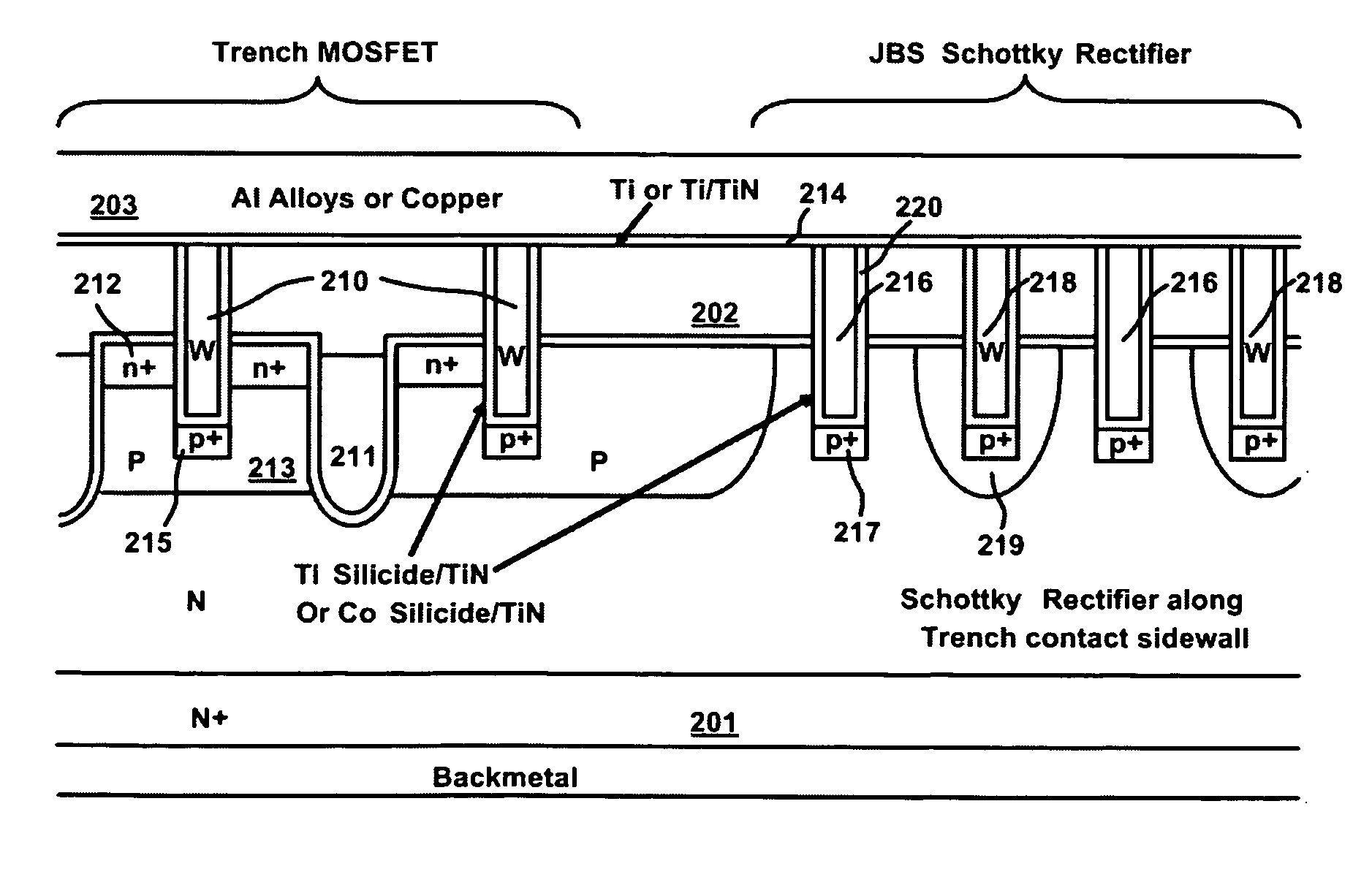

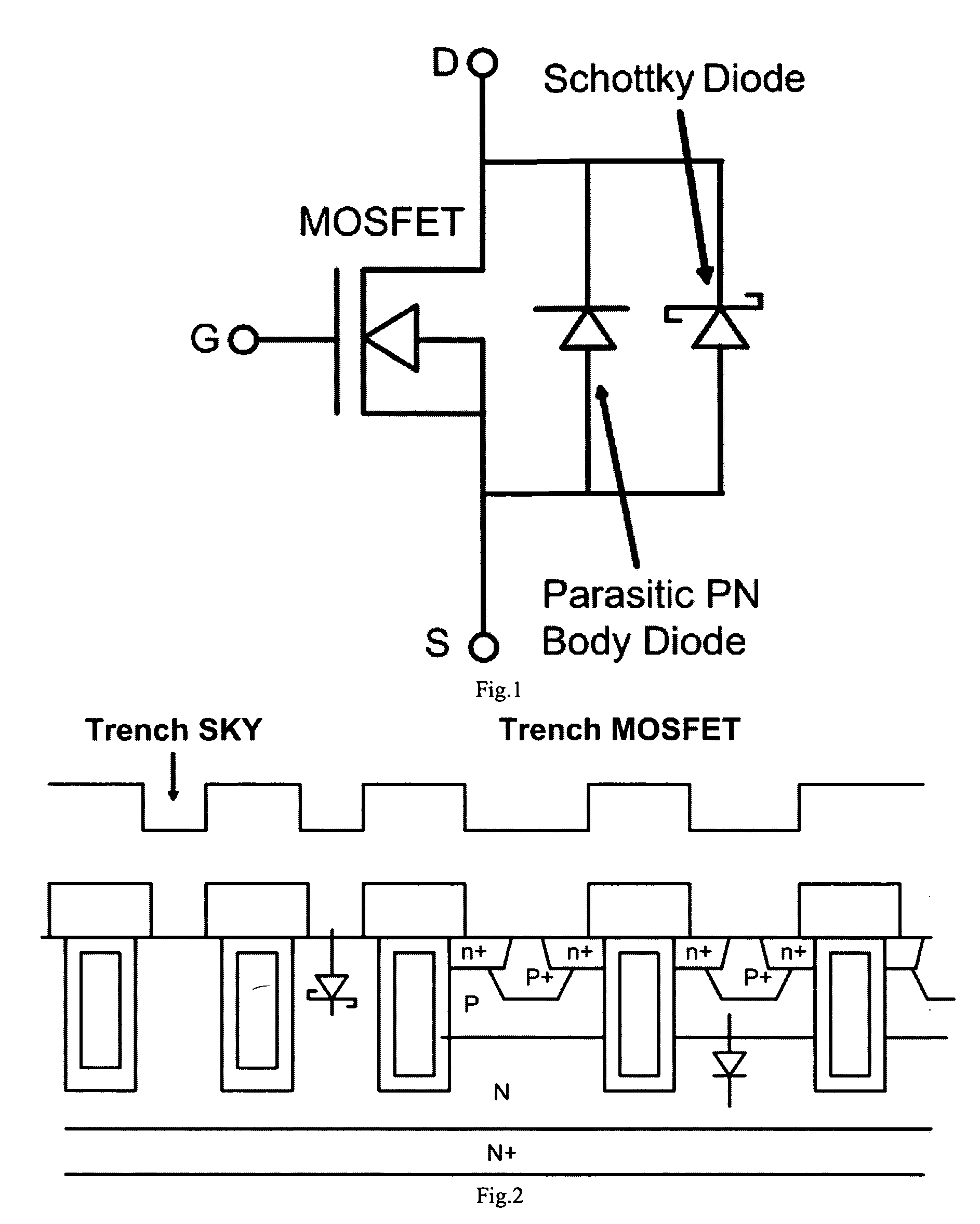

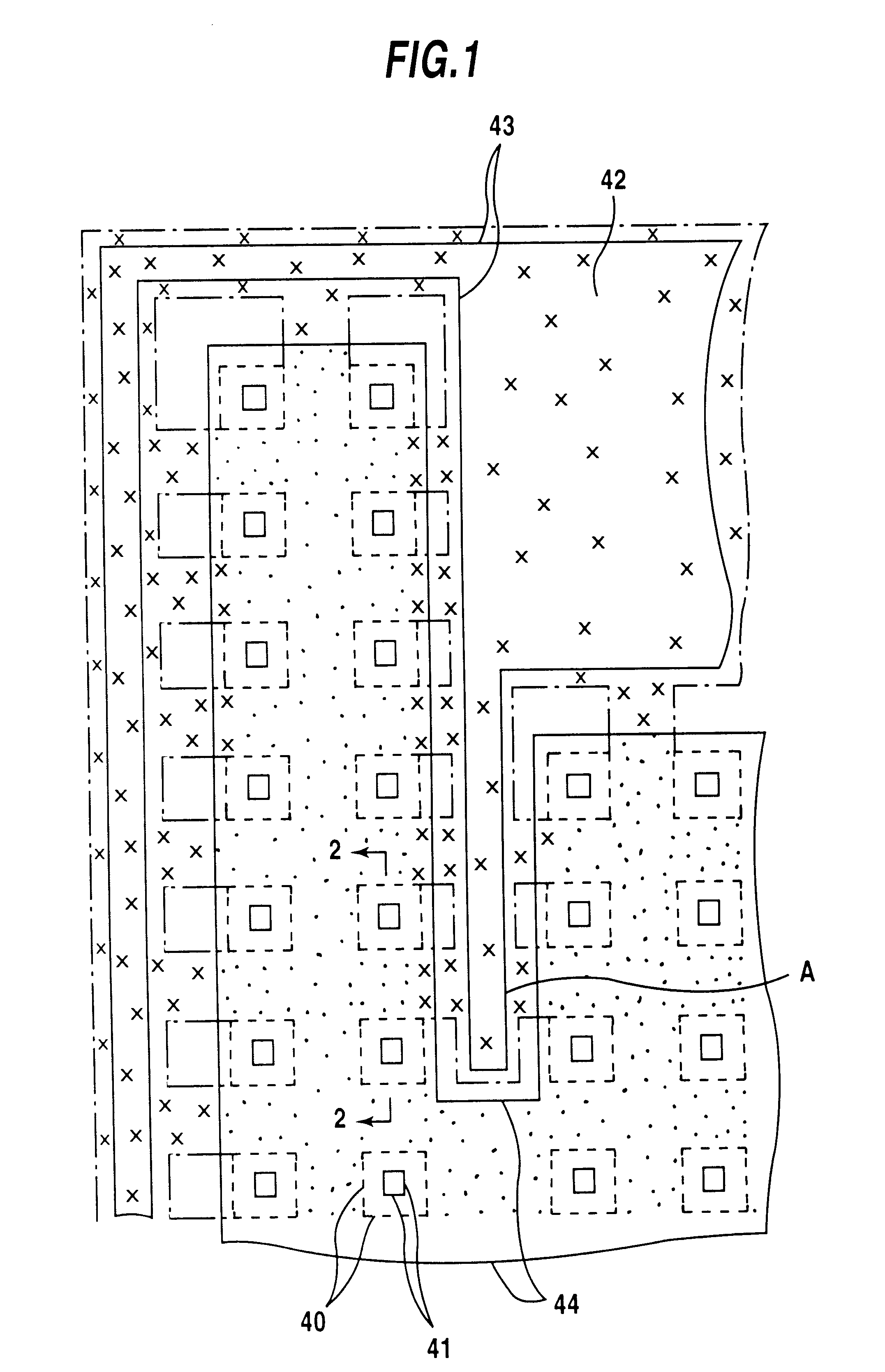

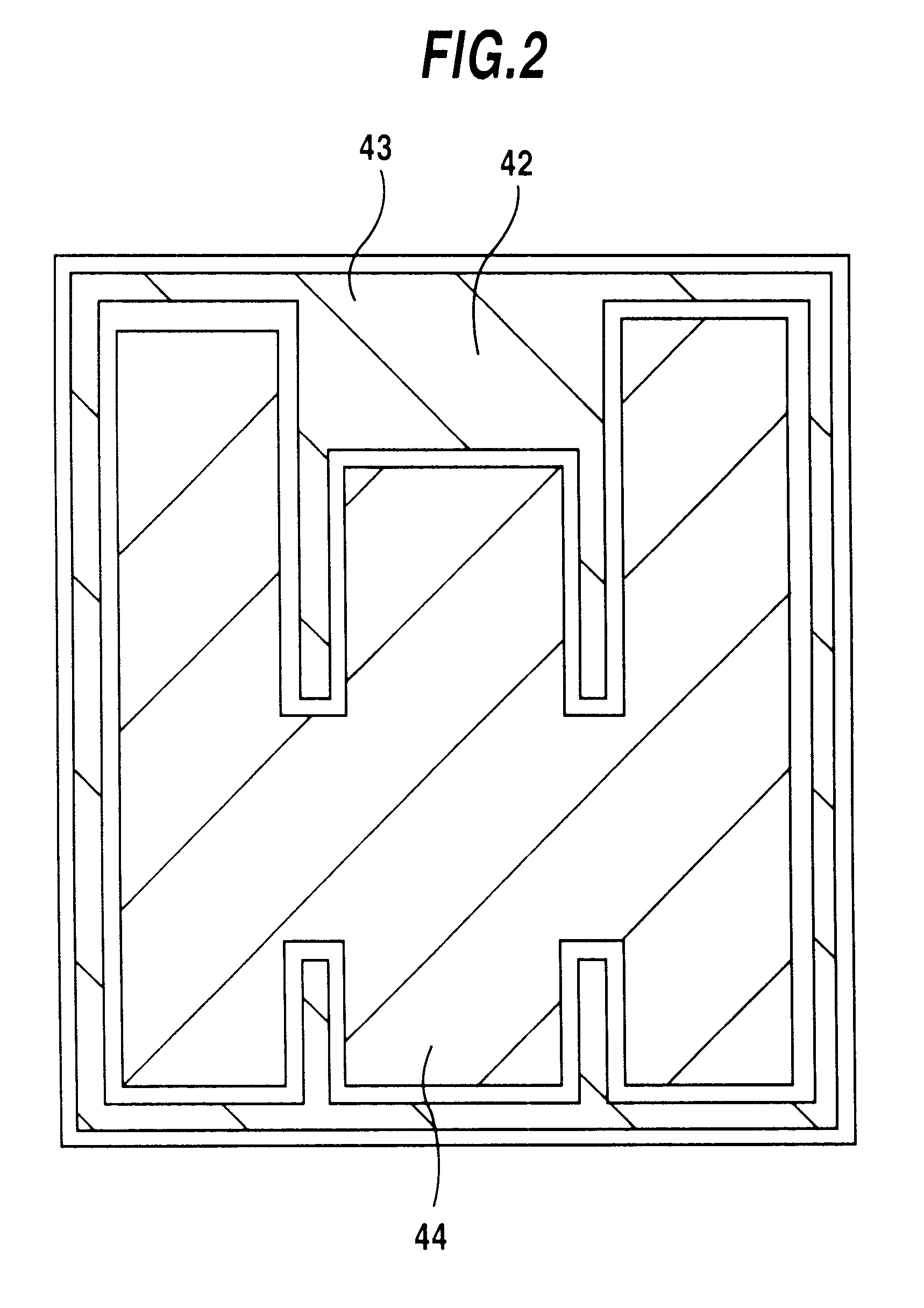

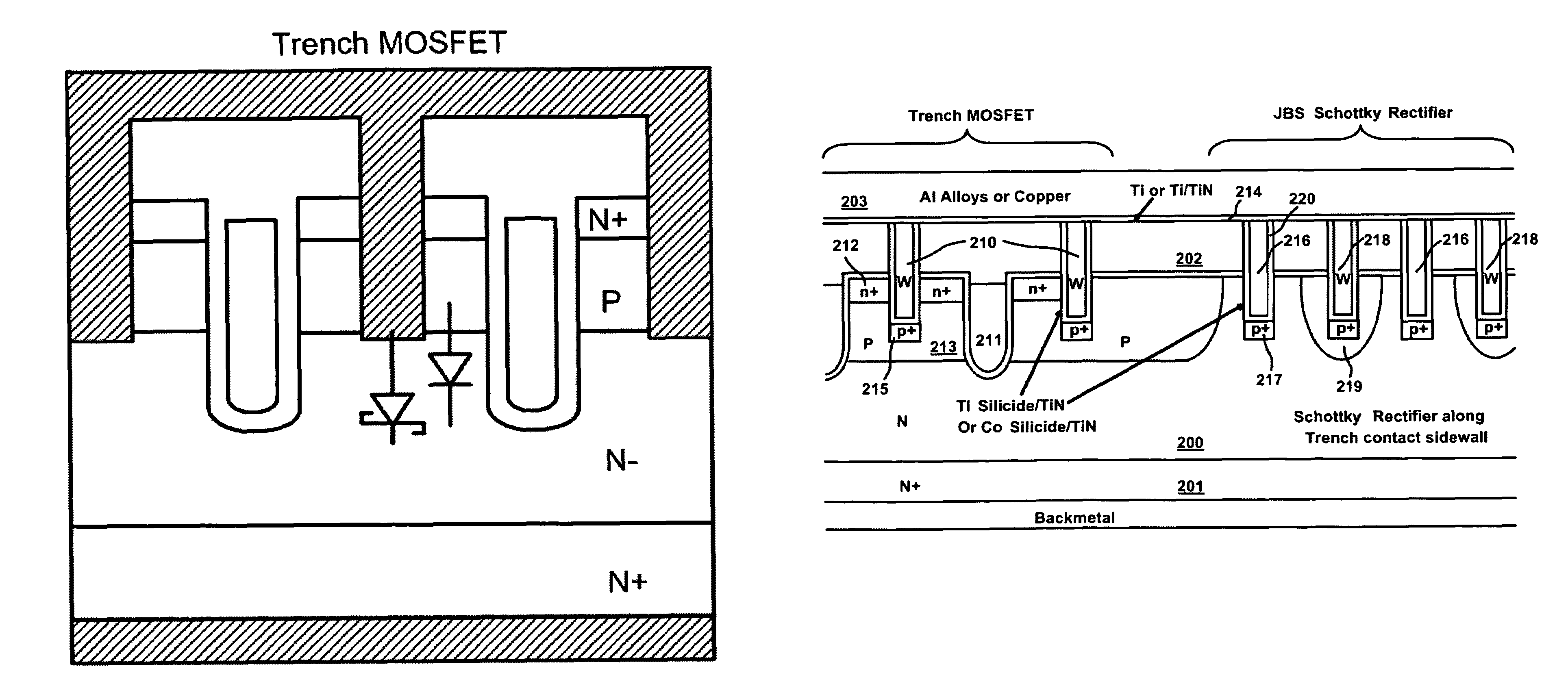

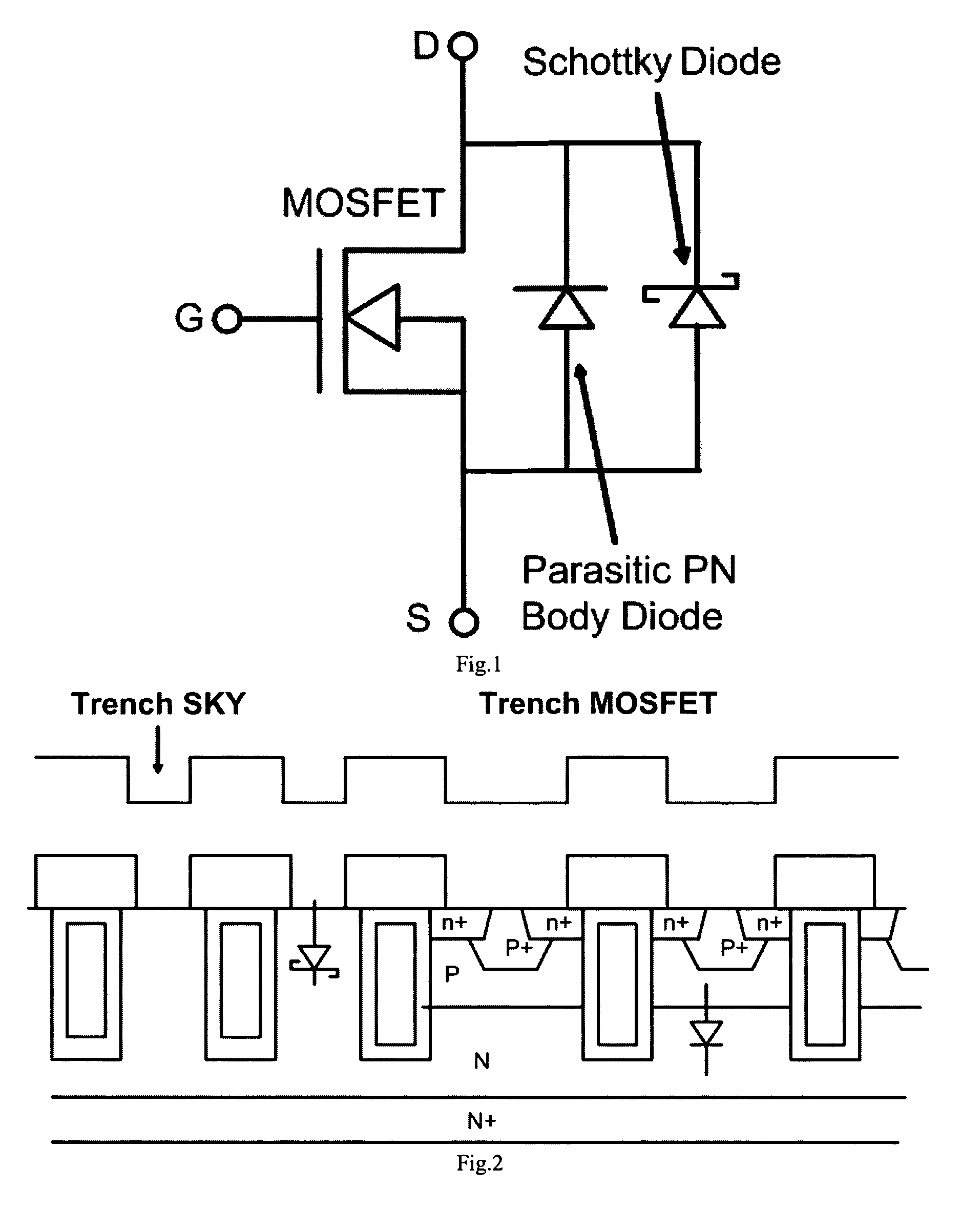

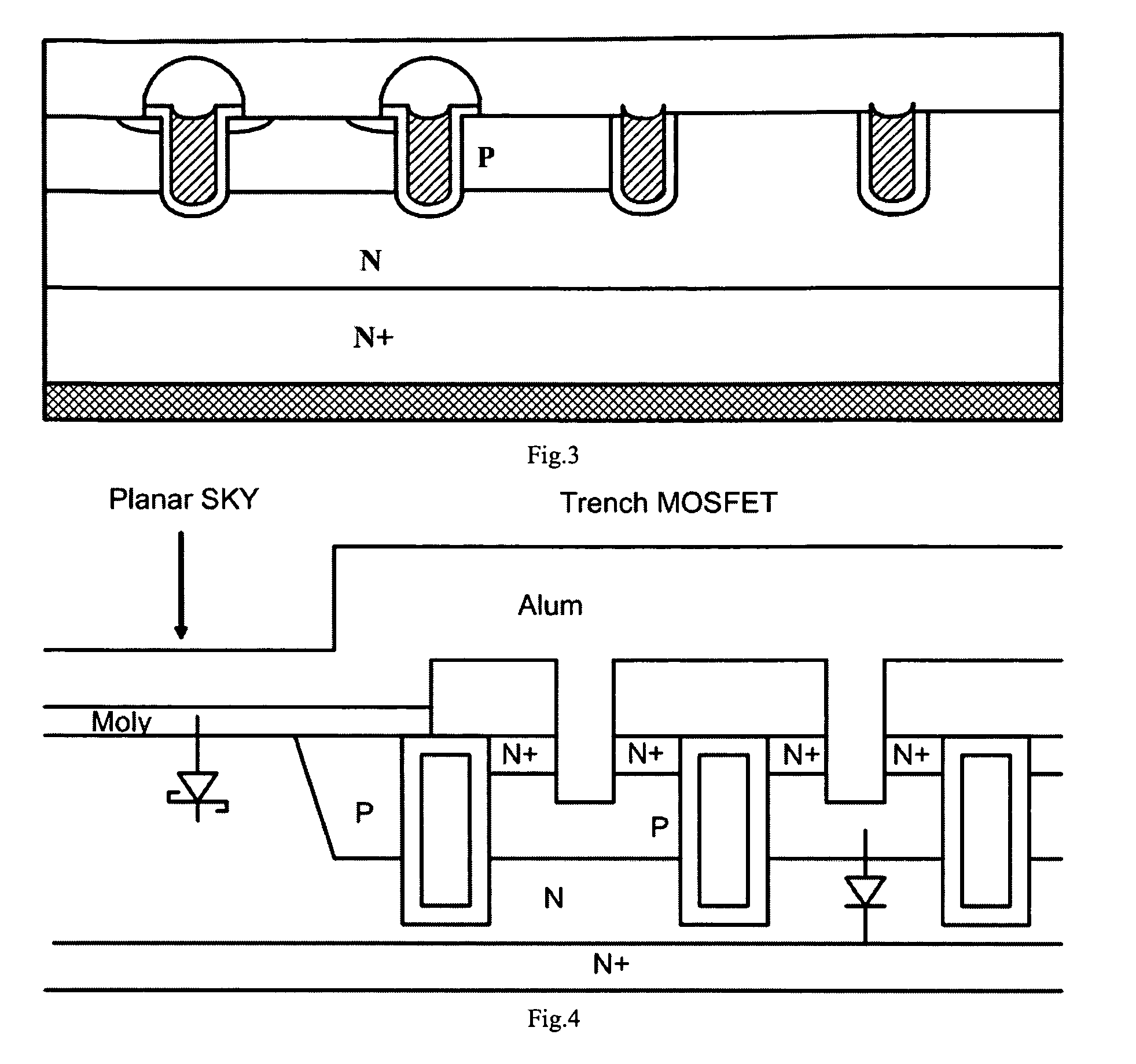

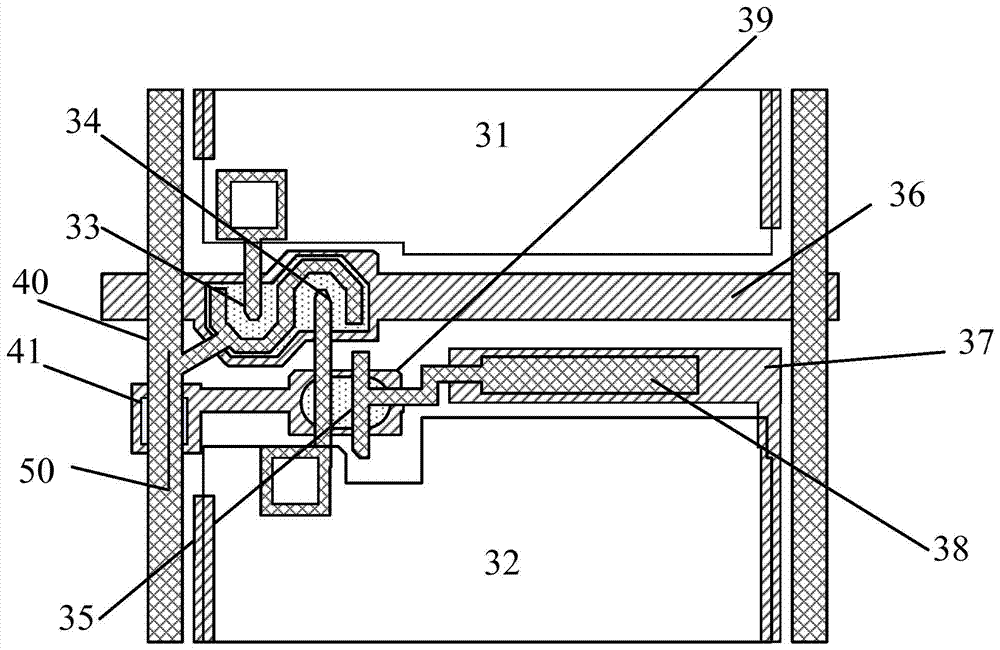

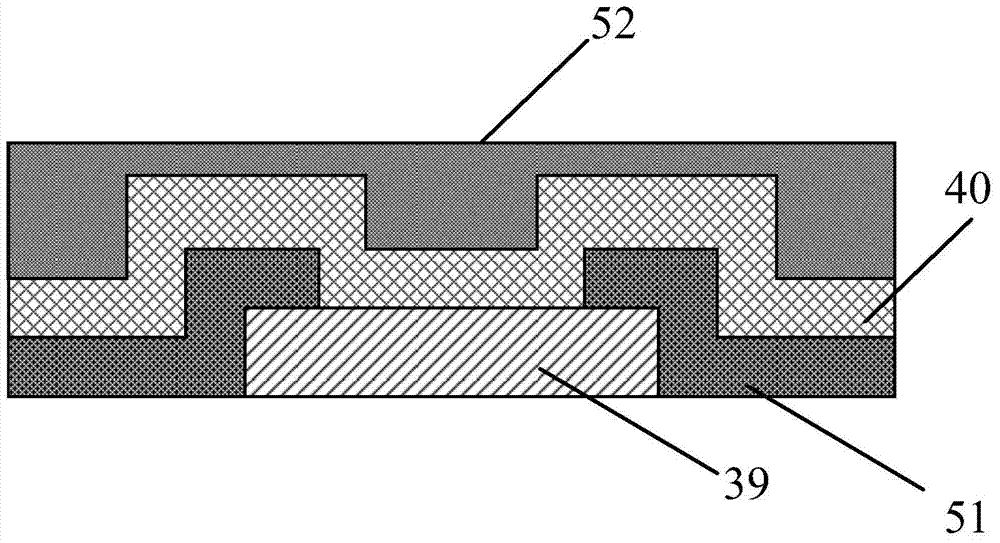

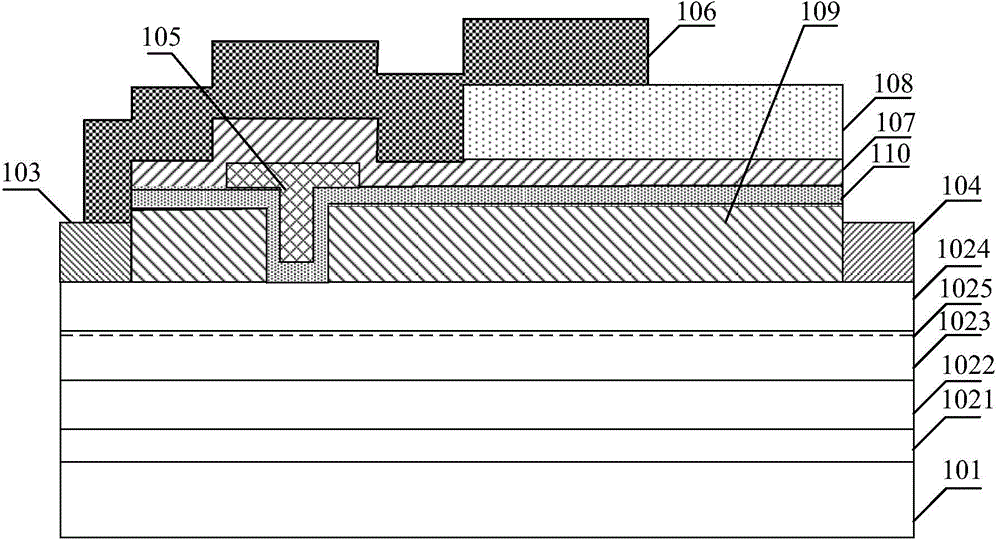

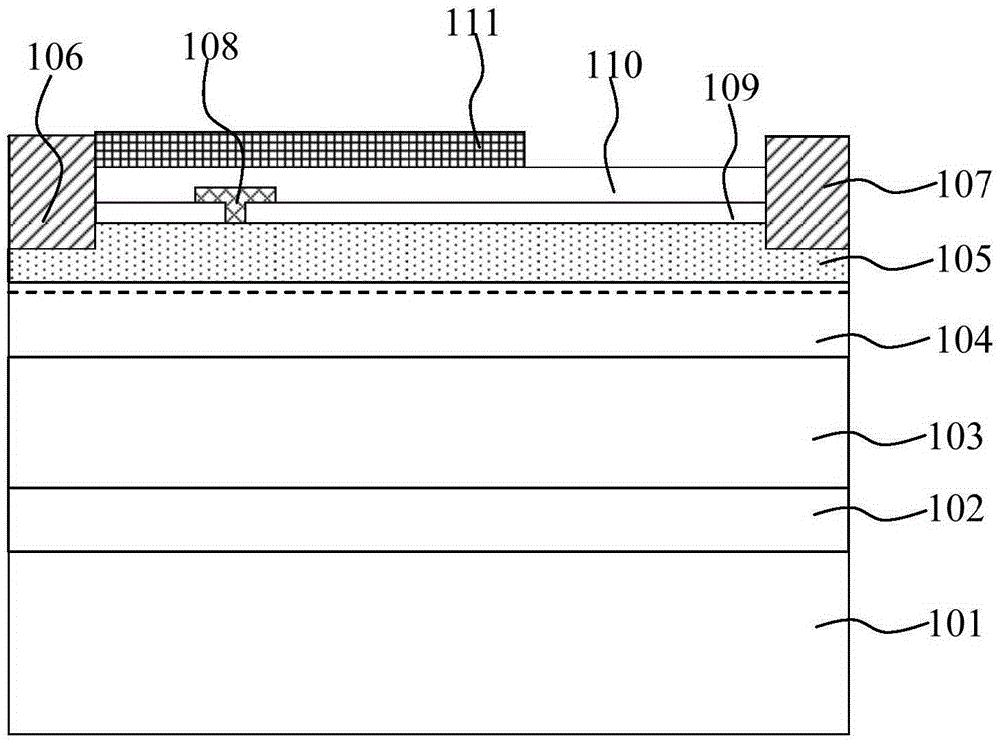

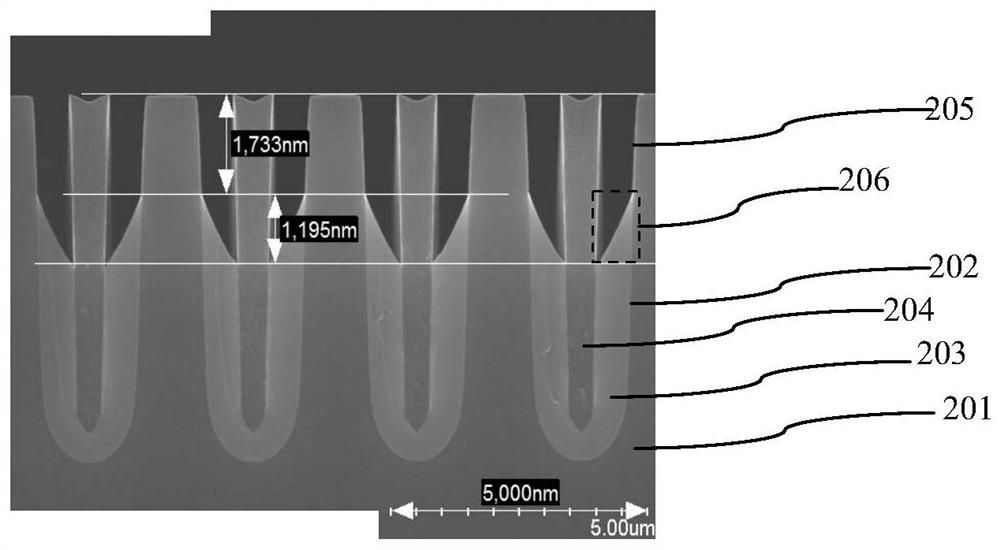

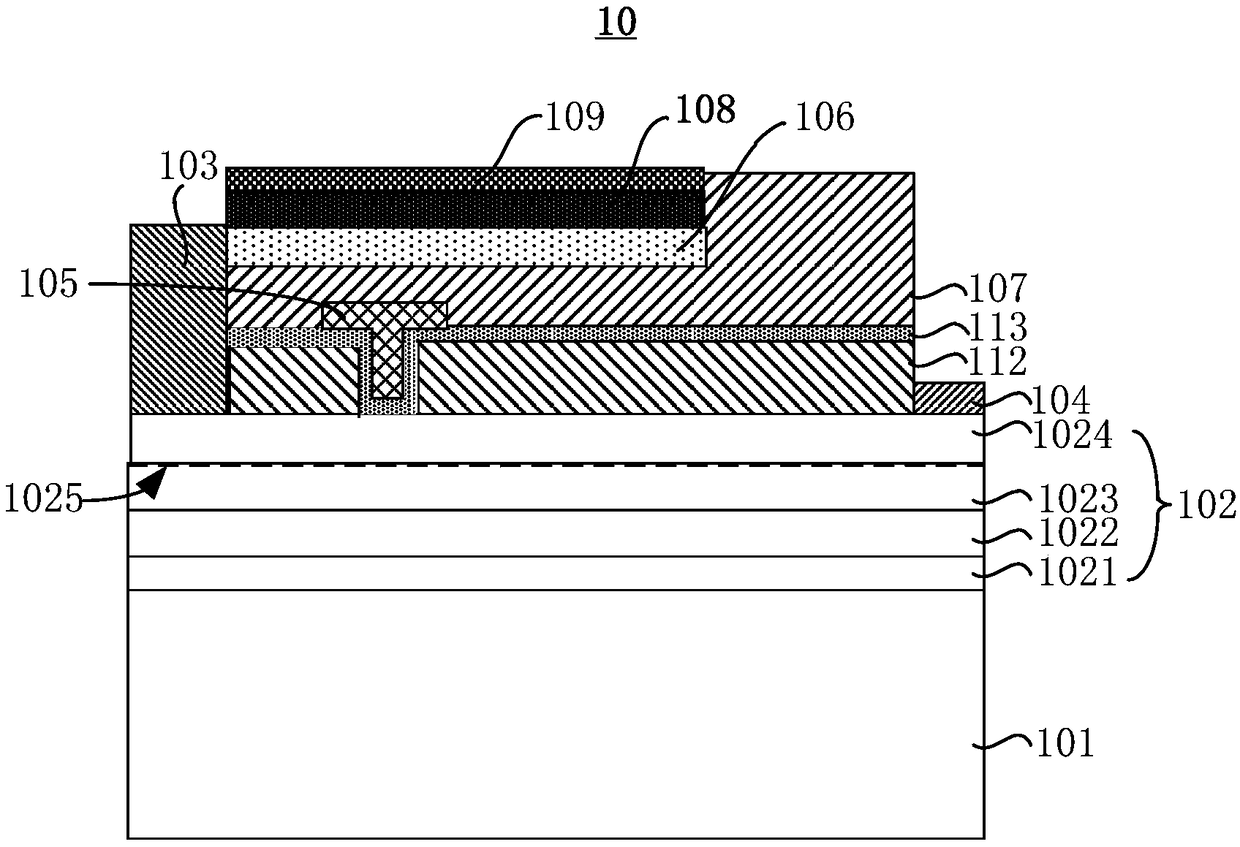

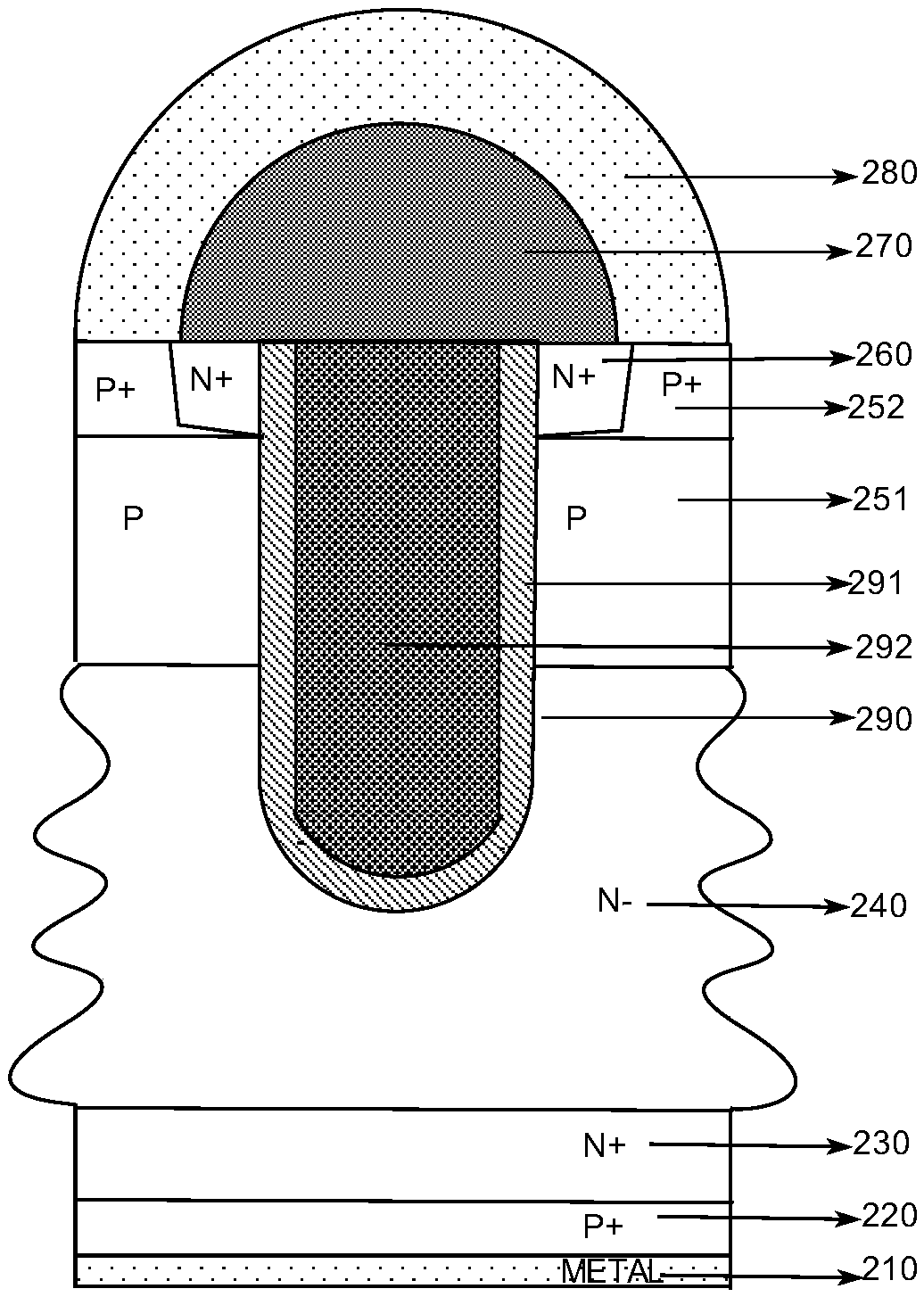

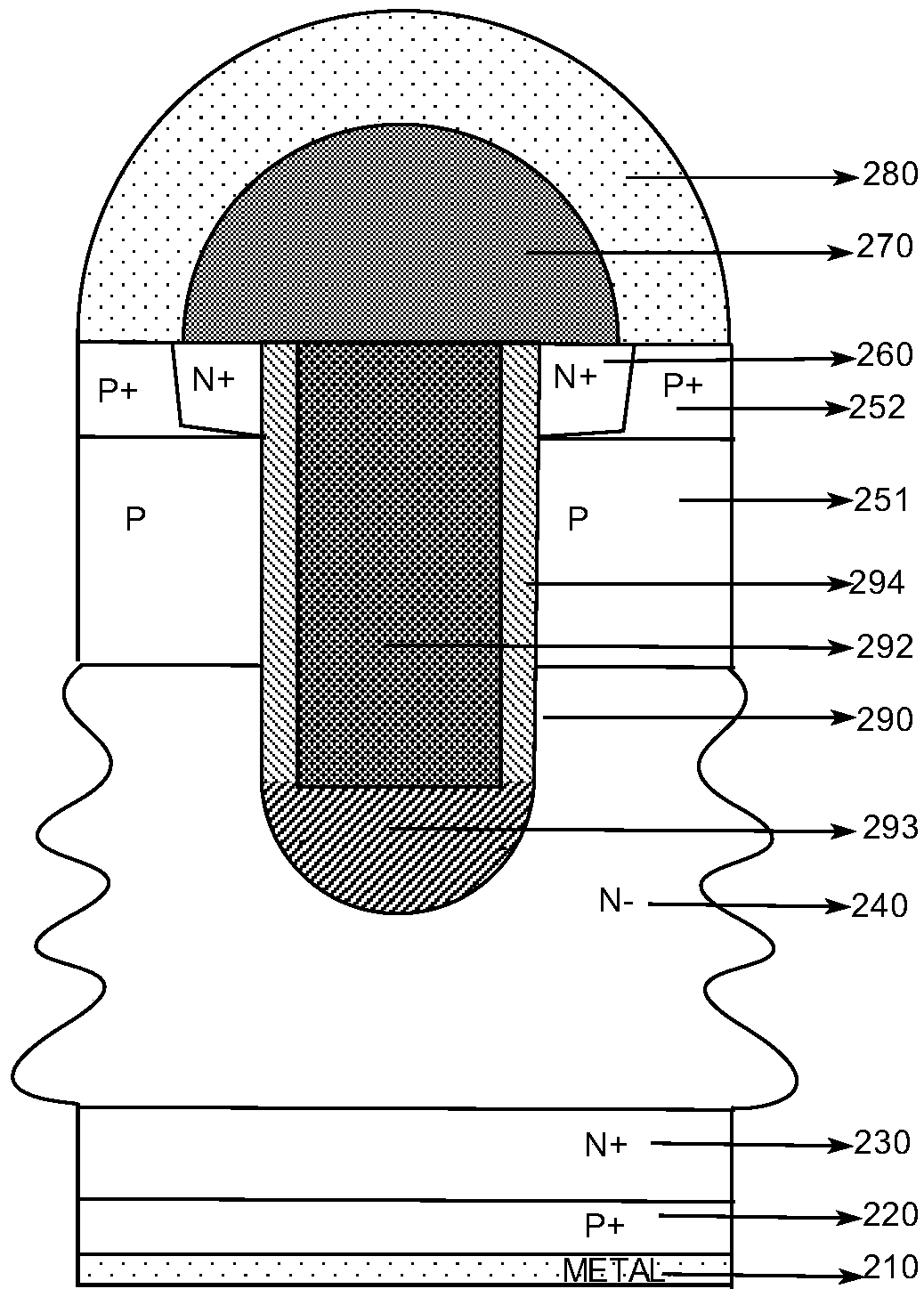

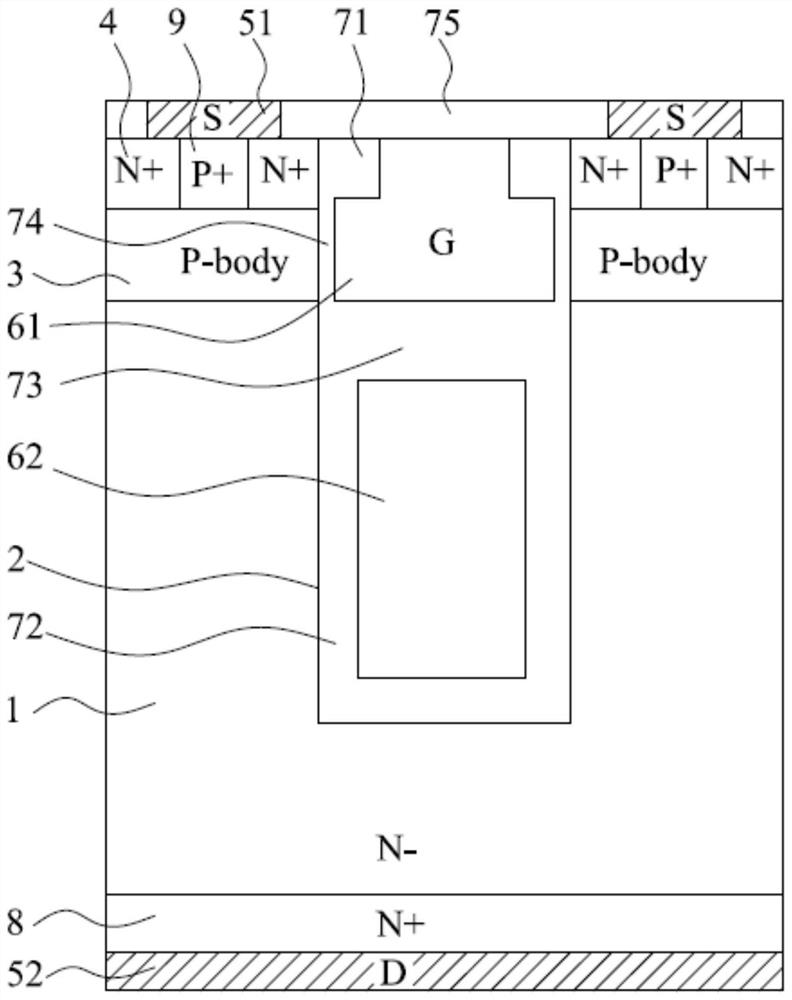

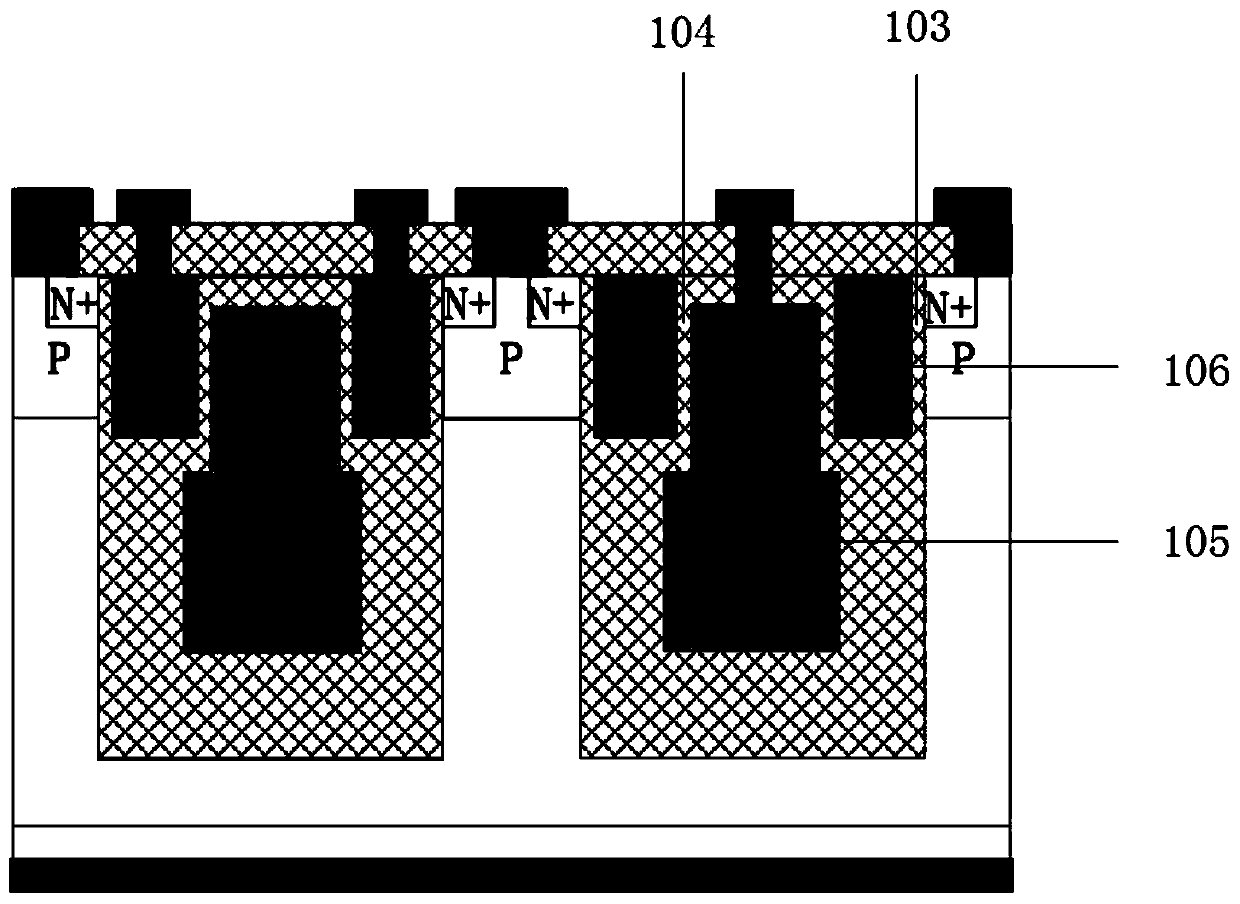

Integrated trench mosfet and junction barrier schottky rectifier with trench contact structures

ActiveUS20090315107A1Improve configurationImproved manufactureSolid-state devicesSemiconductor devicesTrench mosfetMiniaturization

A trench MOSFET in parallel with trench junction barrier Schottky rectifier with trench contact structures is formed in single chip. The present invention solves the drawback brought by some prior arts, for example, the large area occupied by planar contact structure and high gate-source capacitance. As the electronic devices become more miniaturized, the trench contact structures of this invention are able to be shrunk to achieve low specific on-resistance of Trench MOSFET, and low Vf and reverse leakage current of the Schottky Rectifier.

Owner:FORCE MOS TECH CO LTD

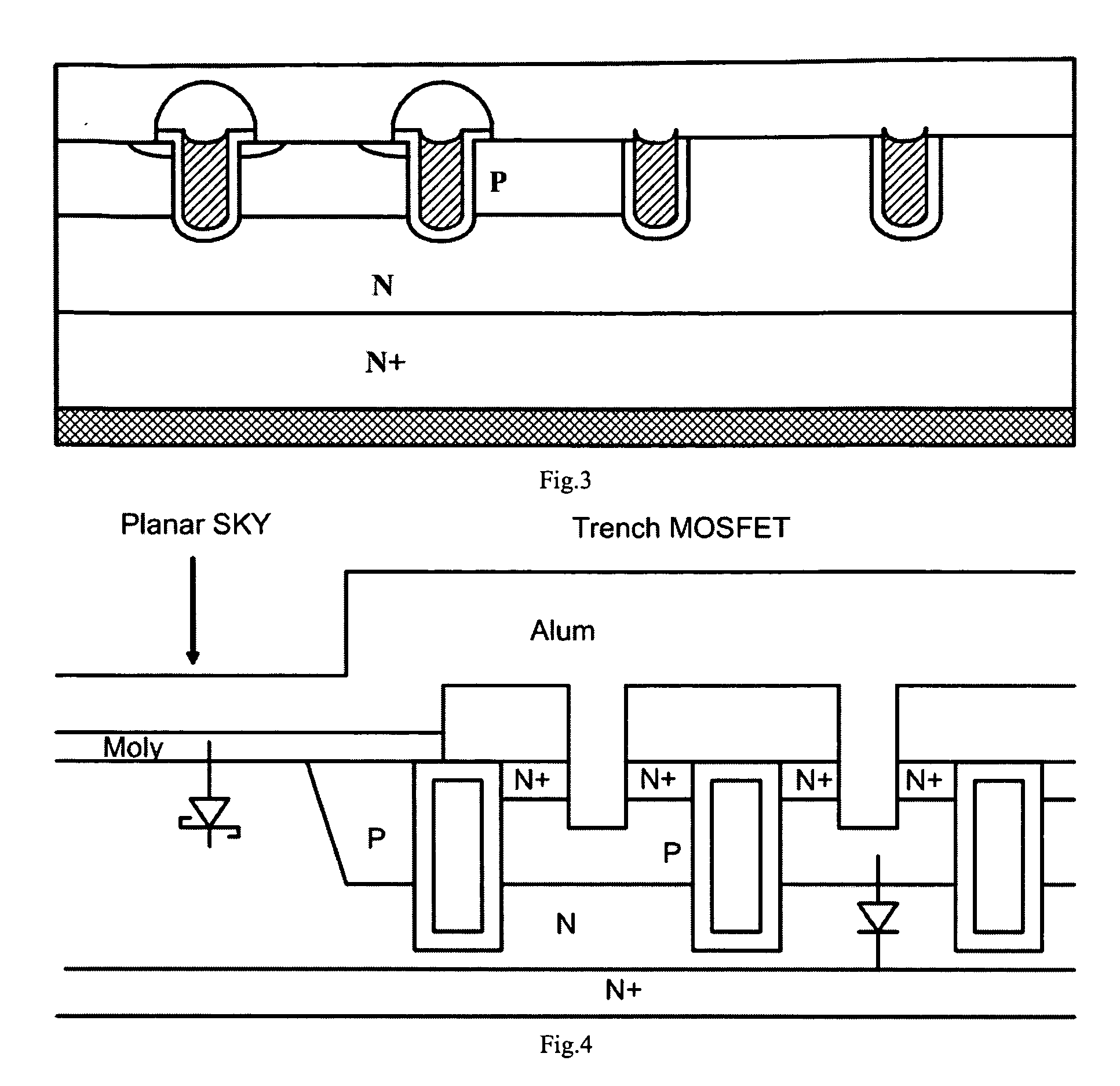

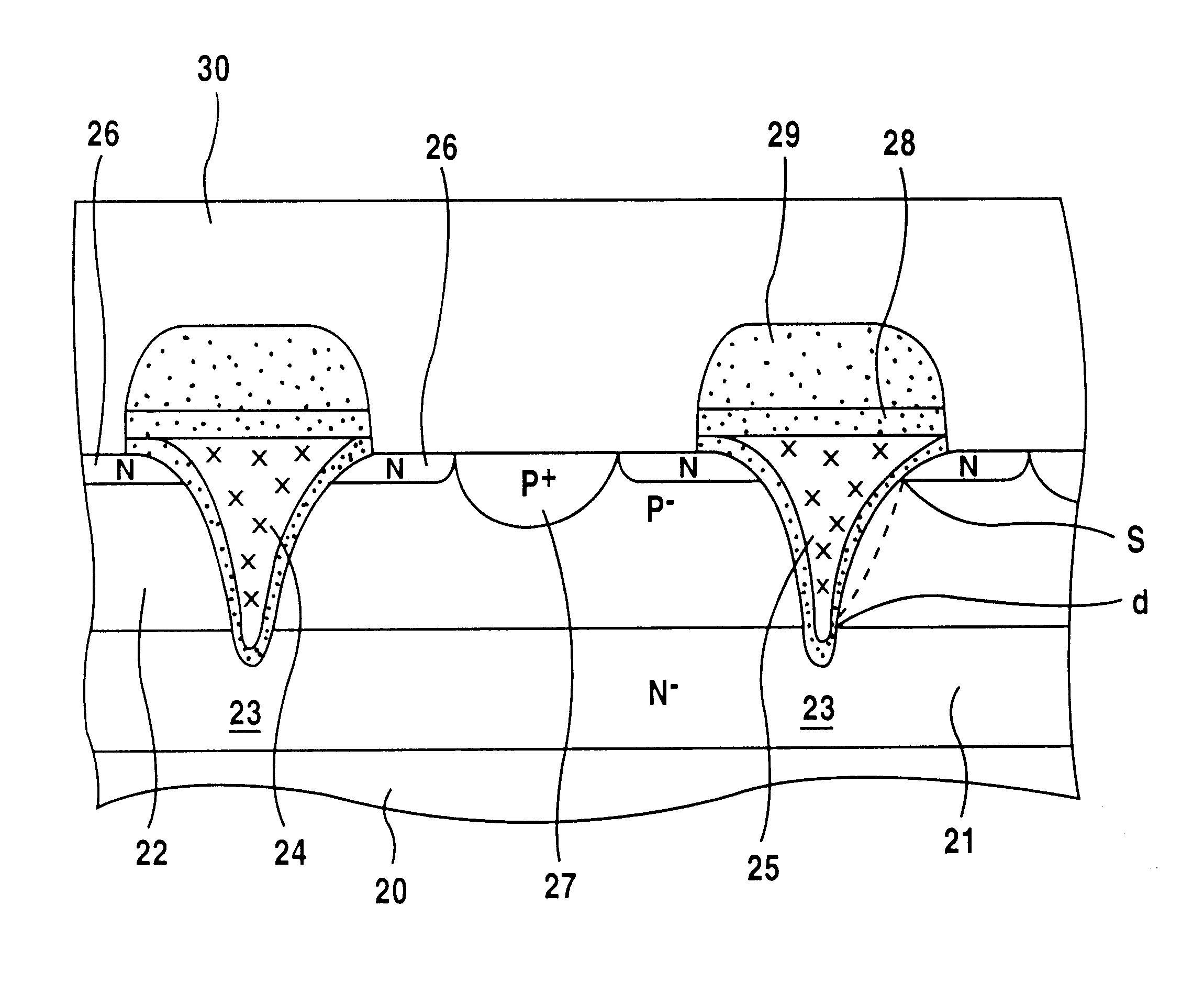

Method of fabricating semiconductor device

InactiveUS6395604B1Semiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate source capacitance

The present invention improves the characteristic of a trench-type vertical MOSFET. When a trench 23 serving as a gate 25 is formed, it is made in a shape of "gamma" which is convex toward the inside of the trench. Thus, the surface area of the trench is reduced so that both gate-source capacitance and gate-drain capacitance can be reduced, thereby shortening the switching time of the MOSFET.

Owner:SEMICON COMPONENTS IND LLC

Integrated trench MOSFET and junction barrier schottky rectifier with trench contact structures

ActiveUS7626231B1Improved device configurationReduce spacingSemiconductor devicesTrench mosfetMiniaturization

A trench MOSFET in parallel with trench junction barrier Schottky rectifier with trench contact structures is formed in single chip. The present invention solves the drawback brought by some prior arts, for example, the large area occupied by planar contact structure and high gate-source capacitance. As the electronic devices become more miniaturized, the trench contact structures of this invention are able to be shrunk to achieve low specific on-resistance of Trench MOSFET, and low Vf and reverse leakage current of the Schottky Rectifier.

Owner:FORCE MOS TECH CO LTD

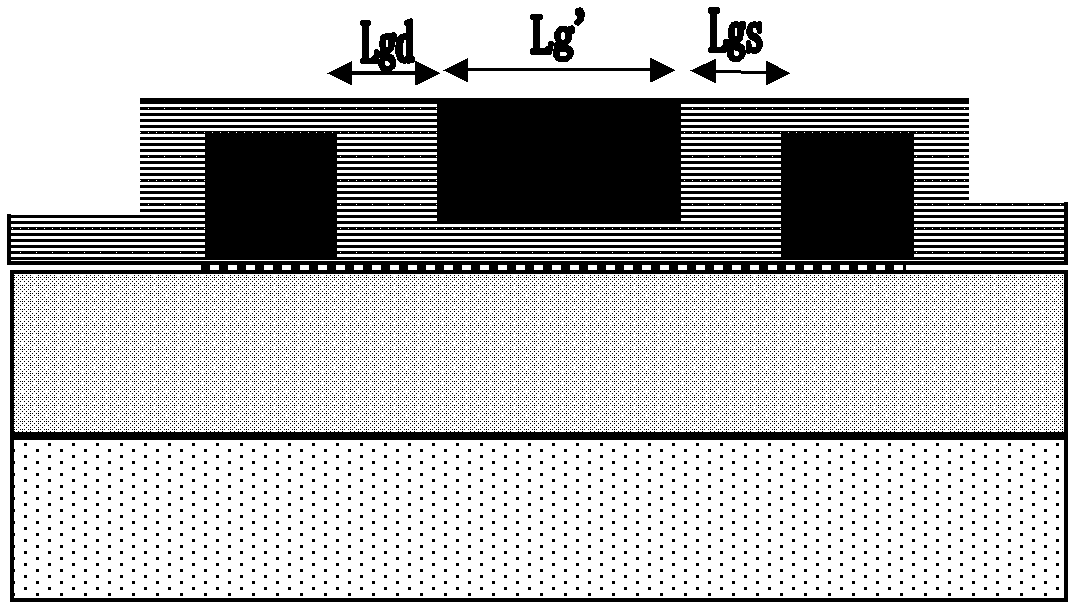

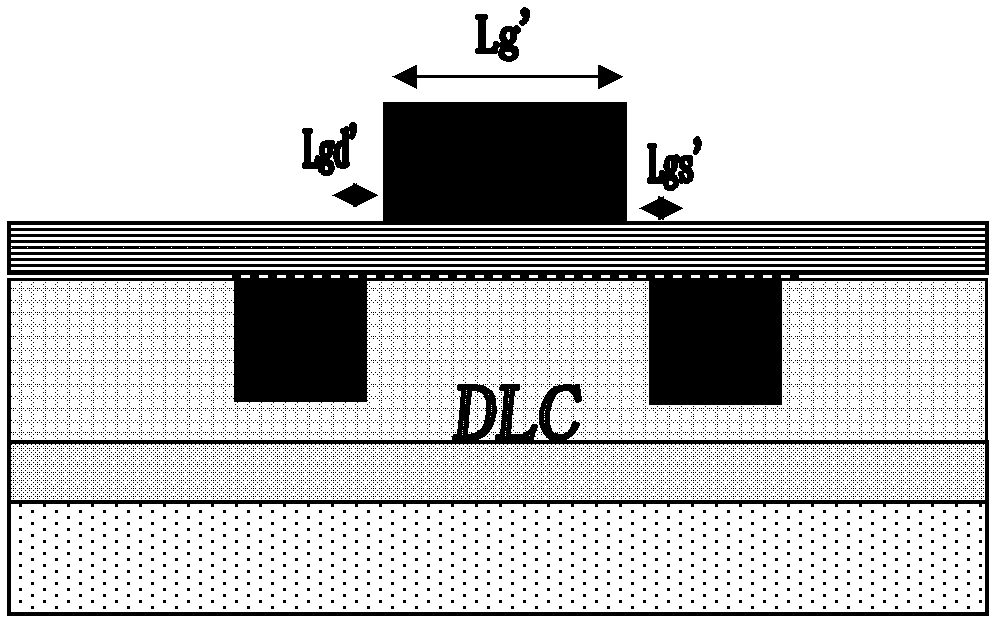

Source-drain buried graphene transistor device on diamond-like carbon substrate and manufacture method

InactiveCN103000669ALower channel resistanceReduce horizontal spacingSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricDiamond-like carbon

A source-drain buried graphene transistor device on a diamond-like carbon substrate and a manufacture method are applicable to radio frequency communication. The manufacture method includes: firstly, depositing a layer of diamond-like carbon amorphous carbon smooth in surface and stable in chemical property on the substrate by the aid of a magnetic filtered cathode vacuum arc system; secondly, etching a source trench and a drain trench on the diamond-like carbon amorphous carbon insulating layer and filling electrode metal into the trenches; thirdly, planarizing and cleaning the surface of the substrate prior to transferring graphene grown by a chemical vapor deposition method to the cleaned substrate; fourthly, growing gate insulating dielectric by an atomic layer deposition method and sputtering gate electrode metal; and finally, forming a metal gate by means of reactive ion etching and depositing low-K insulating dielectric to protect the device. Carrier mobility of a graphene transistor is high, and the source-drain buried structure is capable of decreasing the graphene length of a region uncovered by the gate, so that gate-source capacitance, gate-drain capacitance and channel resistance are reduced, and high-frequency performance and efficiency of the graphene transistor are improved. The source-drain buried graphene transistor device can be widely applied to small-sized high-frequency graphene integrated circuits.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

CMOS imager with wide dynamic range Pixel

InactiveUS20070023786A1Additional circuitryImprove performanceTelevision system detailsTelevision system scanning detailsCMOS sensorGate source capacitance

In one aspect of the present invention, a light sensor is provided in the active pixel sensor cell for sensing incident radiation. The voltage corresponding to the photon-generated or other radiation-generated charge in the active pixel sensor cell is stored on a storage node via a sample-and-hold capacitor. Additional elements, such as source-follower transistors, may reside between the sensing element and the sample-and-hold capacitor. The signal is read via a readout source-follower (RSF) transistor. The readout source-follower drain is connected to the row select switch while its drain is connected to the output node on the column output bus. This configuration couples the storage node to the gate-source capacitance of the readout source-follower transistor. This allows the voltage on the storage node to increase proportionally to the increase in voltage on the readout node when the row select is closed and thus enables the drain current to flow through the RSF to the column output bus.

Owner:IMAGERLABS

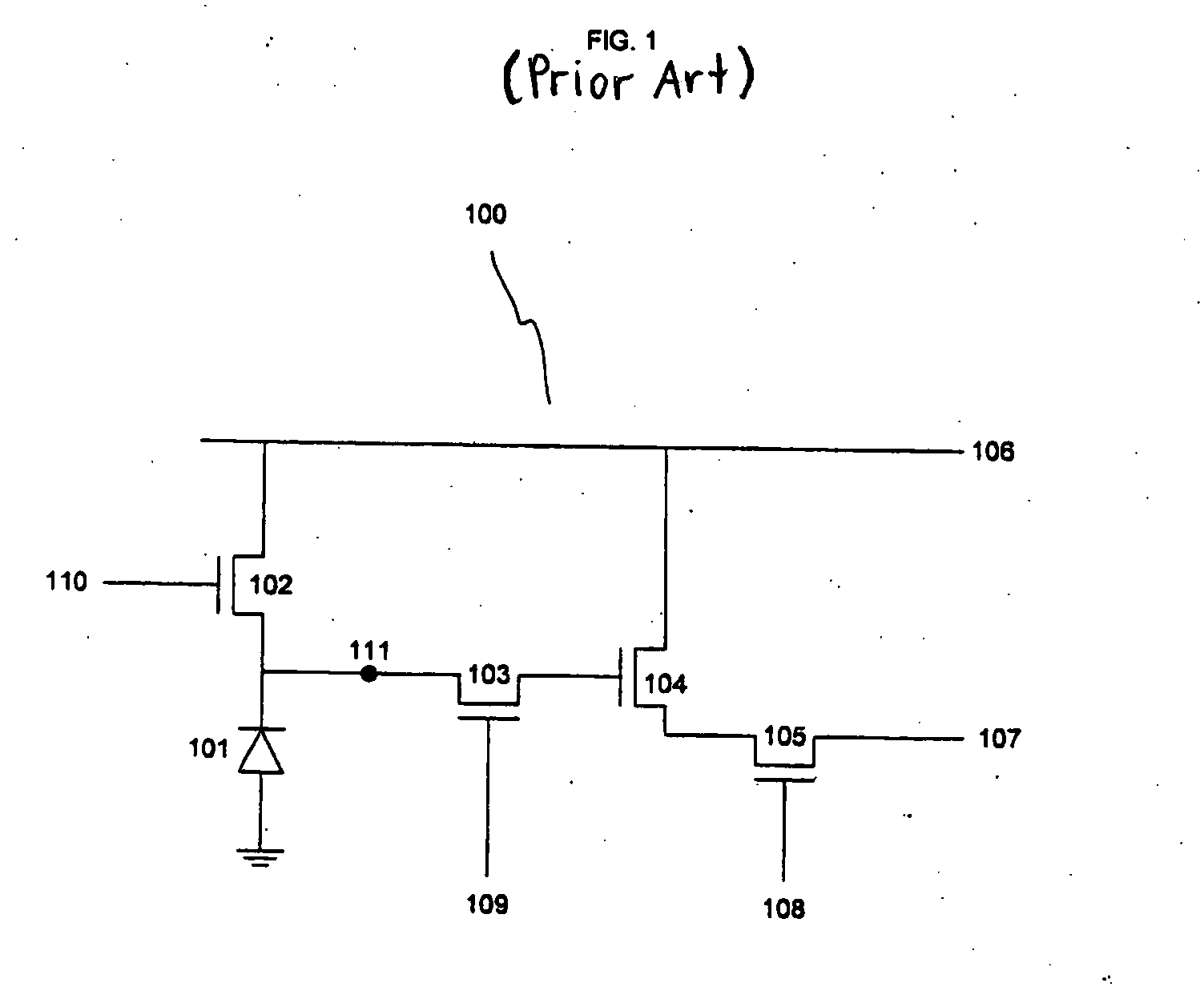

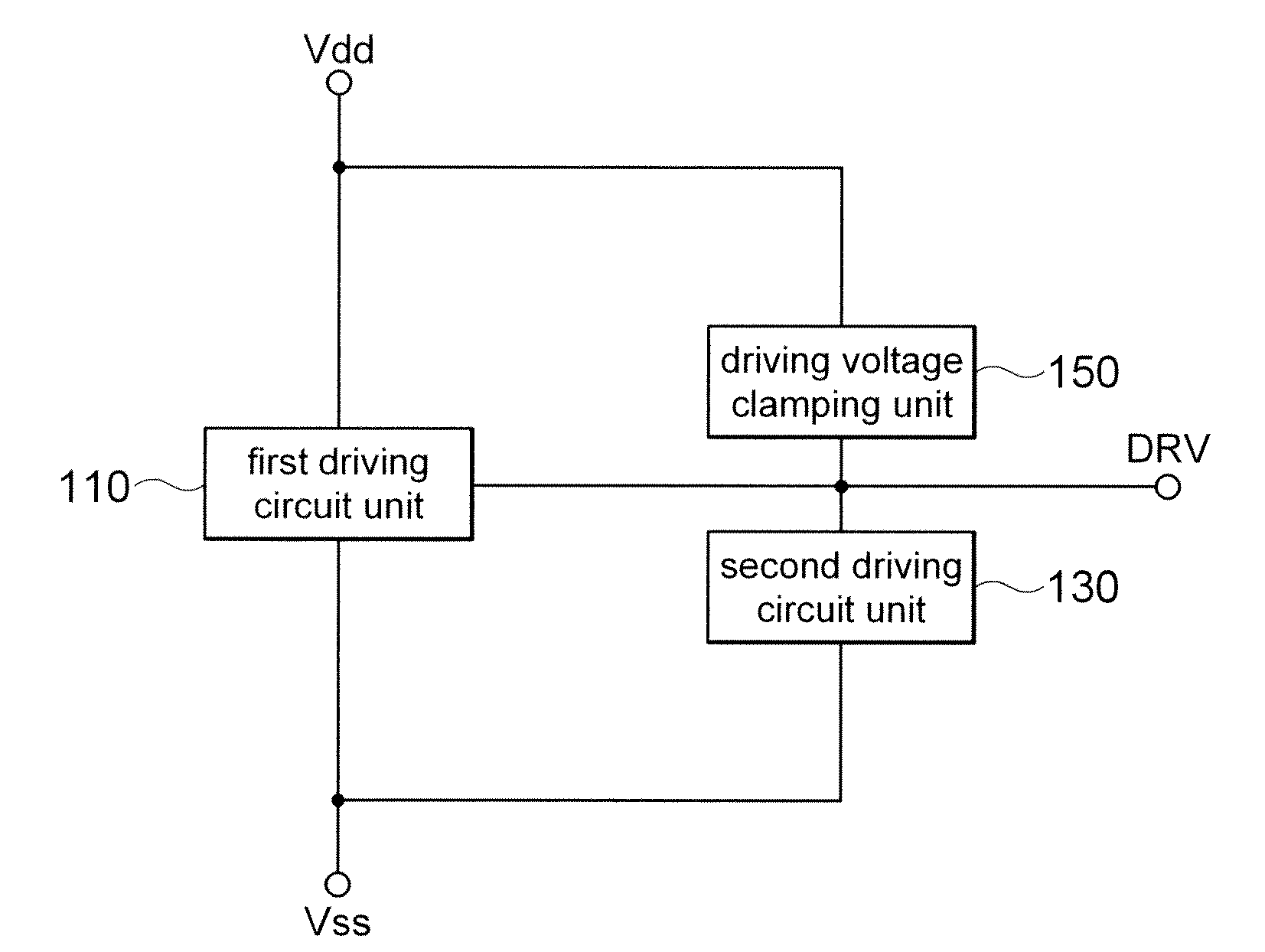

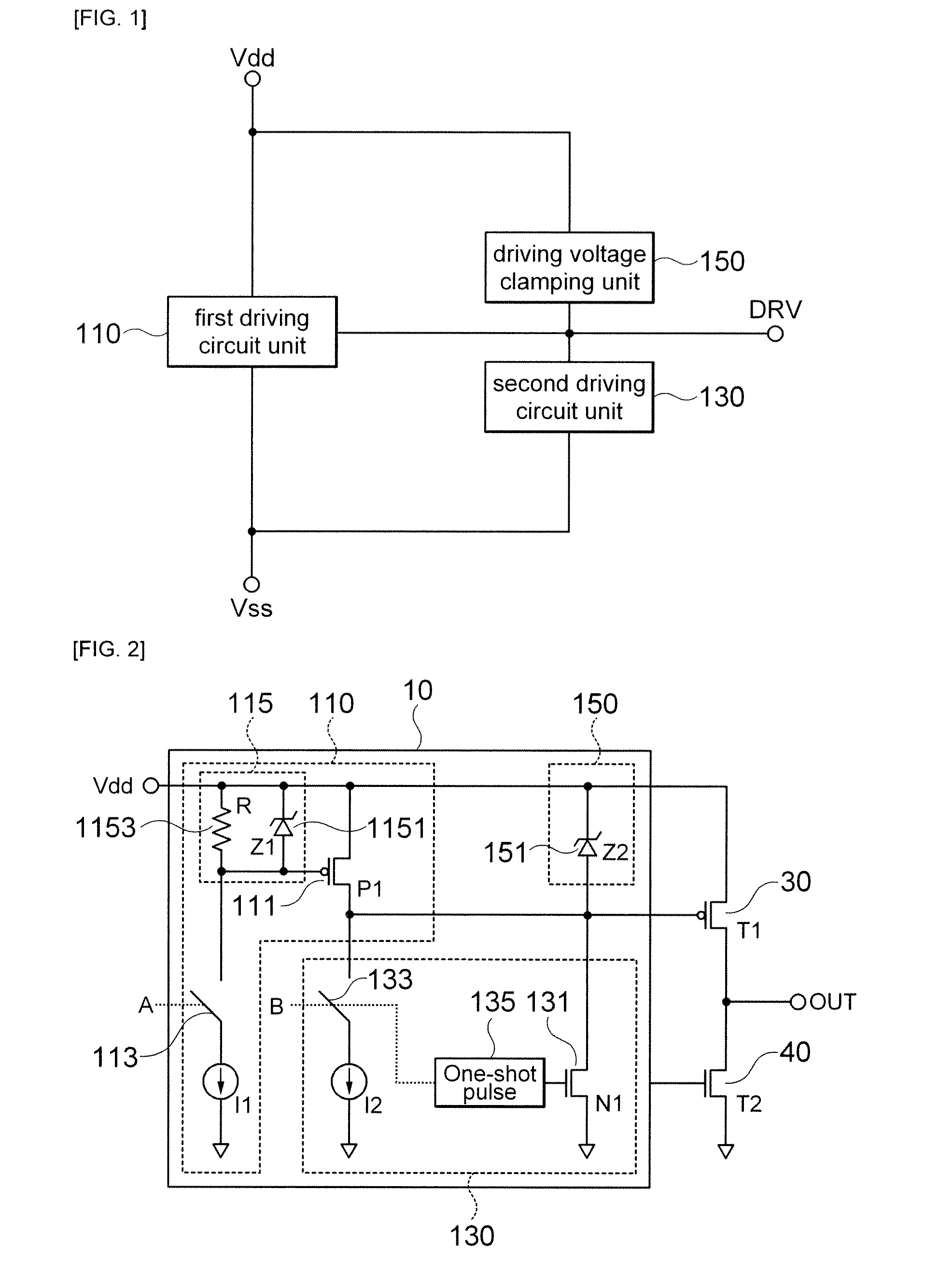

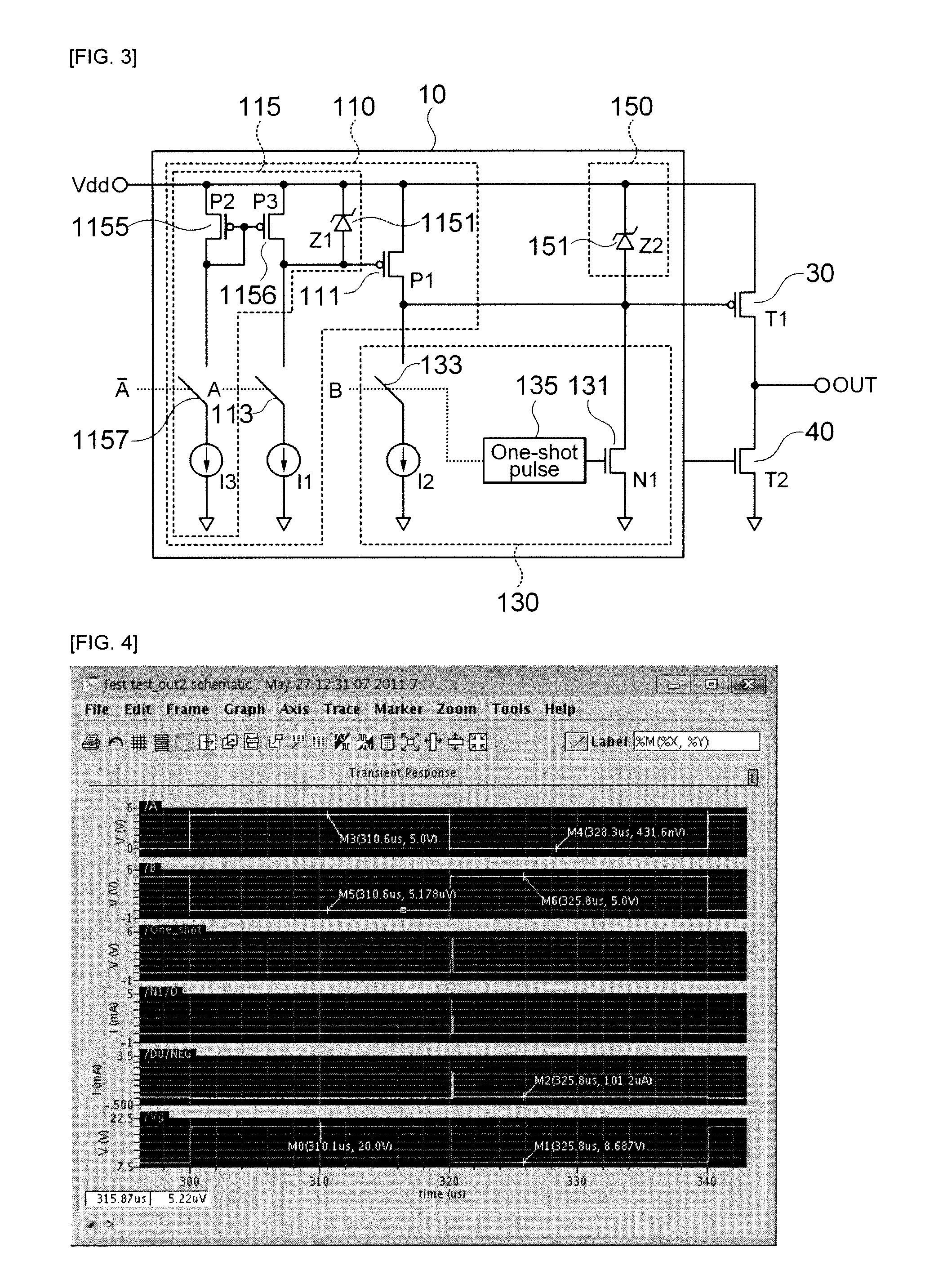

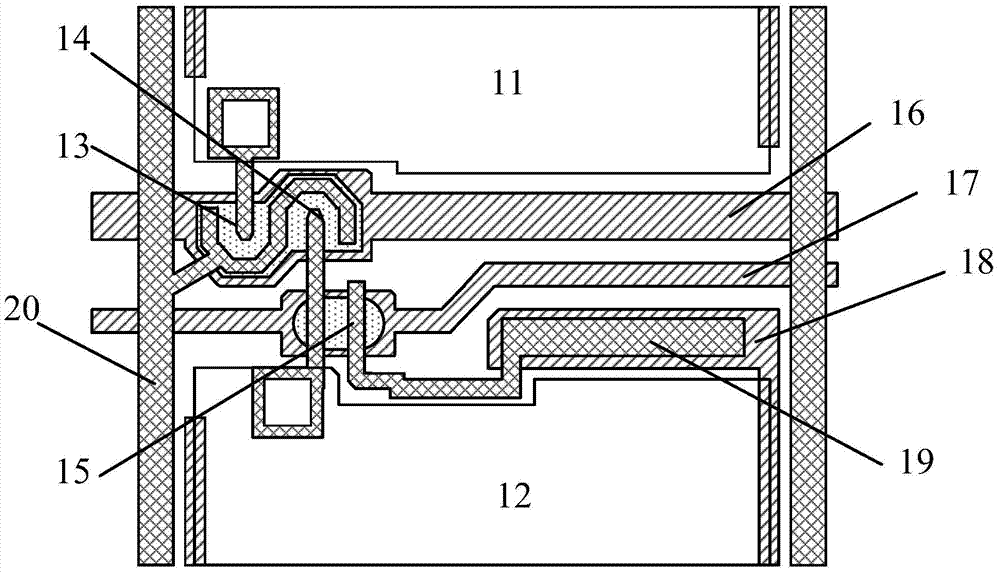

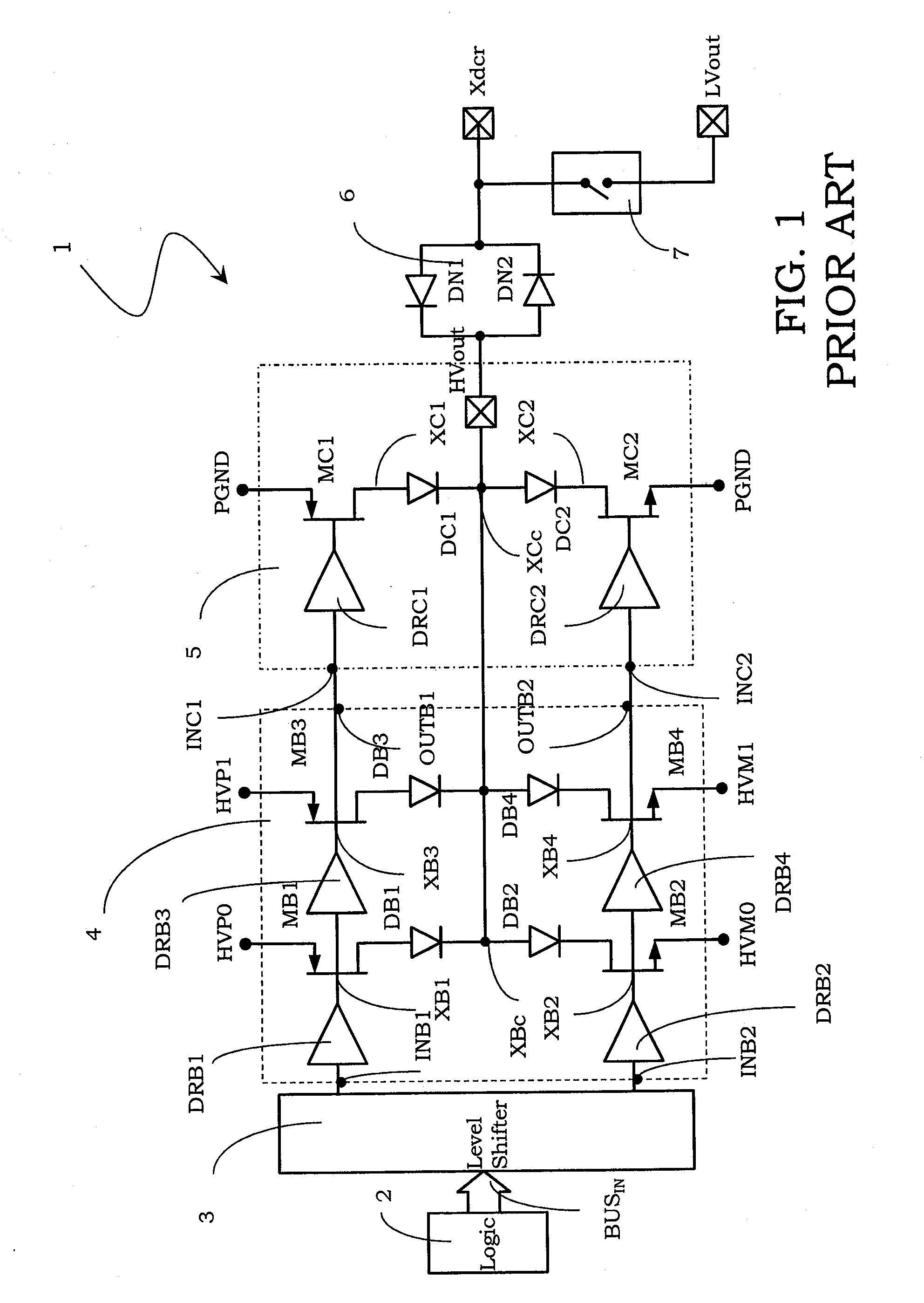

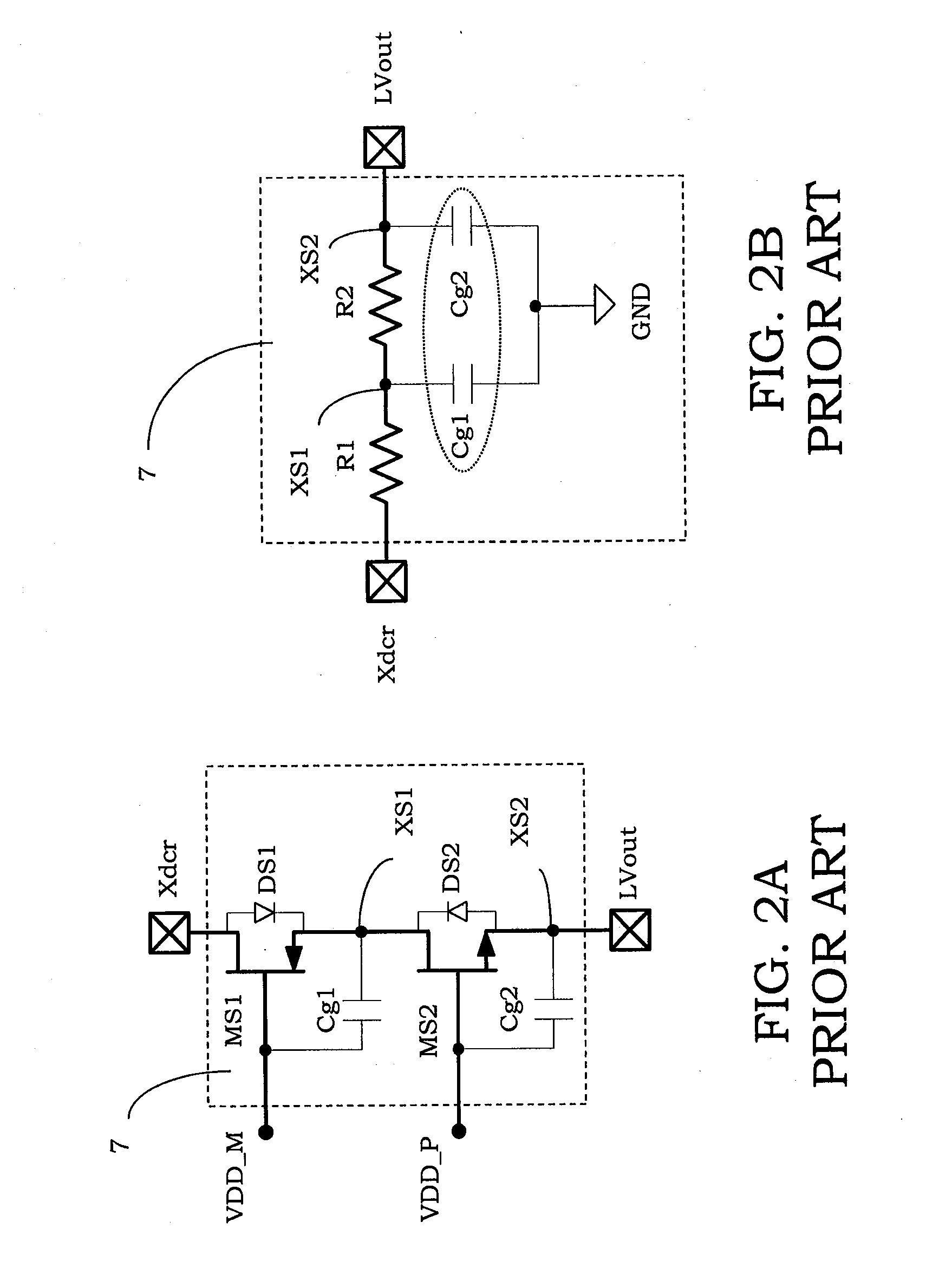

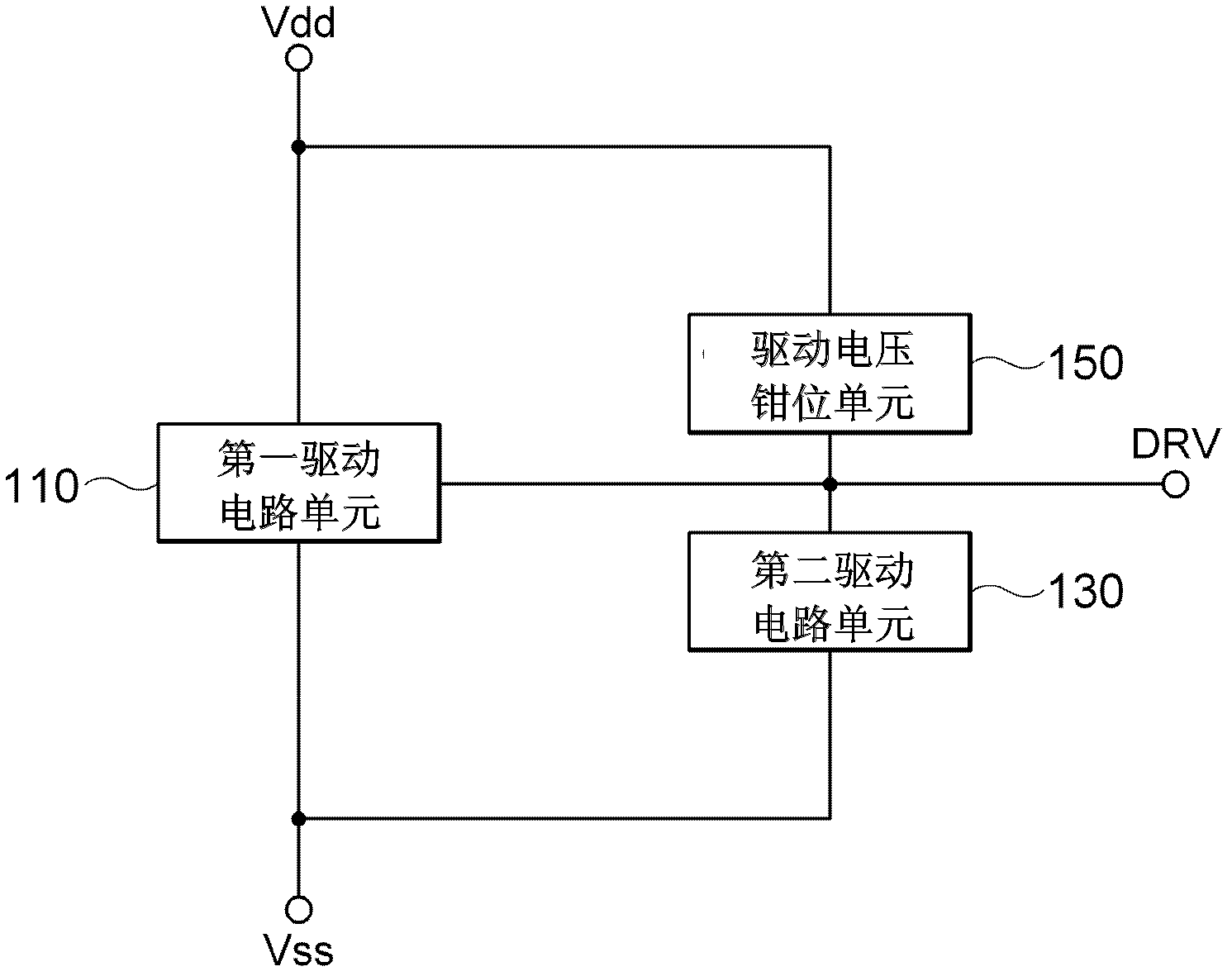

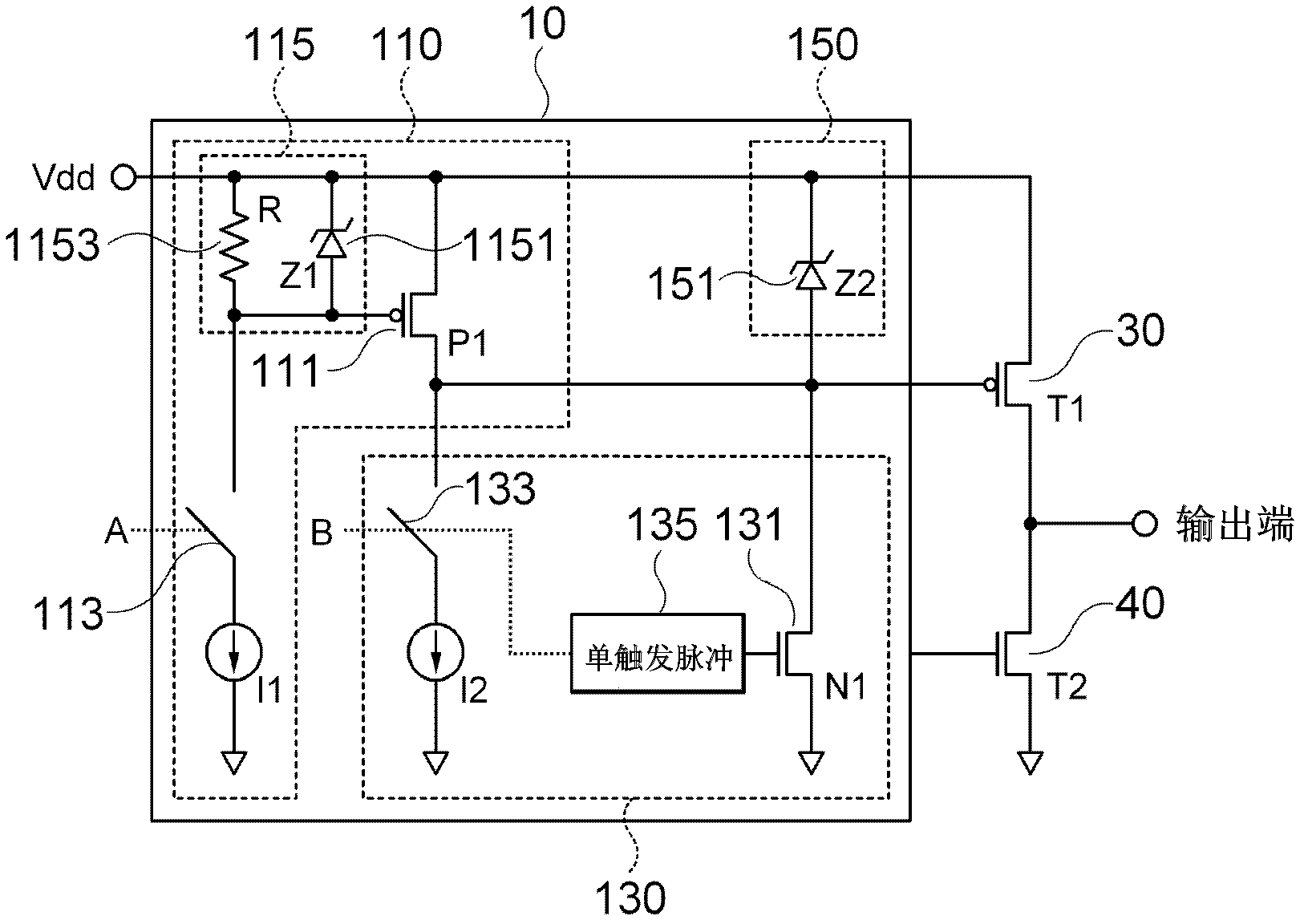

Output driving circuit and transistor output circuit

InactiveUS20130038355A1Guaranteed uptimeReduce current consumptionElectronic switchingElectric pulse generatorDriver circuitEngineering

The present invention relates to an output driving circuit and a transistor output circuit. In accordance with an embodiment of the present invention, an output driving circuit including: a first driving circuit unit driven according to on operation of a first switch to supply high voltage power source to a gate of an output transistor; a second driving circuit unit driven by a one-shot pulse generated according to on operation of a second switch, which operates complementarily with the first switch, to discharge a gate-source capacitance of the output transistor; and an output driving voltage clamping unit disposed between a high voltage power source terminal and the gate of the output transistor in parallel with the first driving circuit unit to maintain a gate potential of the output transistor discharged according to the on operation of the second switch is provided.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Low-color-error liquid crystal array substrate and drive method thereof

ActiveCN104122724AAdjust the voltage differenceConsistent voltageStatic indicating devicesSolid-state devicesElectricityGate source capacitance

The invention relates to a low-color-error liquid crystal array substrate and a corresponding drive method. The low-color-error liquid crystal array substrate comprises a plurality of pixel structures, each pixel structure comprises a primary pixel area and a secondary pixel area, a gate line is arranged between each primary pixel area and the corresponding secondary pixel area and is provided with a first thin film transistor and a second thin film transistor which are connected to the primary pixel area and the secondary pixel area respectively, the position between each gate line and the corresponding secondary pixel area further comprises a public electrode wire and a metal component, each public electrode wire is provided with a standoff capacitor, and each metal component is provided with a share thin film transistor connected with the corresponding standoff capacitor and electrically connected with a data line through a through hole. Through the design of omitting a sub gate line, switches of the share thin film transistors are switched on directly through signal voltage of the data lines; the inconformity of voltage between each primary pixel area and the corresponding secondary pixel area is solved by adjusting the gate source capacitance of the thin film transistor in the primary pixel area, the aperture opening ratio is improved, and the processing cost is lowered.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

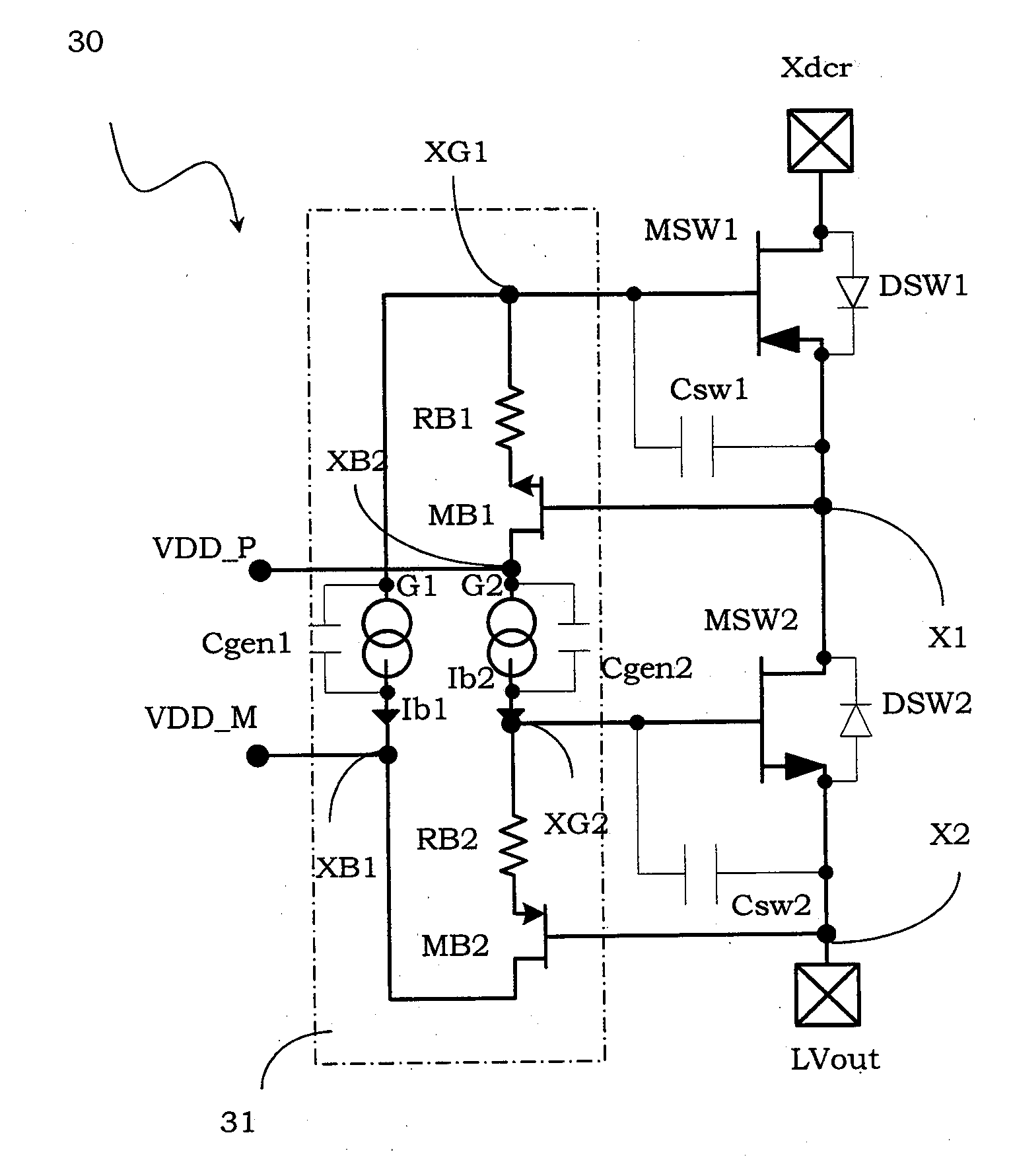

Low voltage isolation switch, in particular for a transmission channel for ultrasound applications

ActiveUS20120268189A1Guaranteed to workPulse automatic controlElectronic switchingElectricityLow voltage

A switching circuit is electrically coupled between a connection terminal and an output terminal of a transmission channel and includes first and second switching transistors electrically coupled in series to each other and having respective body diodes in anti-series, between the connection terminal and the output terminal. The switching circuit comprises a bootstrap circuit connected to respective first and second control terminals of these first and one second switching transistors, as well as to respective first and second voltage references. The bootstrap circuit includes a first parasitic capacitance electrically coupled between the first control terminal and a first bootstrap node, and a second parasitic capacitance electrically coupled between the second control terminal and a second bootstrap node. The parasitic capacitances have value of at least one order of magnitude lower with respect to the gate-source capacitances of the first and second switching transistors.

Owner:STMICROELECTRONICS SRL

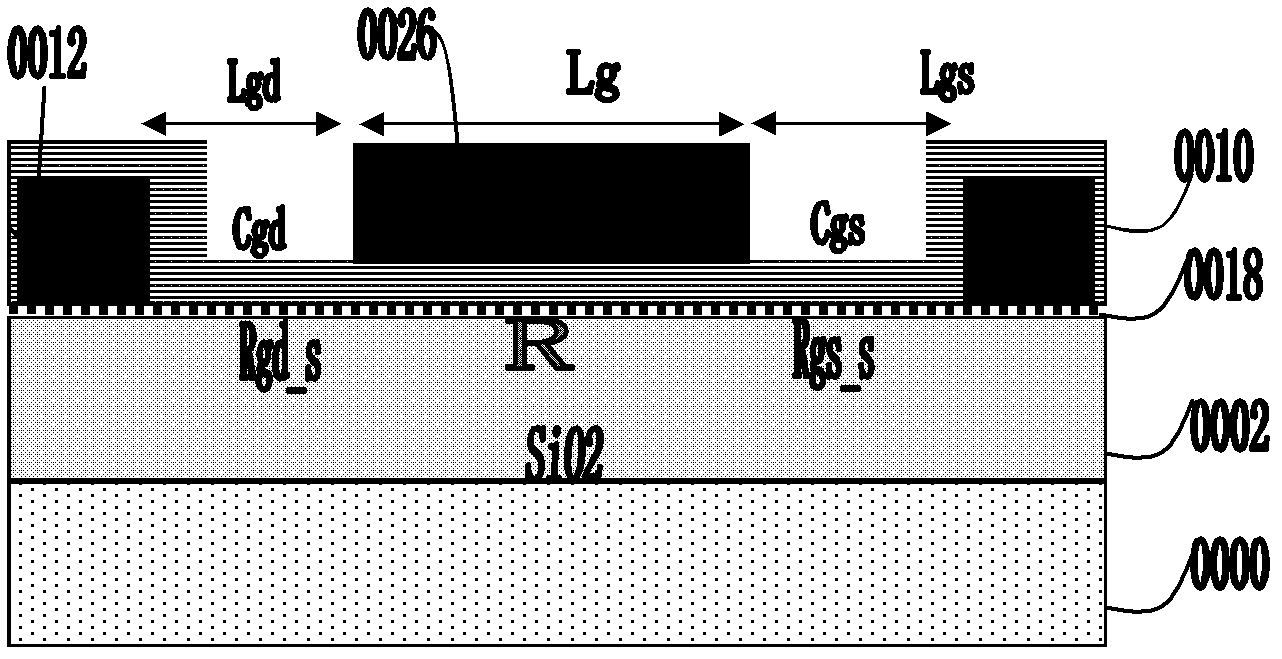

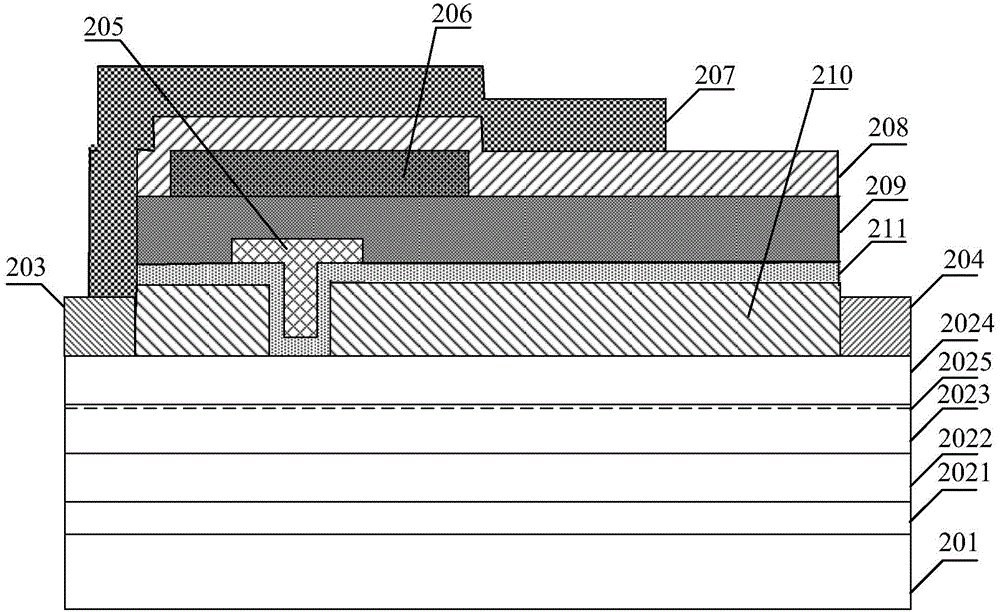

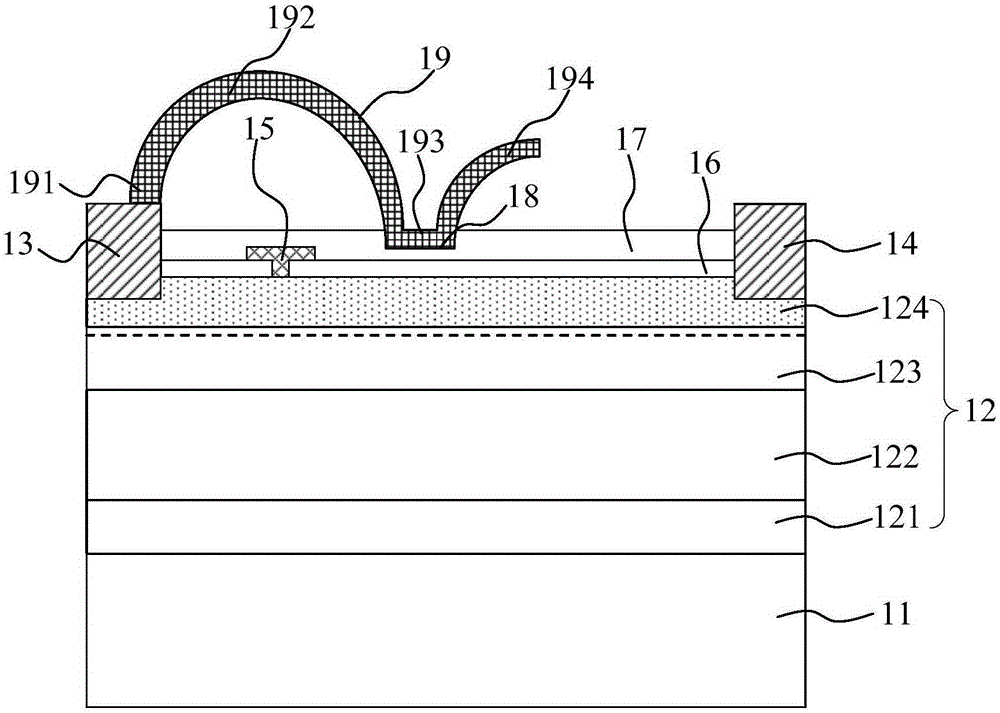

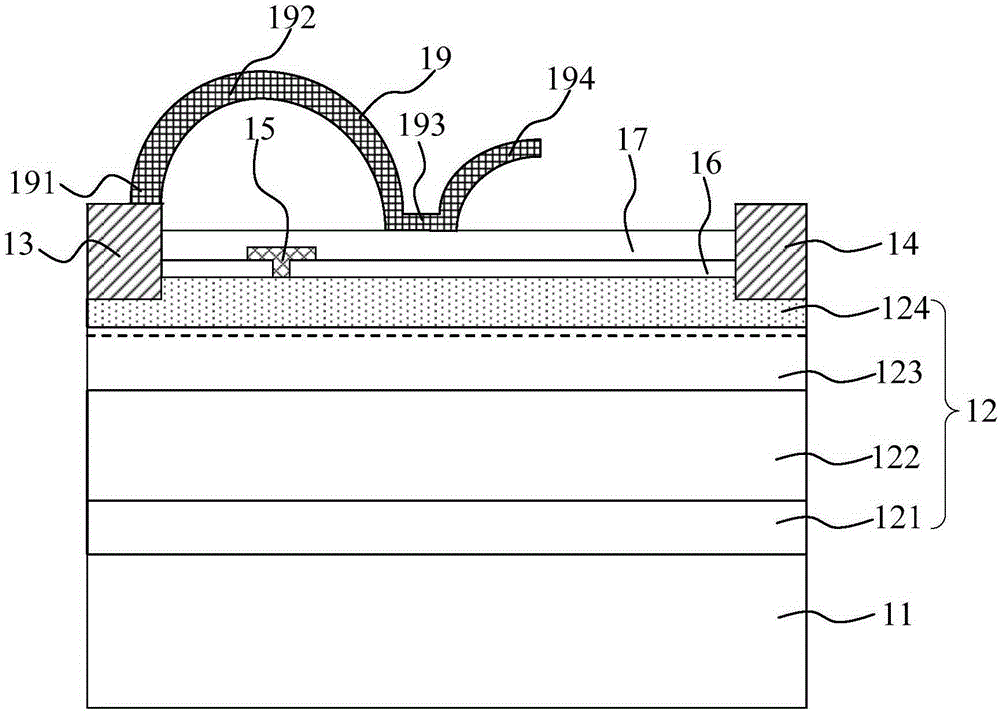

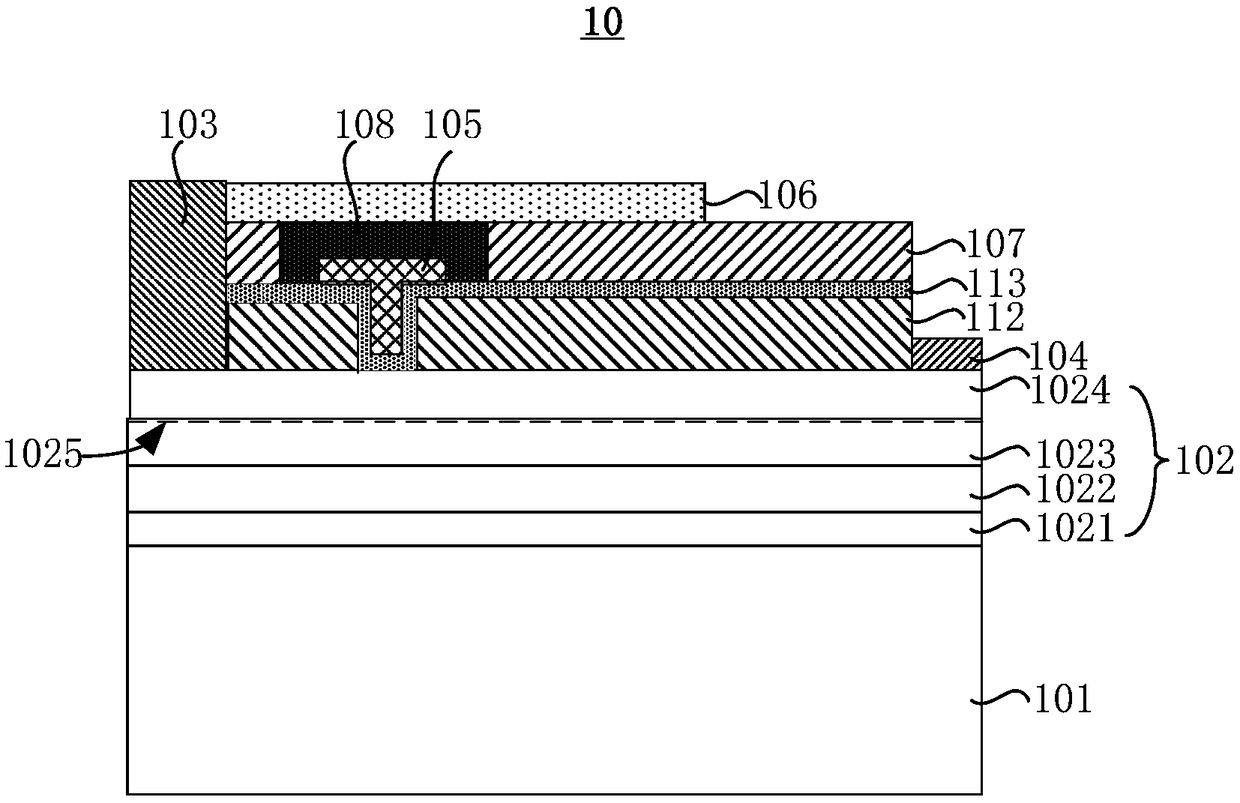

Semiconductor device and preparation method thereof

ActiveCN105322005AIncrease gate-source capacitanceIncrease in sizeSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSource field

The invention discloses a semiconductor device and a preparation method thereof. The semiconductor device comprises a substrate, a semiconductor layer, a source, a drain, a grid, a source field plate and a high dielectric constant dielectric layer, wherein the semiconductor layer is located on the substrate; the source and the drain are located on the semiconductor layer; the grid on the semiconductor layer is arranged between the source and the drain; the source field plate is electrically connected with the source; the high dielectric constant dielectric layer is located between the grid and the source field plate; and the dielectric constant of the high dielectric constant dielectric layer is greater than 3.9. The semiconductor device disclosed by the invention has relatively high gate-source capacitance, so that node capacitance of the semiconductor device and a structure cascaded with the semiconductor device can be matched with each other.

Owner:GPOWER SEMICON

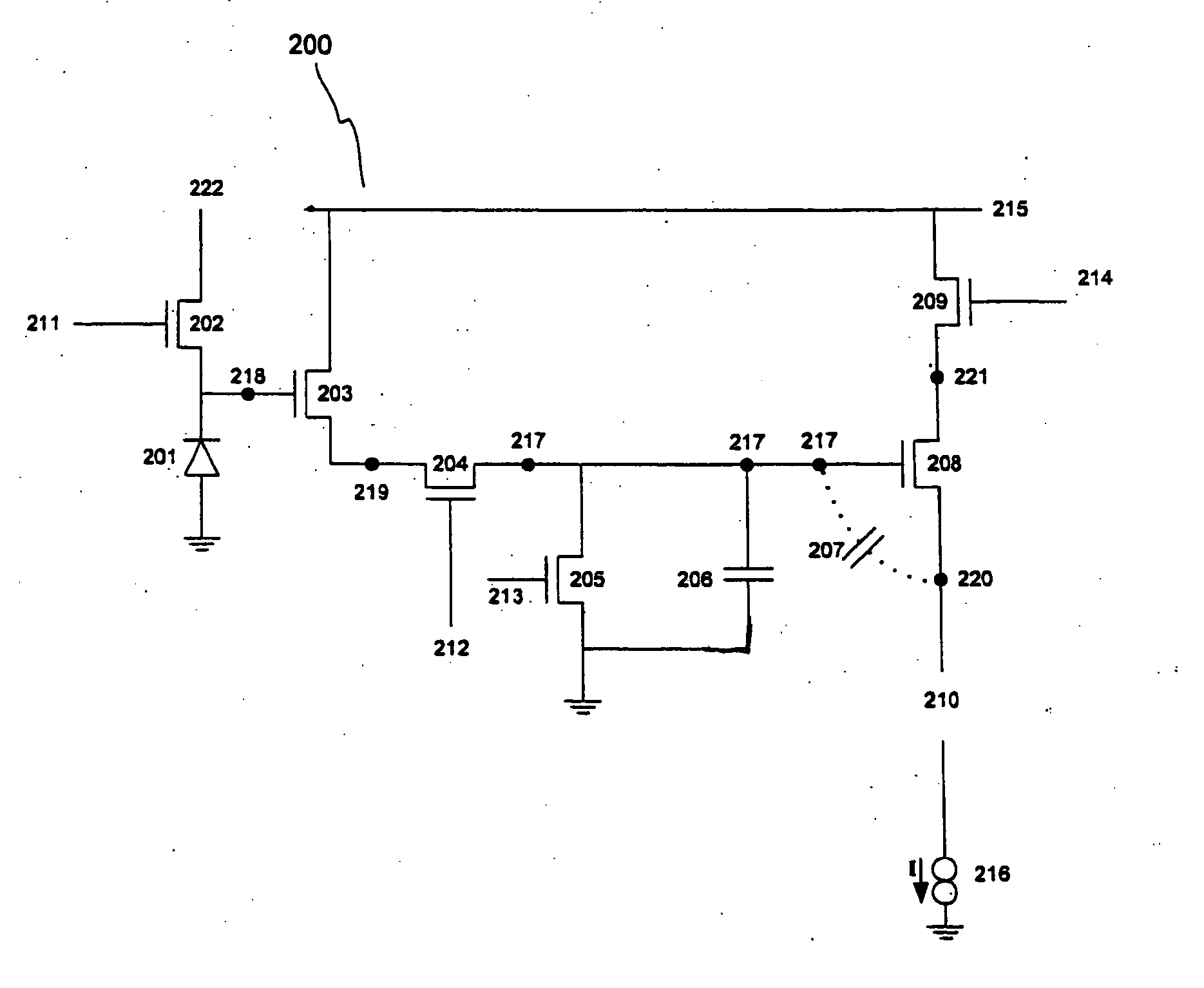

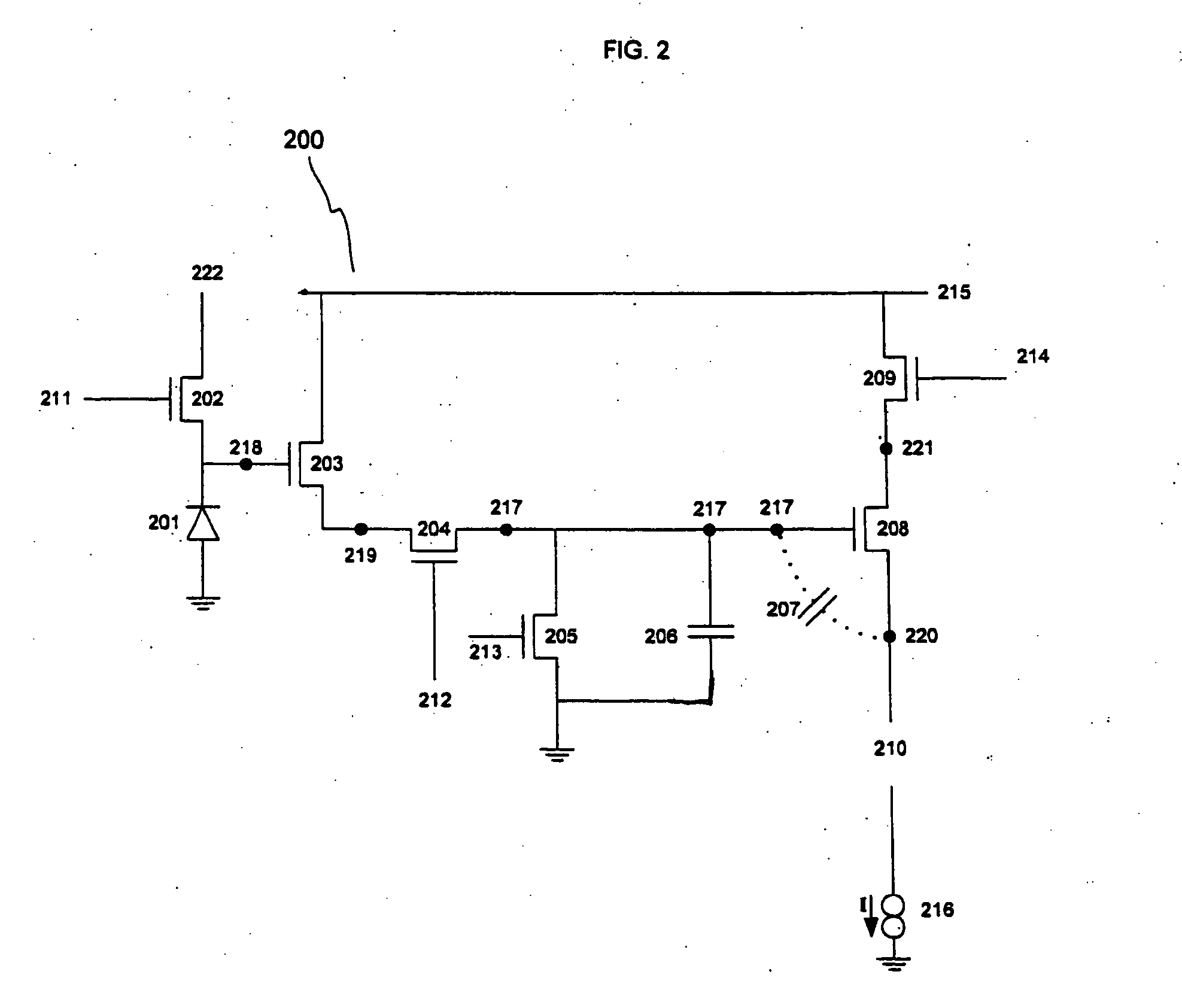

Output driving circuit and transistor output circuit

InactiveCN102931974AStable jobElectronic switchingLogic circuitsDriver circuitGate source capacitance

The present invention relates to an output driving circuit and a transistor output circuit. In accordance with an embodiment of the present invention, an output driving circuit including: a first driving circuit unit driven according to on operation of a first switch to supply high voltage power source to a gate of an output transistor; a second driving circuit unit driven by a one-shot pulse generated according to on operation of a second switch, which operates complementarily with the first switch, to discharge a gate-source capacitance of the output transistor; and an output driving voltage clamping unit disposed between a high voltage power source terminal and the gate of the output transistor in parallel with the first driving circuit unit to maintain a gate potential of the output transistor discharged according to the on operation of the second switch is provided. Further, a transistor output circuit using the same is provided.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

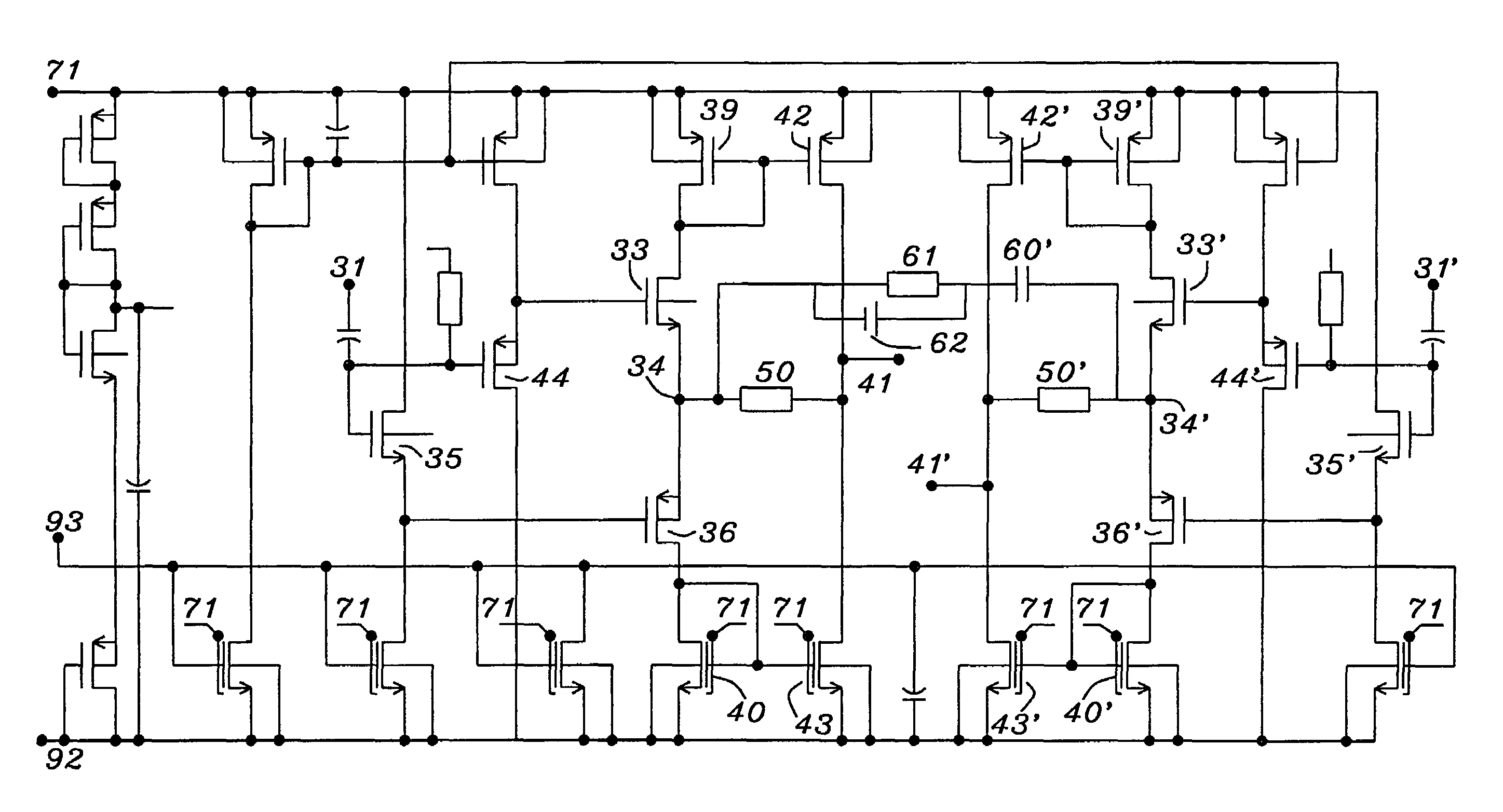

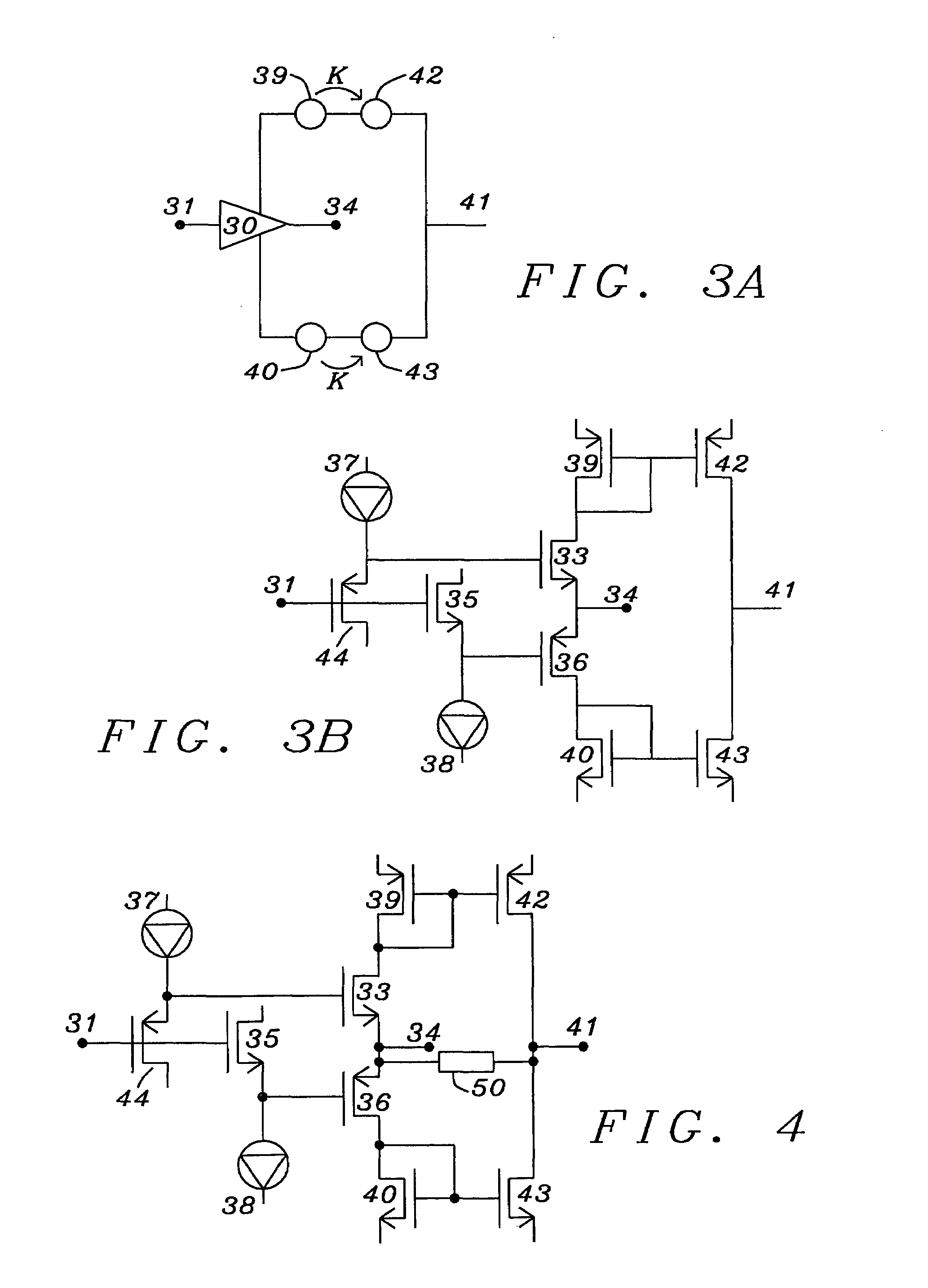

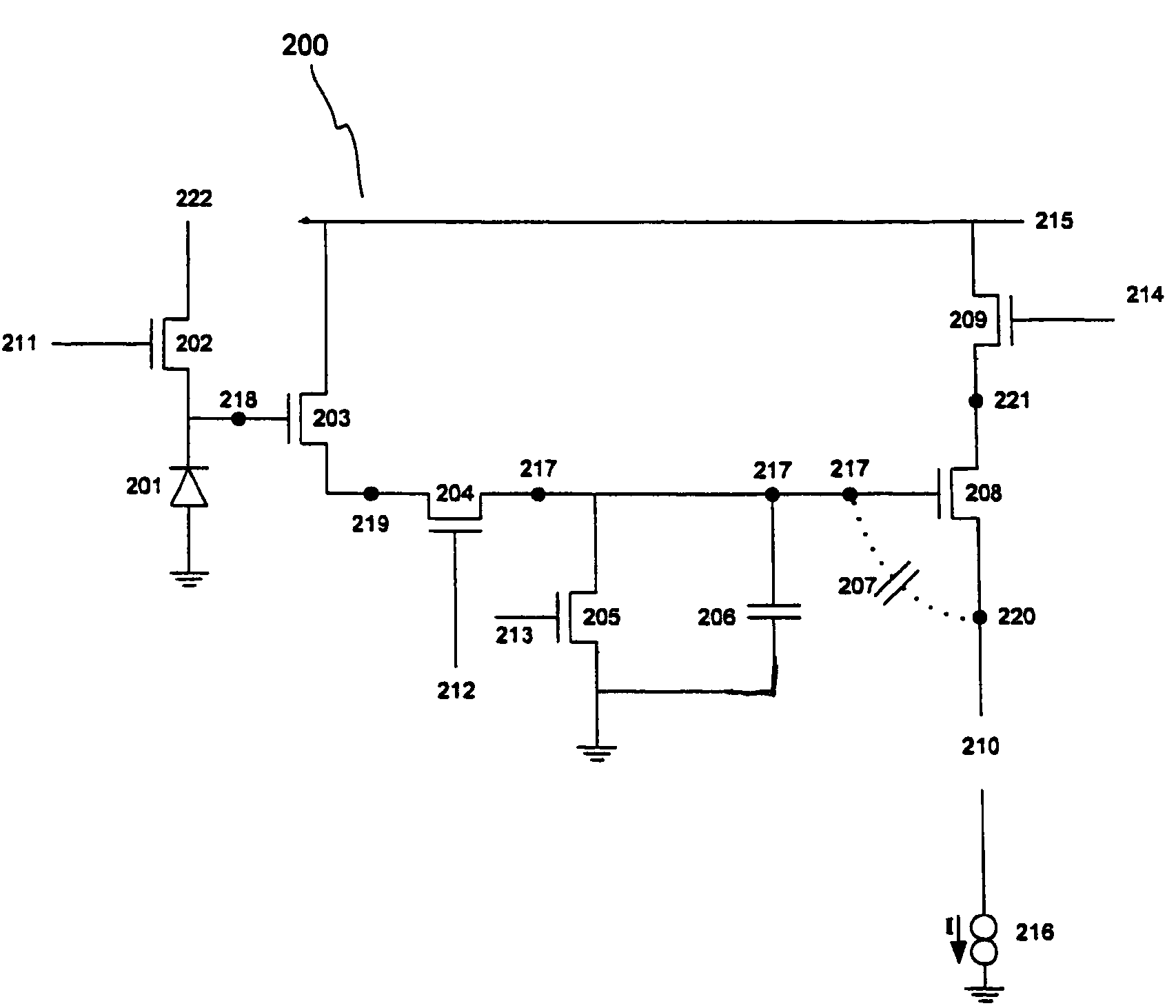

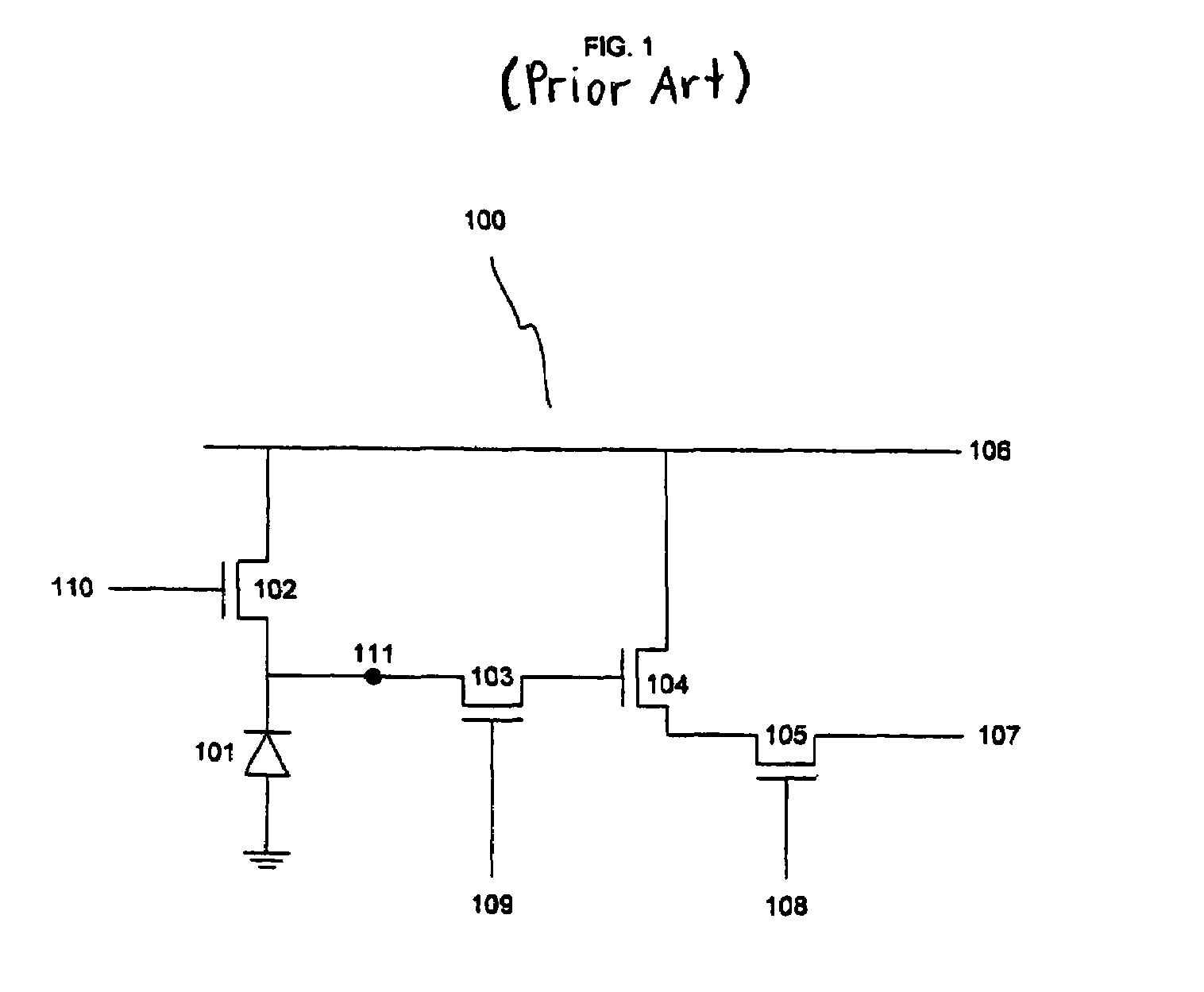

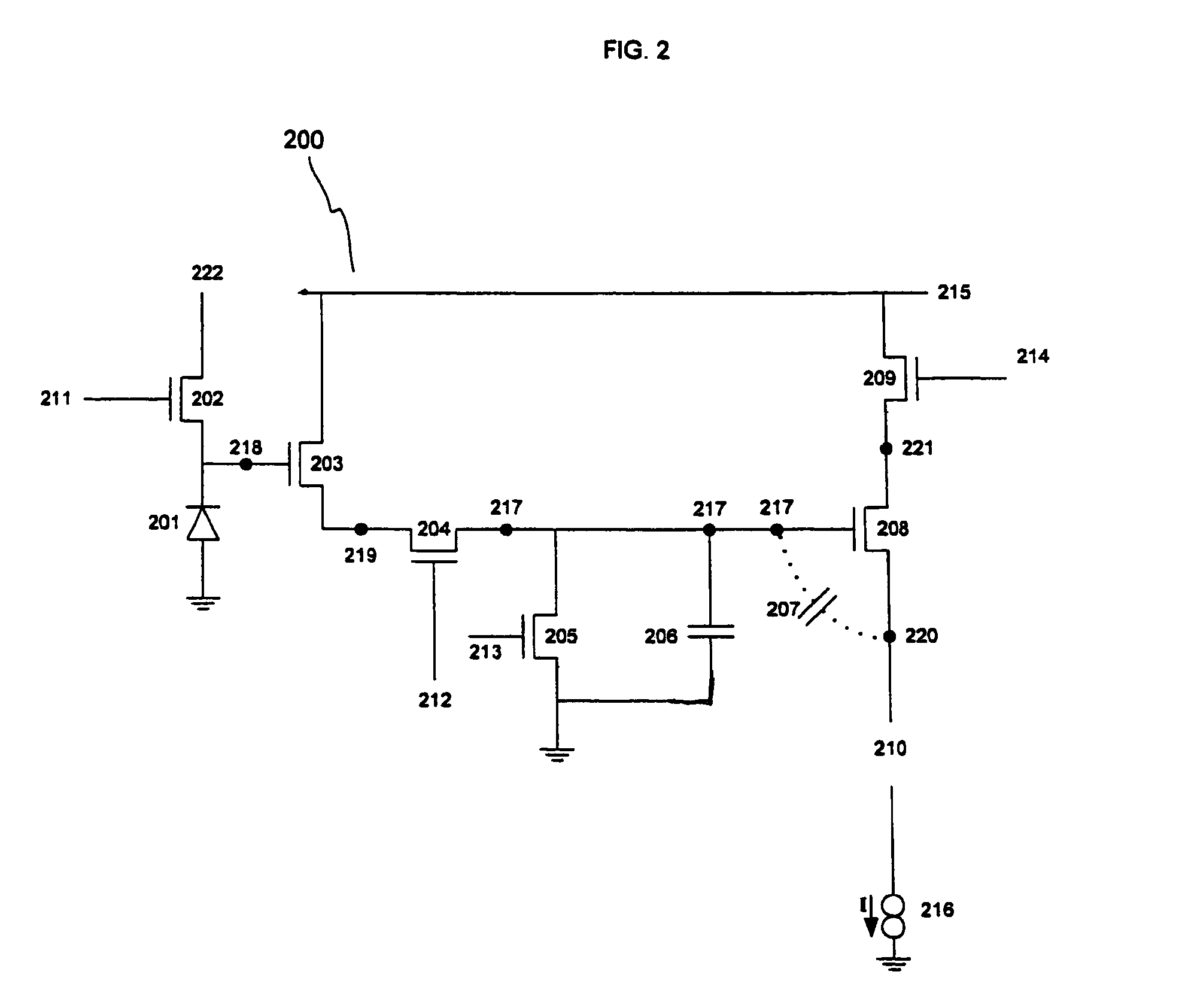

High isolation/high speed buffer amplifier

A method and circuits of a high isolation and high-speed buffer amplifier capable to handle frequencies in the GHz range have been achieved. The output to input isolation is primary dependent on the gate-source capacitance of the active buffer transistor. Having two or more in series and by reducing the impedance between them a high isolation can be achieved. The input signals are split in several signal paths and are amplified in the push-pull mode using source follower amplifiers. Then the amplified signals are being combined again. The amplified output current is mirrored applying a multiplication factor. Said method and technology can be used for buffer amplifiers having differential input and differential output or having single input and single output or having differential input and single output. A high reversed biased (output to input) isolation and a reduced quiescent current have been achieved.

Owner:DIALOG SEMICONDUCTOR GMBH

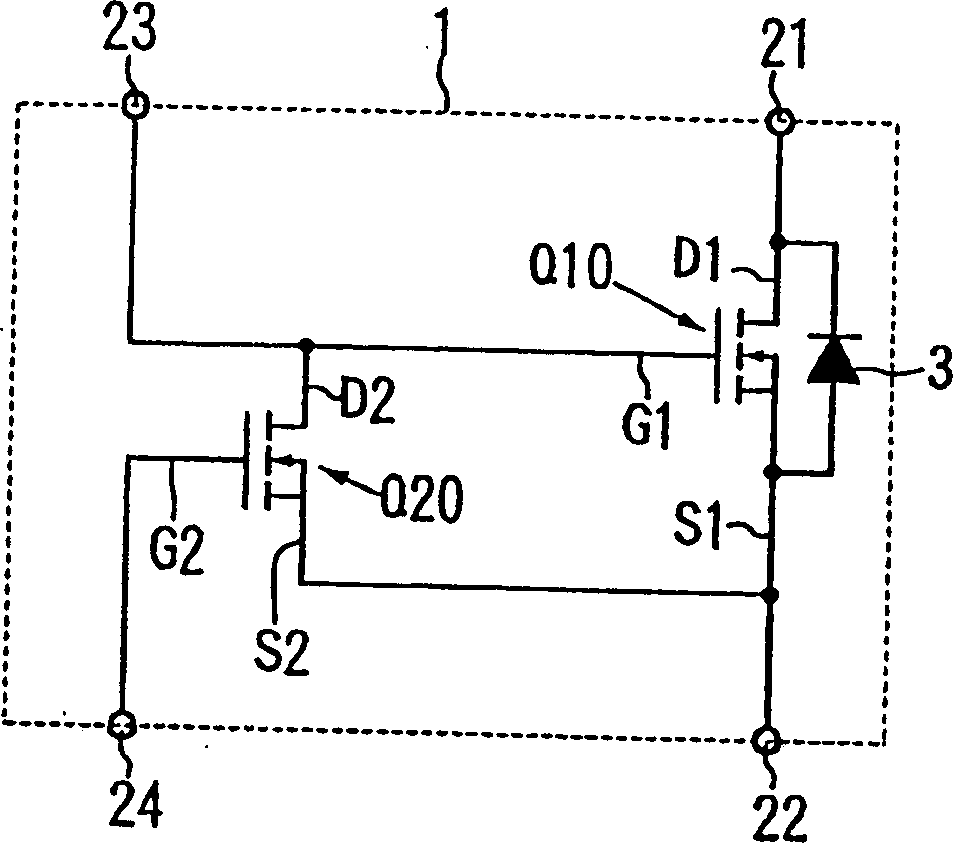

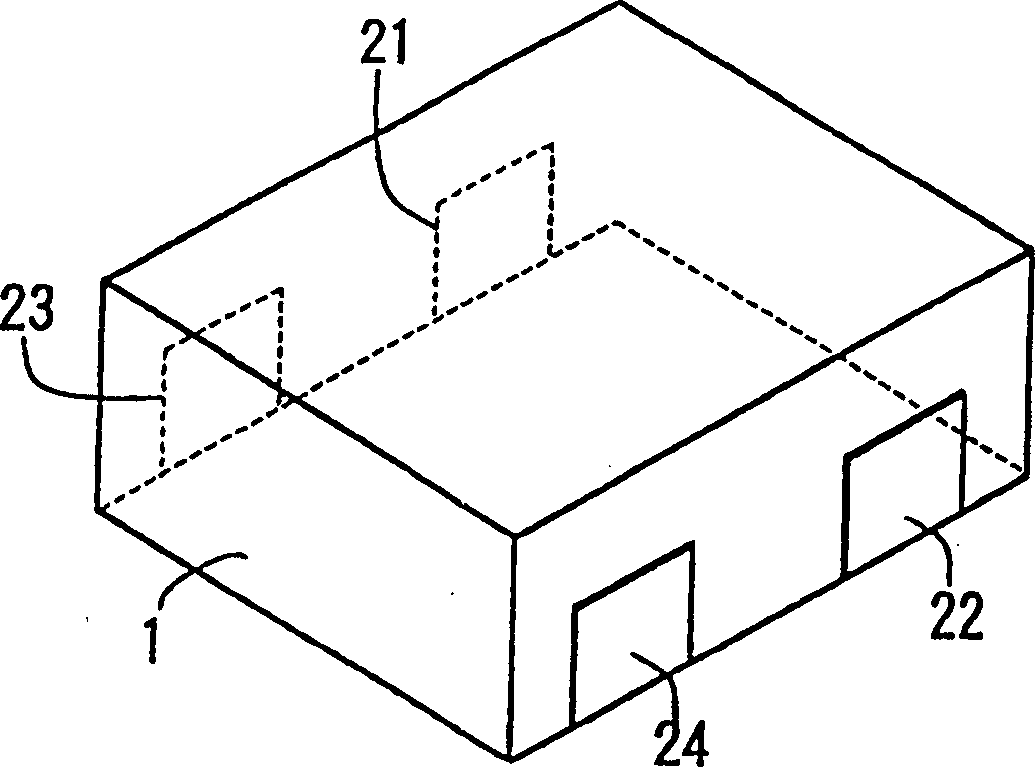

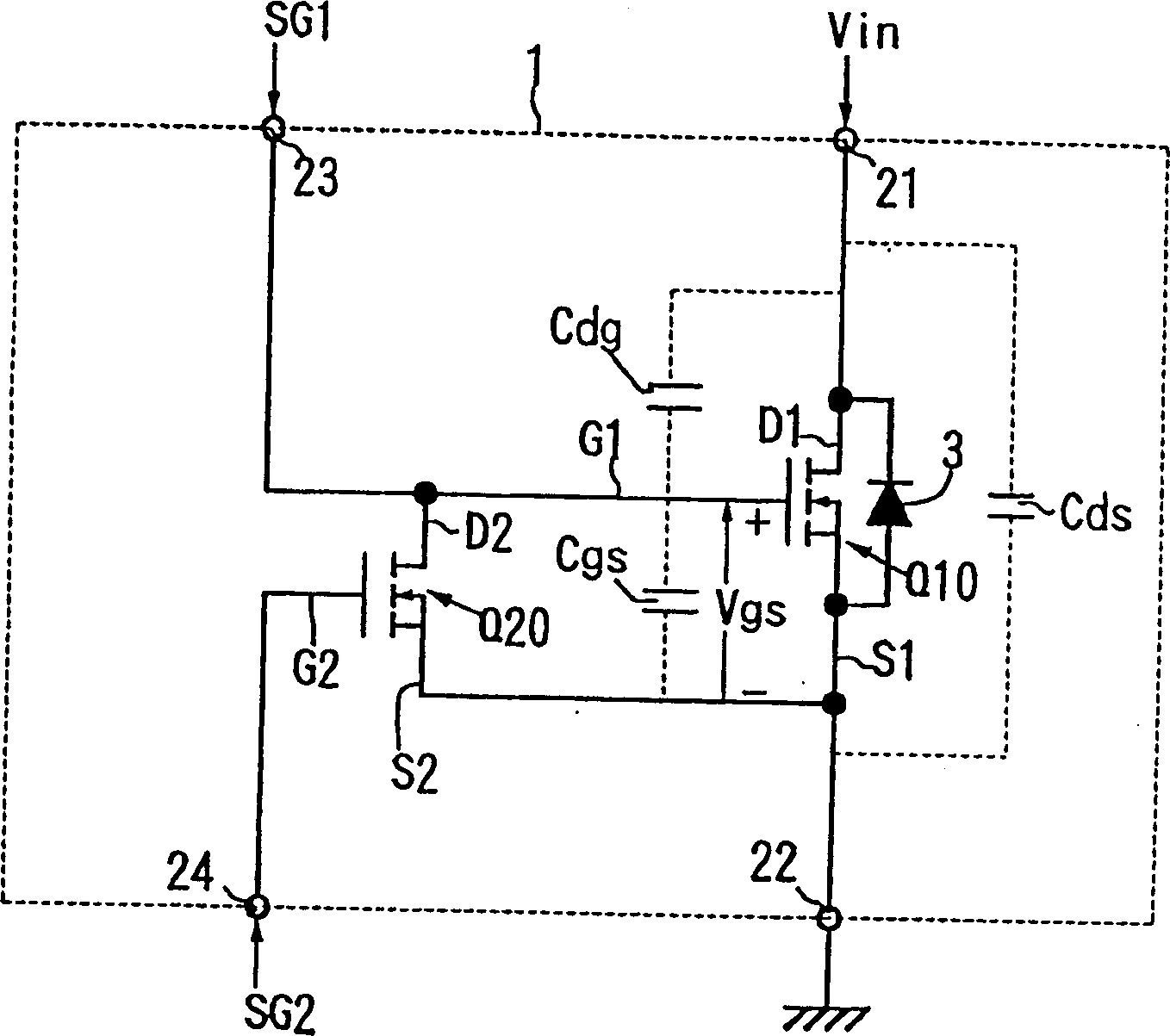

Semiconductor device

InactiveCN1378285ASmall sizeReduce component countTransistorAc-dc conversion without reversalGate source capacitanceEngineering

A semiconductor device capable of short-circuiting a gate-source capacitance of a FET (Field Effect Transistor) as a main switching device with low impedance is proposed. The above semiconductor device includes a first FET, a second FET, and a package. Both the first FET and the second FET are contained within the package. The first FET constitutes a main switching device. The drain and source of the second FET are connected to the gate and source of the first FET. An outer surface of the package has external terminals of the first and second FETs.

Owner:TDK CORPARATION

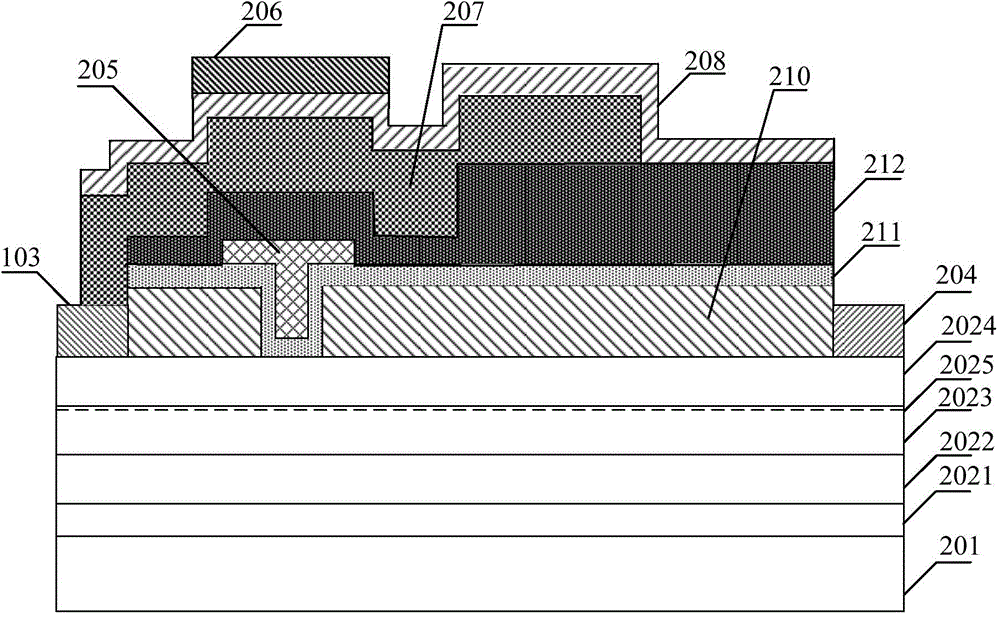

Semiconductor device and manufacturing method therefor

ActiveCN105633144AReduce leakageEffective electric field modulationSemiconductor/solid-state device manufacturingSemiconductor devicesGate source capacitanceSemiconductor

The invention provides a semiconductor device and a manufacturing method therefor. The device comprises a substrate, a semiconductor layer positioned on the substrate, a source electrode and a drain electrode positioned on the semiconductor layer, and a grid electrode positioned between the source electrode and the drain electrode, and a source field plate positioned on the semiconductor layer, wherein a groove is formed in the semiconductor layer between the grid electrode and the drain electrode; and the source field plate comprises a beginning part electrically connected with the source electrode, a first middle part, a second middle part covering the semiconductor layer between the grid electrode and the drain electrode, and a tail part, wherein air exists between the first middle part and the semiconductor layer, and between the tail part and the semiconductor layer. According to the semiconductor device, the overlay deviation between the groove and the source field plate can be eliminated, so that the production cost can be saved, and parasitic gate source capacitance and parasitic resistance are reduced as well.

Owner:DYNAX SEMICON

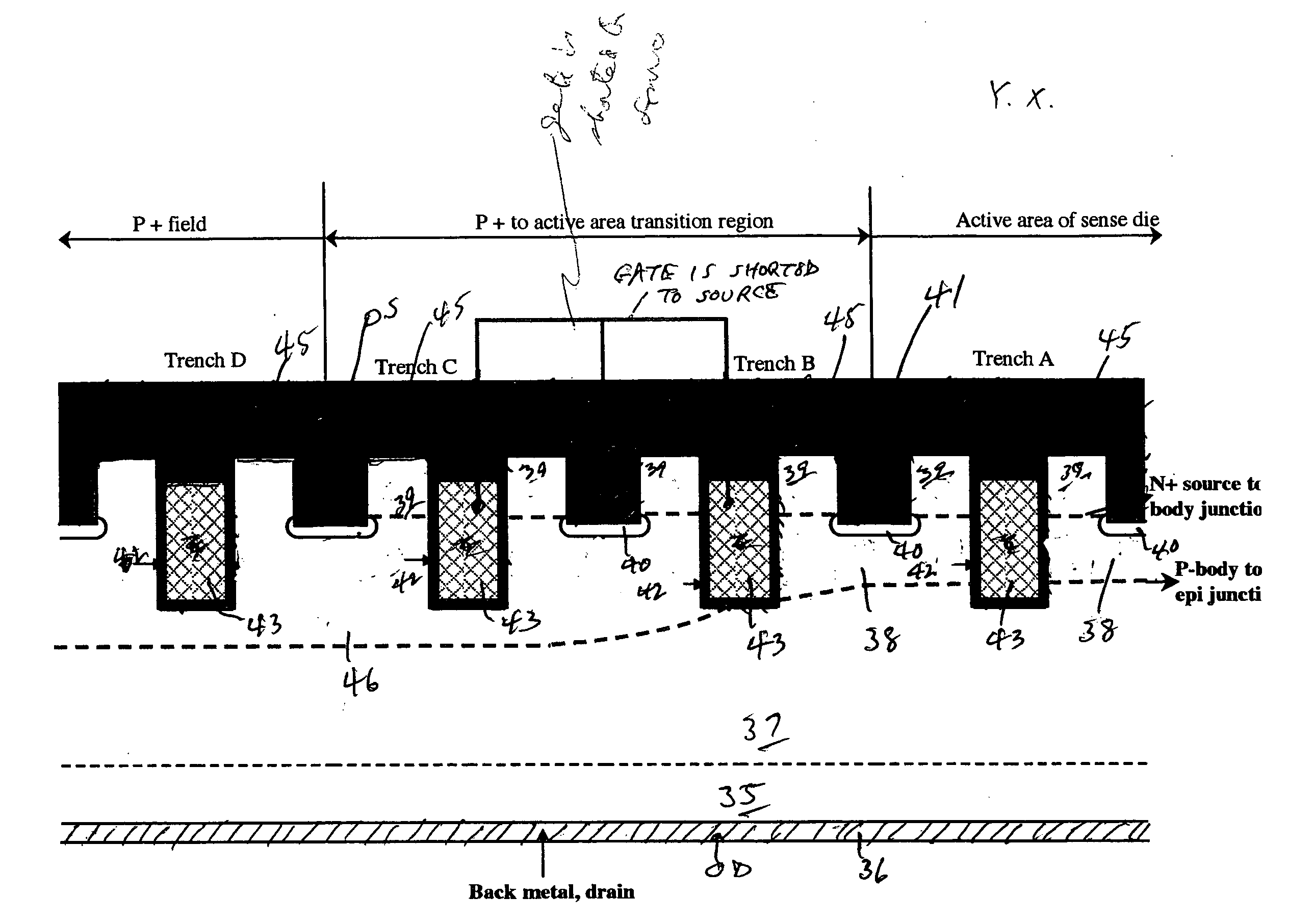

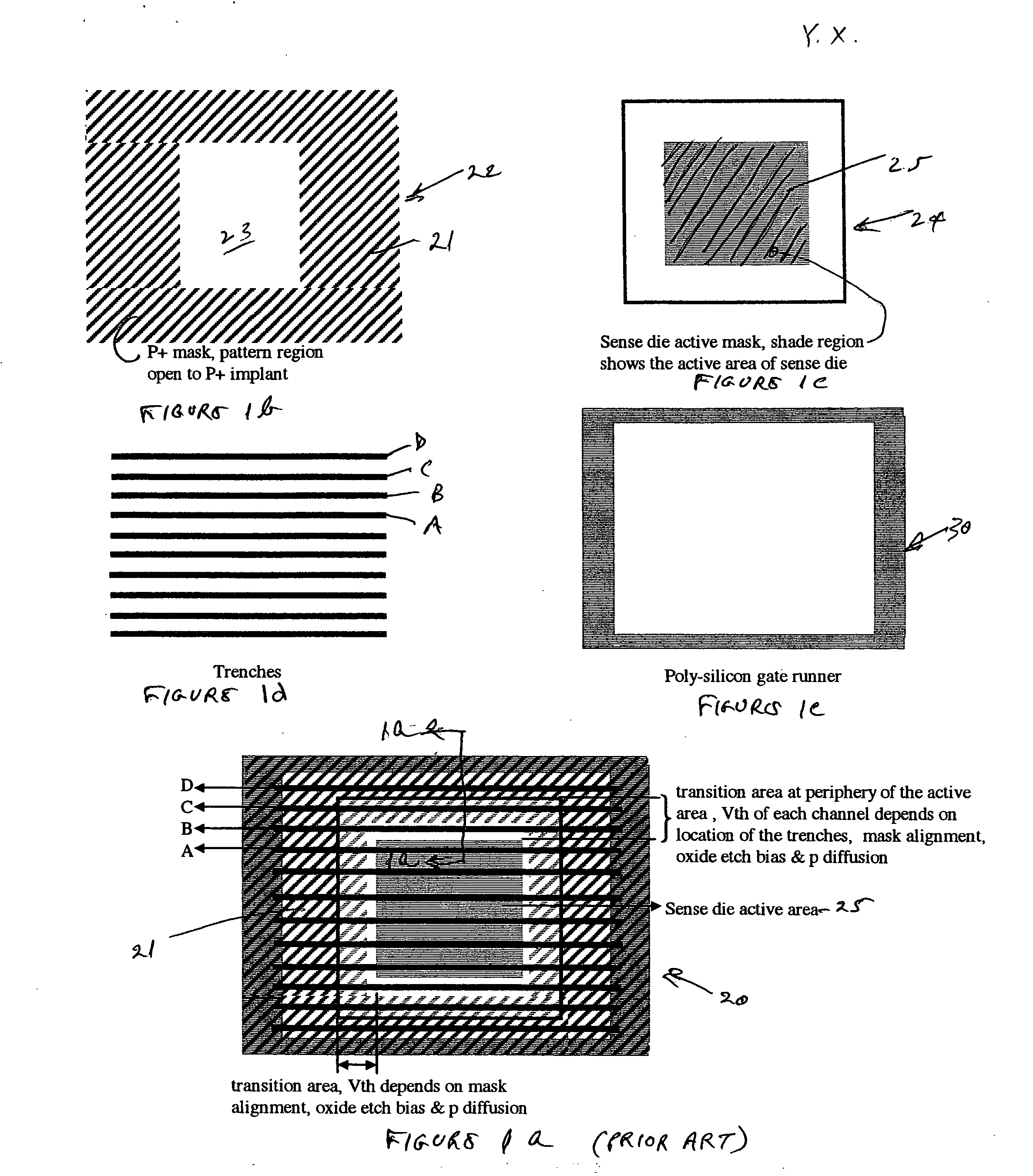

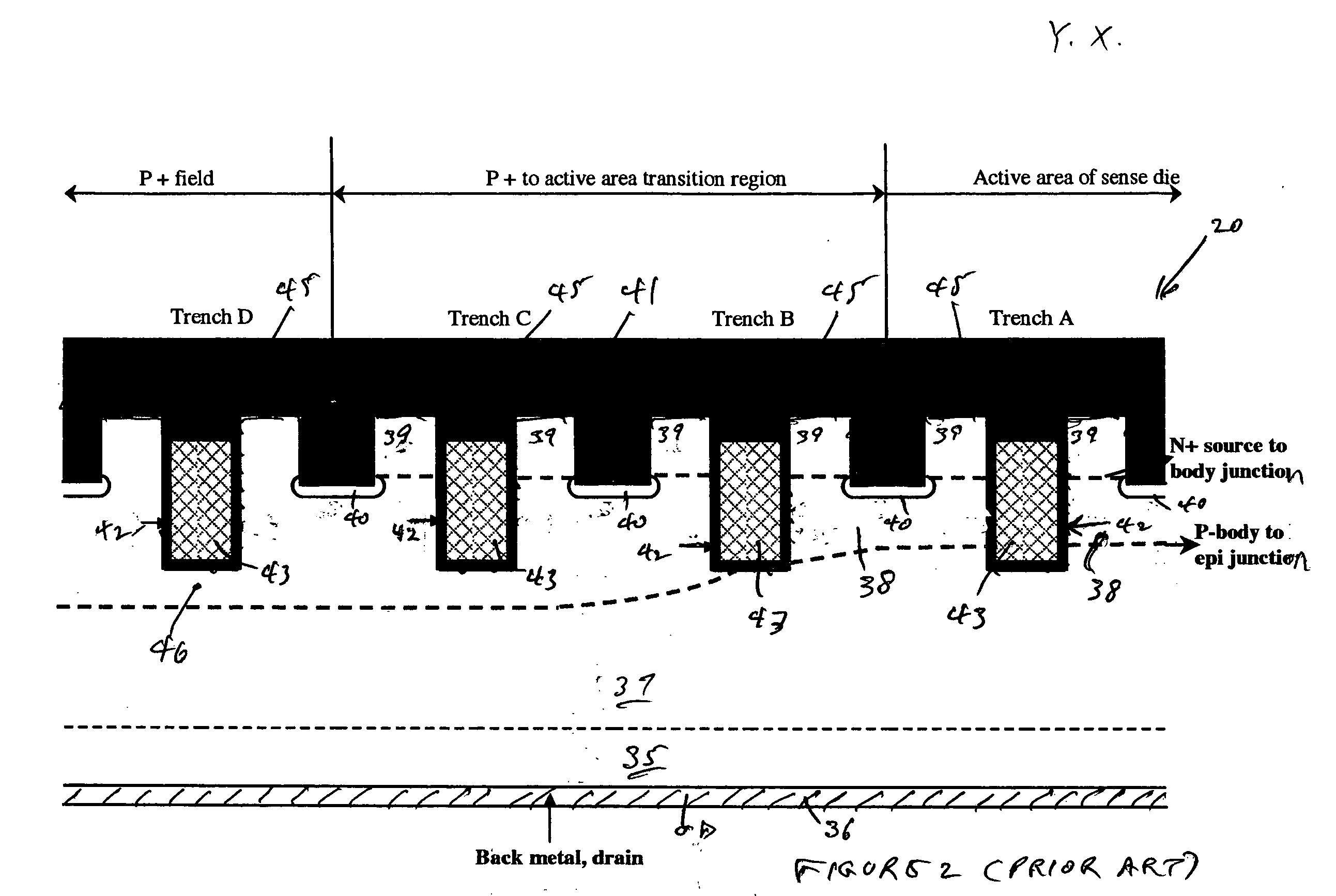

Current sense trench type MOSFET with improved accuracy and ESD withstand capability

ActiveUS20050174823A1Reduce variationTotal current dropStatic storageSemiconductor devicesMOSFETGate source capacitance

The active area of a current sense die is surrounded by a transition region which extends to the terminating periphery of the die. Spaced parallel MOSgated trenches extend through and define an active area. The trench positions in the transition region are eliminated or are deactivated, as by shorting to the MOSFET source of the trench, or by removing the source regions in areas of the transition region. By inactivating MOSgate action in the transition region surrounding the source, the device is made less sensitive to current ratio variation due to varying manufacturing tolerances. The gate to source capacitance is increased by surrounding the active area with an enlarged P+ field region which is at least five times the area of the active region, thereby to make the device less sensitive to ESD failure.

Owner:INFINEON TECH AMERICAS CORP

Array substrate and manufacturing method thereof and display device

InactiveCN105742295AReduce power consumptionReduce gapSolid-state devicesNon-linear opticsDisplay deviceGate source capacitance

The invention relates to an array substrate and a manufacturing method thereof and a display device. The array substrate comprises a substrate, common electrodes, multiple rows of grid lines and multiple pixel electrodes, wherein the common electrodes, the multiple rows of grid lines and the multiple pixel electrodes are formed on the substrate; the pixel electrodes and the common electrodes are arranged at different layers; a vertical overlap part exists in each pixel electrode and the corresponding common electrode; and in two pixel electrodes connected to the same row of grid lines, the area of the vertical overlap part of the pixel electrode which is further to the first ends of the grid lines and the corresponding common electrode is smaller than that of the pixel electrode which is nearer the first ends of the grid lines and the corresponding common electrode. According to the array substrate, the leaping voltage of the pixel electrode further to the first ends of the grid lines obtains more compensation than that nearer the first ends of the grid lines, so that the difference between the leaping voltages of two pixel electrodes is reduced; the residual image is reduced. Furthermore, compared with the mode of increasing a gate-source capacitance in the prior art, the array substrate has the advantage that the power consumption of the array substrate can be reduced.

Owner:BOE TECH GRP CO LTD

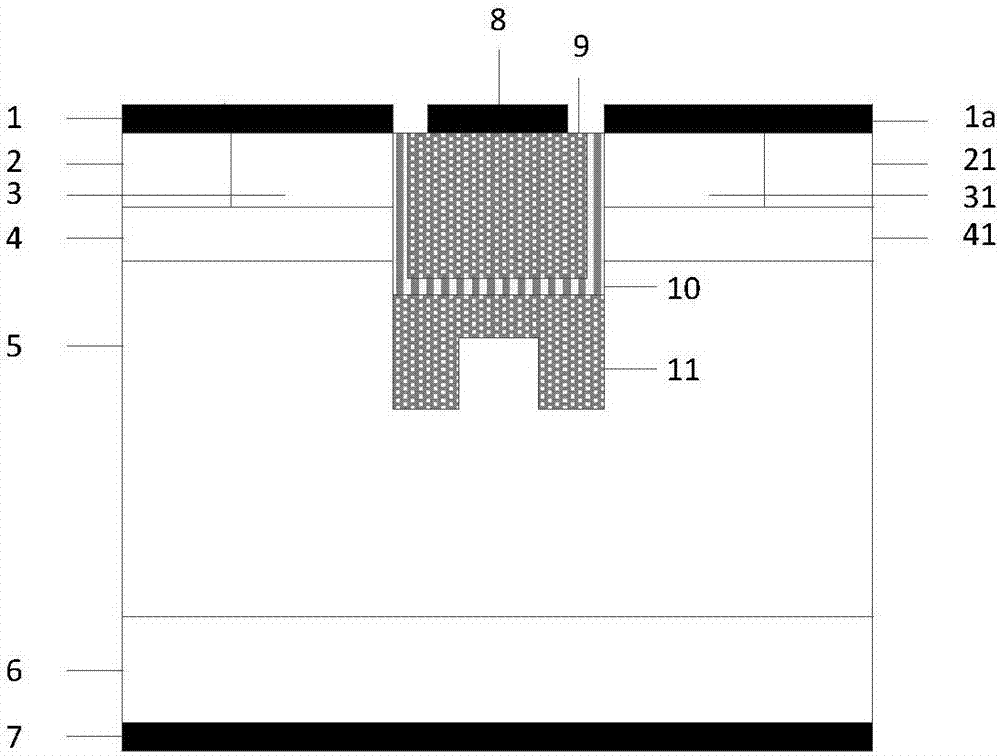

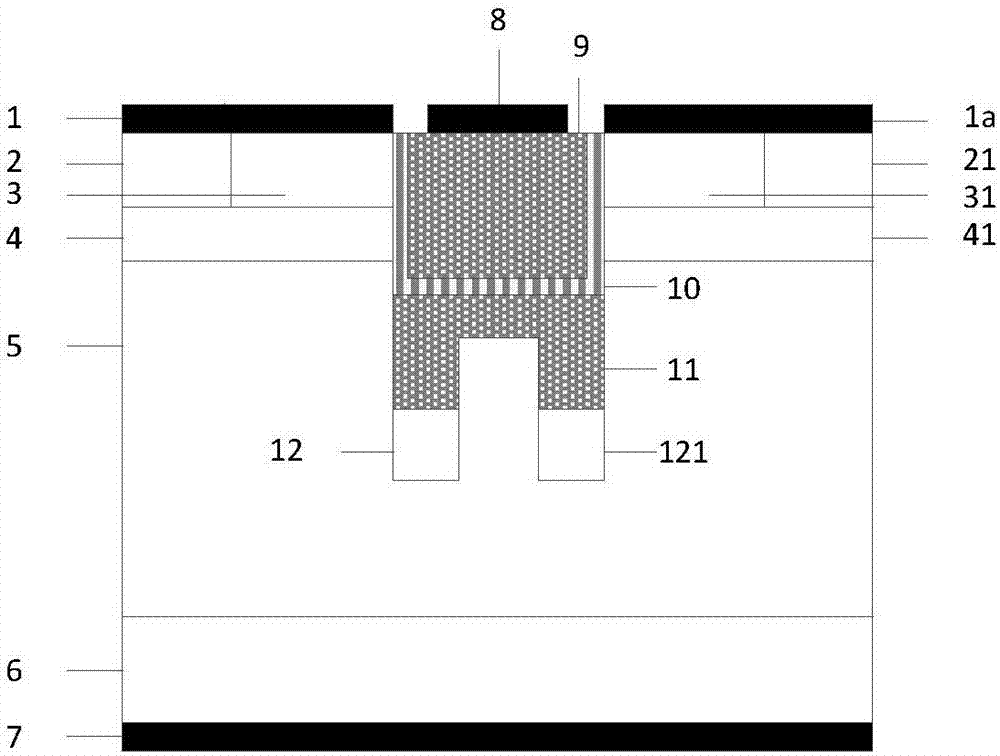

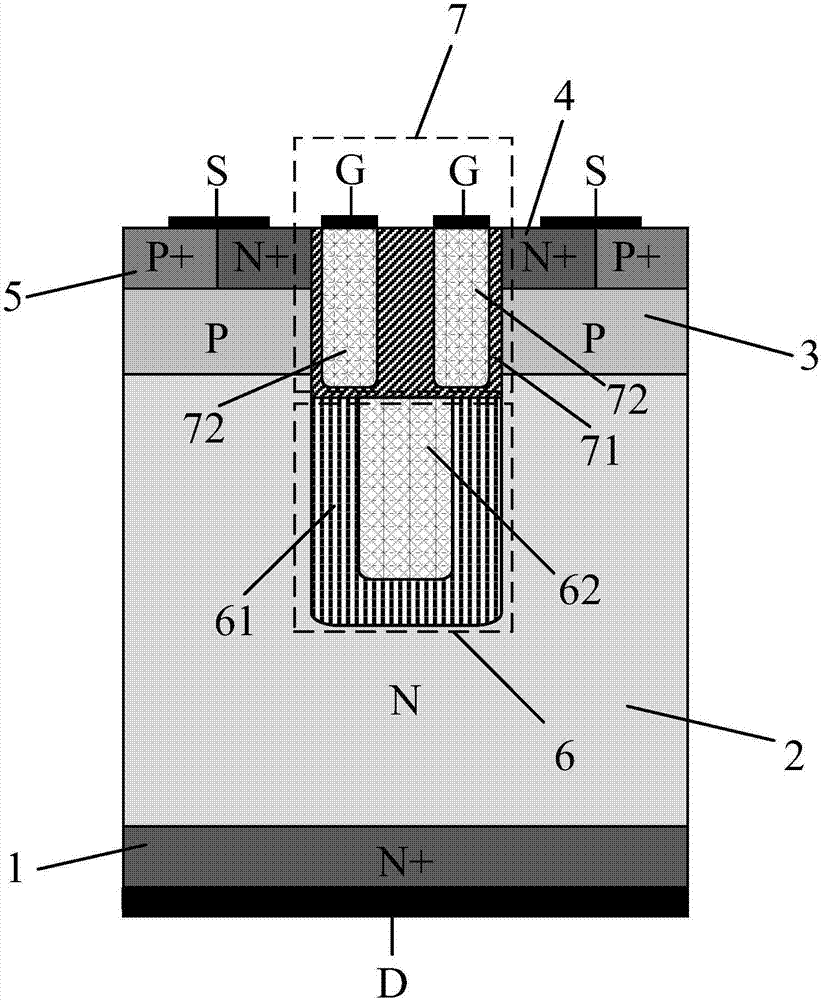

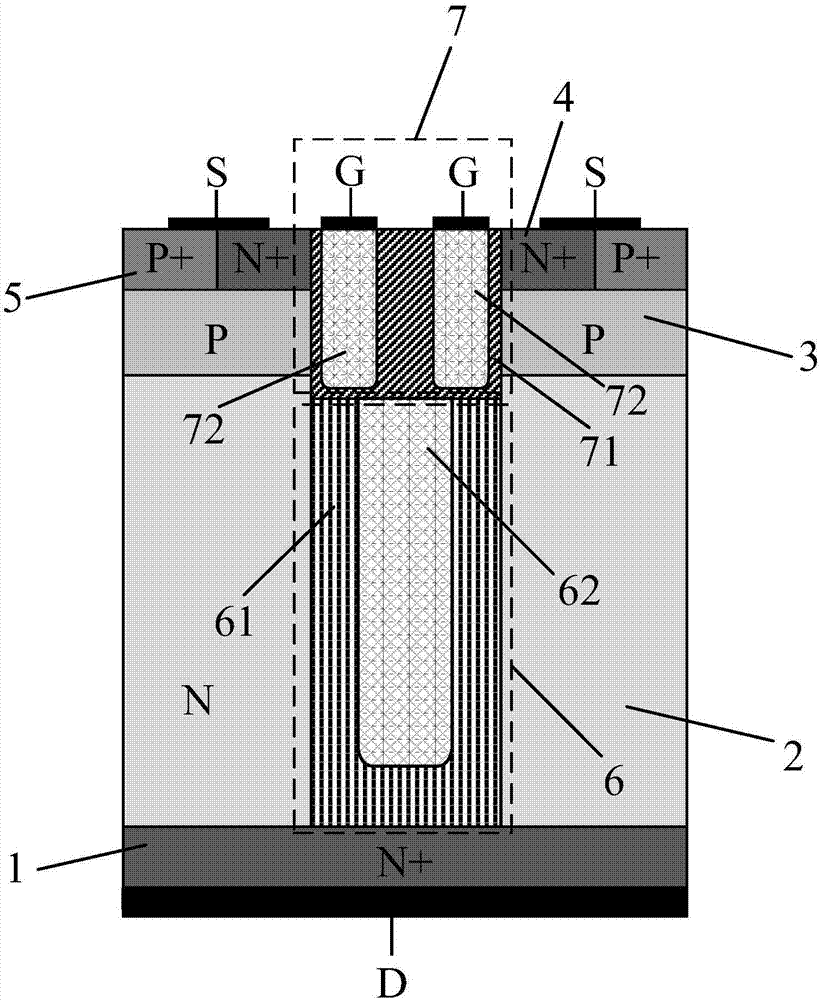

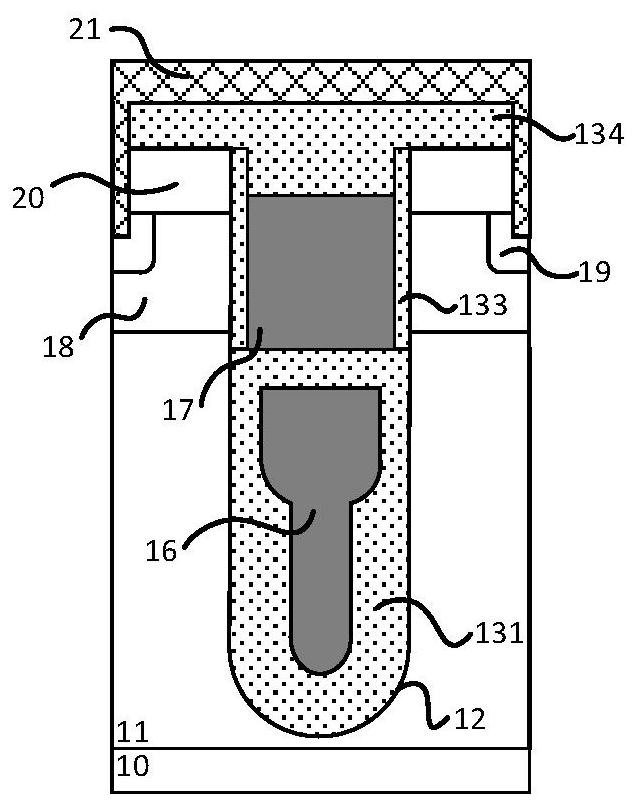

Silicon carbide Trench MOS device and manufacturing method thereof

ActiveCN107425068AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionReverse recovery

The invention discloses a silicon carbide Trench MOS device and a manufacturing method thereof, and belongs to the technical field of power semiconductors. The method includes: a layer of a polysilicon region distributed in a pi shape is additionally arranged under a trench gate structure of a conventional device, the polysilicon region and an epitaxial layer form a Si / SiC heterojunction, and a diode is integrated in the device. Compared with a parasitic silicon carbide diode which directly employs a silicon carbide Trench MOS, according to the silicon carbide Trench MOS device and the manufacturing method thereof, the junction voltage drop of the device diode during application is substantially reduced, and the switch-on characteristic of the device is improved through large junction area of the heterojunction; moreover, the gate-drain capacitance and the ratio of the gate-drain capacitance to the gate-source capacitance of the device are reduced, and the performance and the reliability of the device MOS during application are enhanced; besides, the silicon carbide Trench MOS device and the manufacturing method thereof are also advantageous in that the reverse recovery time is short, the reverse recovery charges are less, and advantages including low reverse leakage, high breakdown voltage, and good temperature stabilization performance of the conventional silicon carbide Trench MOS device are maintained. In conclusion, according to the silicon carbide Trench MOS device and the manufacturing method thereof, the prospect is wide in circuits such as inversion circuits and chopper circuits etc.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

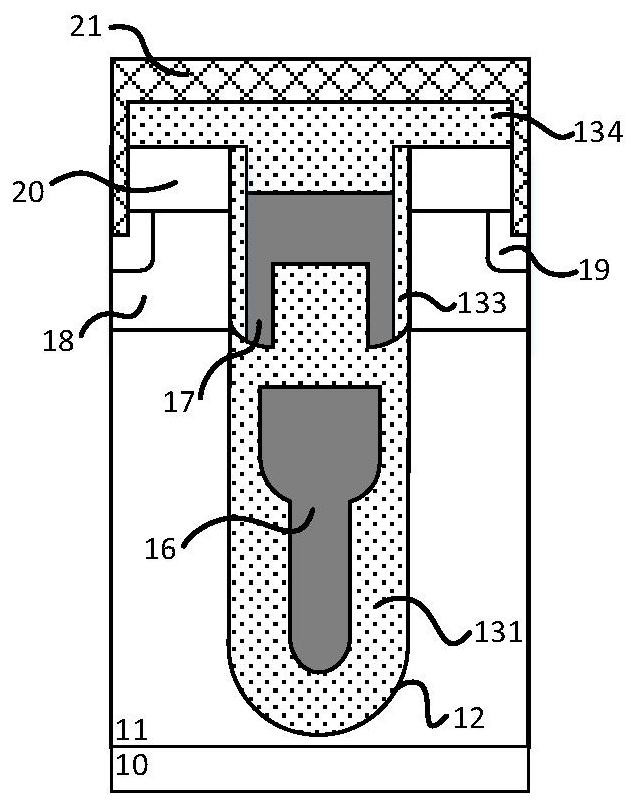

Shield gate trench power device and manufacturing method thereof

ActiveCN111883592ALower on-resistanceIncreasing the thicknessEfficient power electronics conversionSemiconductor/solid-state device manufacturingGate dielectricEngineering

The invention discloses a shield gate trench power device. A gate structure of a device unit region comprises a shielding dielectric layer formed on the inner side surface of a gate trench; the shielding dielectric layer is formed by superposing a thermal oxidation layer and a CVD dielectric layer; active polycrystalline silicon is filled in a gap region formed by filling the shielding dielectriclayer; top trenches formed by etching part of the shielding dielectric layer close to the side surface of the gate trench are formed in two sides of the source polysilicon, and the top trenches are completely located in the thermal oxide layer; the shielding dielectric layer between the second side surface of the top trench and the source polysilicon is used as an inter-polysilicon dielectric layer; the top trench is filled with a polysilicon gate, and a gate dielectric layer is formed on the first side surface of the top trench. The invention further discloses a manufacturing method of the shield gate trench power device. According to the invention, the thickness uniformity of the side wall and the bottom shielding dielectric layer of the trench can be improved, so the voltage resistanceof the device can be ensured, the on resistance of the device can be reduced, and the gate-source capacitance of the device can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

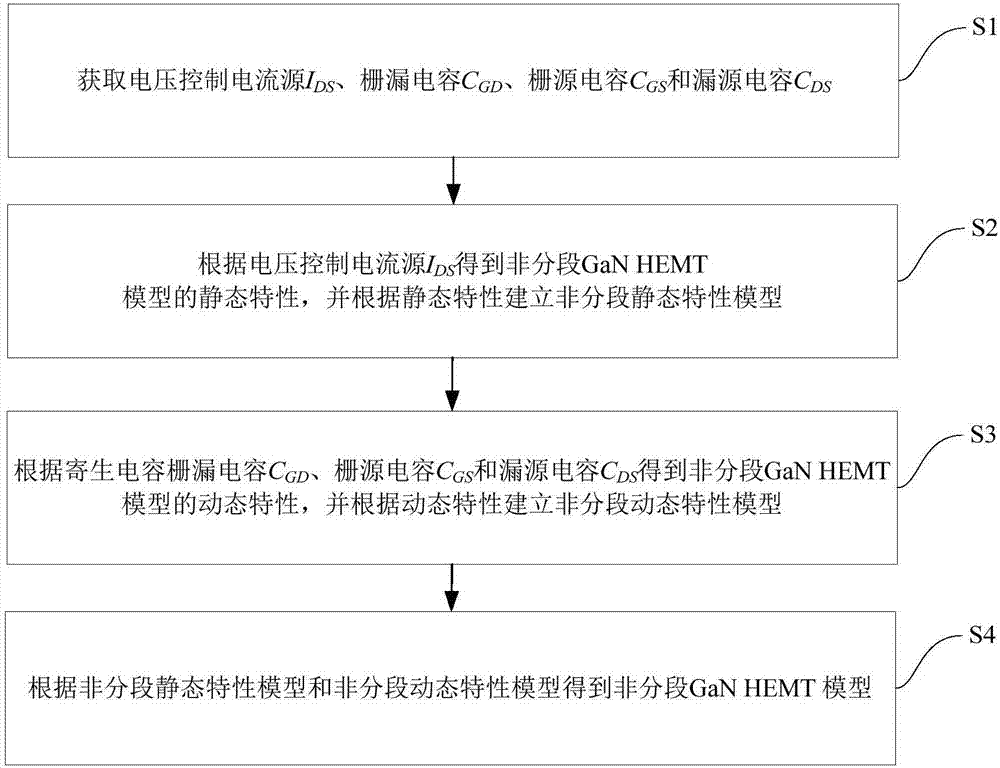

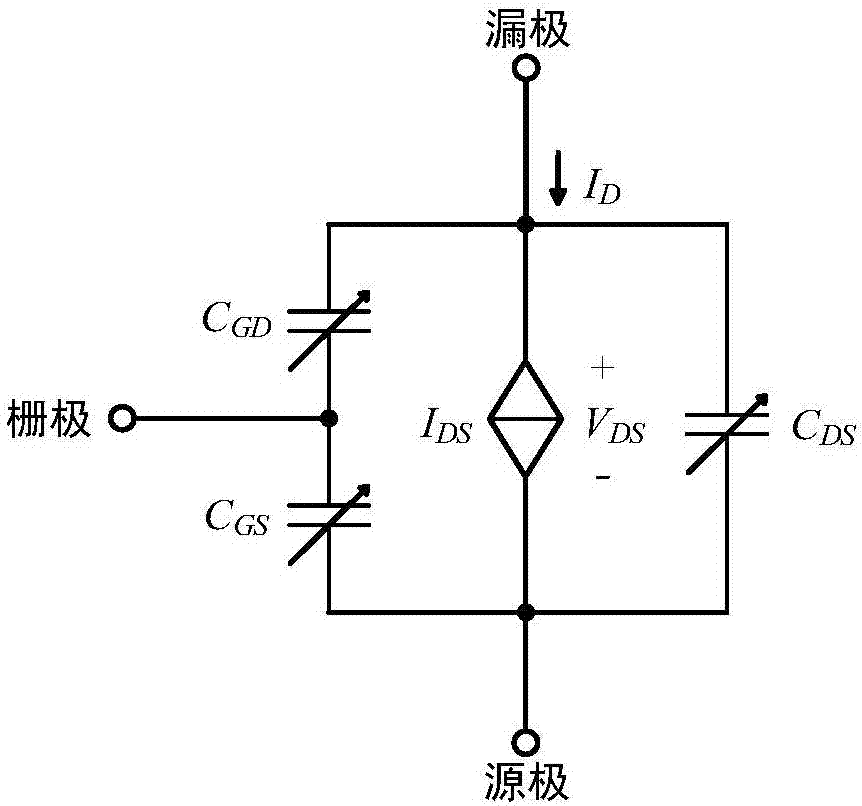

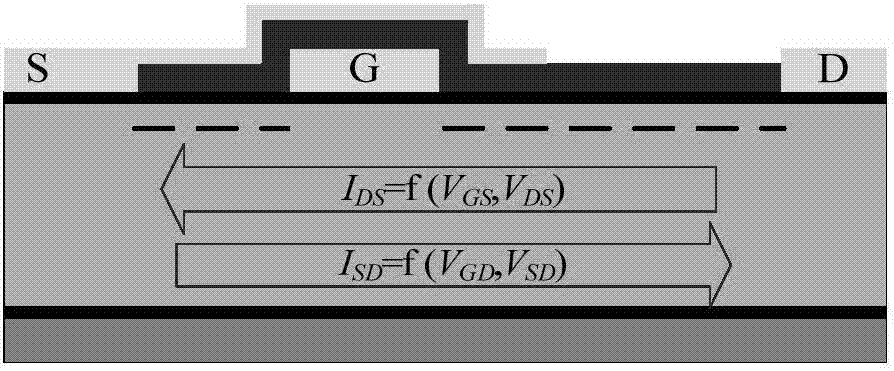

Establishing method for non-sectioned GaN HEMT model

ActiveCN107103122AFast convergenceImprove accuracySpecial data processing applicationsEngineeringGate source capacitance

The invention provides an establishing method for a non-sectioned GaN HEMT model. The establishing method includes the steps that a voltage control current source I<DS>, gate-drain capacitance C<GD>, gate source capacitance C<GS> and drain-source capacitance C<DS> are obtained; the static characteristics of the non-sectioned GaN HEMT model are obtained according to the I<DS>, and a non-sectioned static-characteristic model is established according to the static characteristics; the dynamic characteristics of the non-sectioned GaN HEMT model are obtained according to the C<GD>, the C<GS> and the C<DS>, and a non-sectioned dynamic-characteristic model is established according to the dynamic characteristics; the non-sectioned GaN HEMT model is obtained according to the non-sectioned static-characteristic model and the non-sectioned dynamic-characteristic model. By means of the establishing method, the non-sectioned GaN HEMT model with the good convergence performance and the high accuracy can be obtained, and is further better applied to power electronic circuit simulation, and meanwhile designing and analysis of a following power converter are more convenient and efficient.

Owner:BEIJING JIAOTONG UNIV

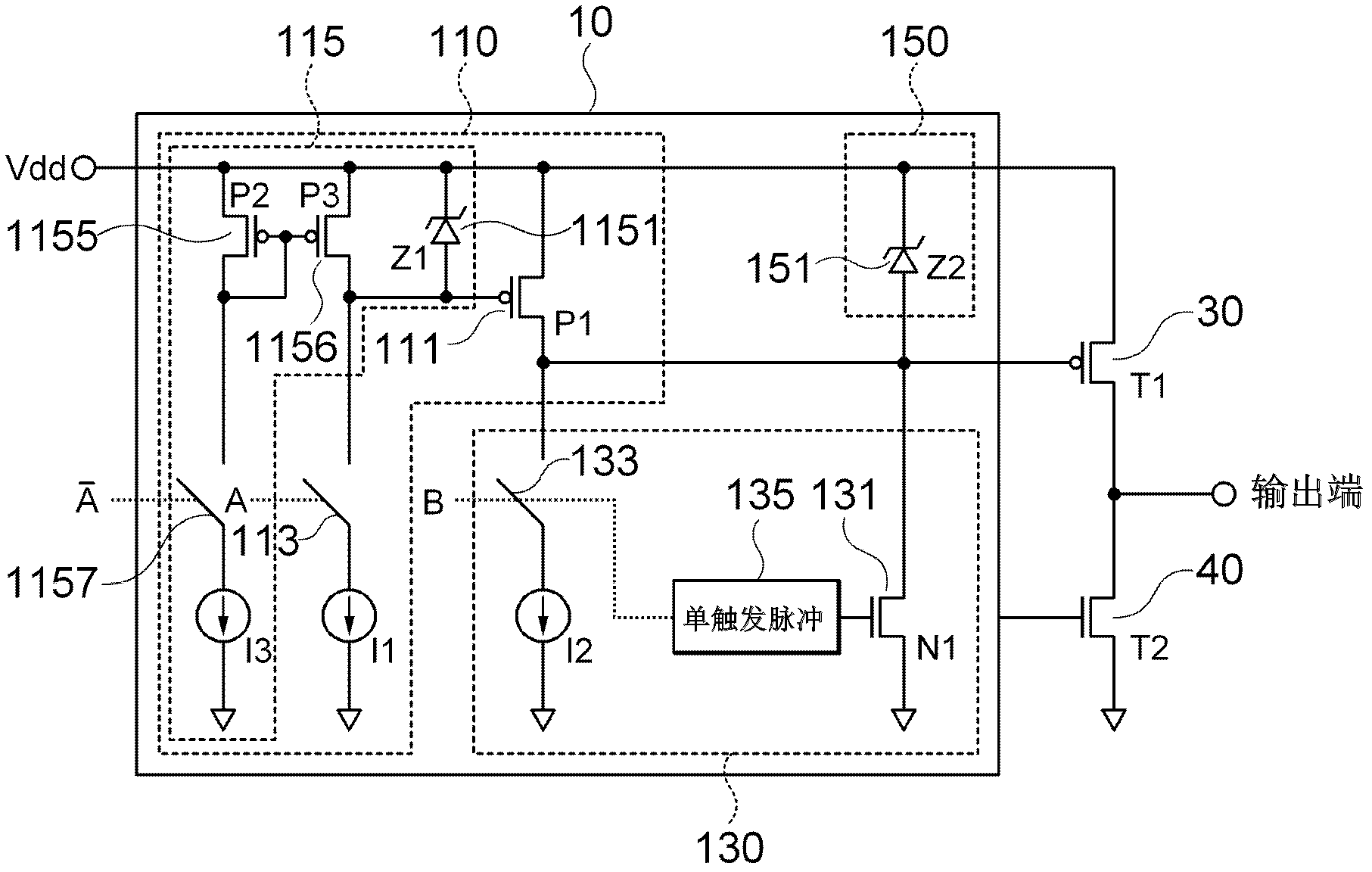

CMOS imager with wide dynamic range pixel

InactiveUS7411168B2Small sizeAdditional circuitryTelevision system detailsTelevision system scanning detailsCMOS sensorEngineering

In one aspect of the present invention, a light sensor is provided in the active pixel sensor cell for sensing incident radiation. The voltage corresponding to the photon-generated or other radiation-generated charge in the active pixel sensor cell is stored on a storage node via a sample-and-hold capacitor. Additional elements, such as source-follower transistors, may reside between the sensing element and the sample-and-hold capacitor. The signal is read via a readout source-follower (RSF) transistor. The readout source-follower drain is connected to the row select switch while its drain is connected to the output node on the column output bus. This configuration couples the storage node to the gate-source capacitance of the readout source-follower transistor. This allows the voltage on the storage node to increase proportionally to the increase in voltage on the readout node when the row select is closed and thus enables the drain current to flow through the RSF to the column output bus.

Owner:IMAGERLABS

Semiconductor device and fabrication method thereof

ActiveCN108767009AGate-to-source capacitance increasesSolving Drain-Source CapacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceGate source capacitance

The invention provides a semiconductor device and a fabrication method thereof, and relates to the technical field of semiconductors. By introducing a second dielectric layer with a higher dielectricconstant between two pole plates forming a gate-source capacitor, the gate-source capacitance of the semiconductor device is improved, the problem that a drain-source capacitor of the semiconductor device is mismatched with drain-source capacitors of other semiconductor devices cascaded with the semiconductor device is solved, an external capacitor is not needed to be connected in parallel betweena source and a drain of the semiconductor device, the complexity of the circuit and the volume of the semiconductor device can be reduced, and the reliability of the semiconductor can be improved; and by introducing the high-dielectric constant material between the two pole plates forming the gate-source capacitor, the electrostatic resistant capability of the device can be improved.

Owner:GPOWER SEMICON

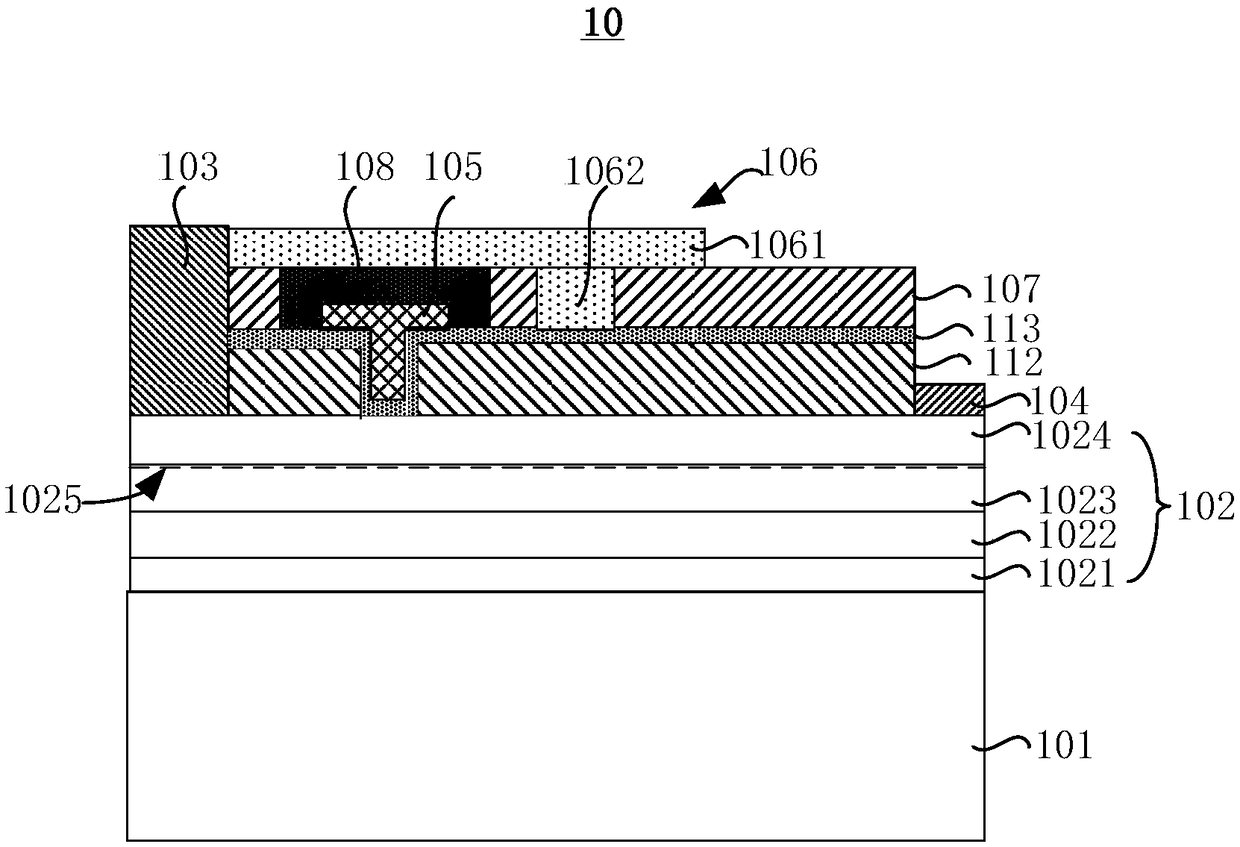

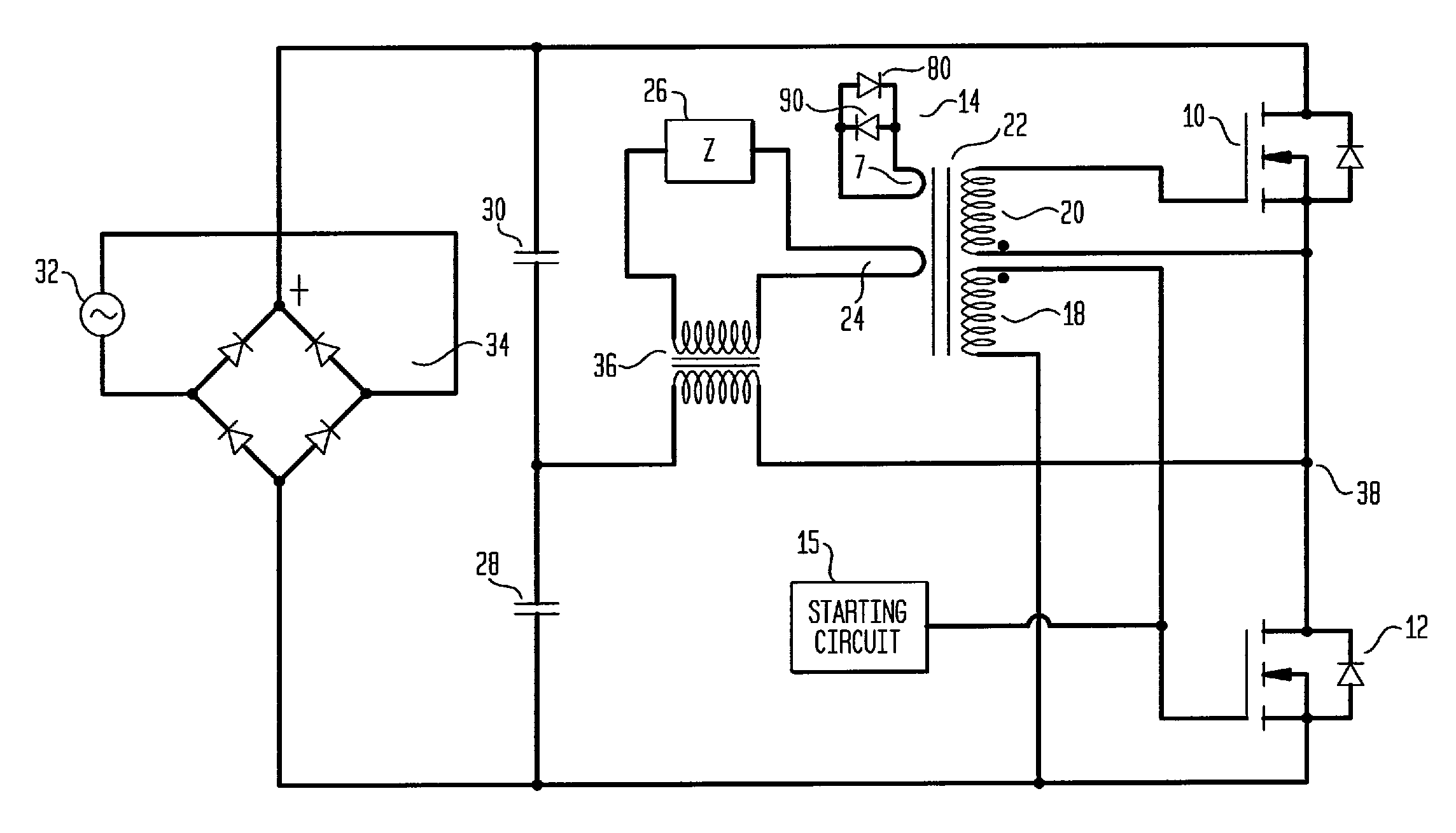

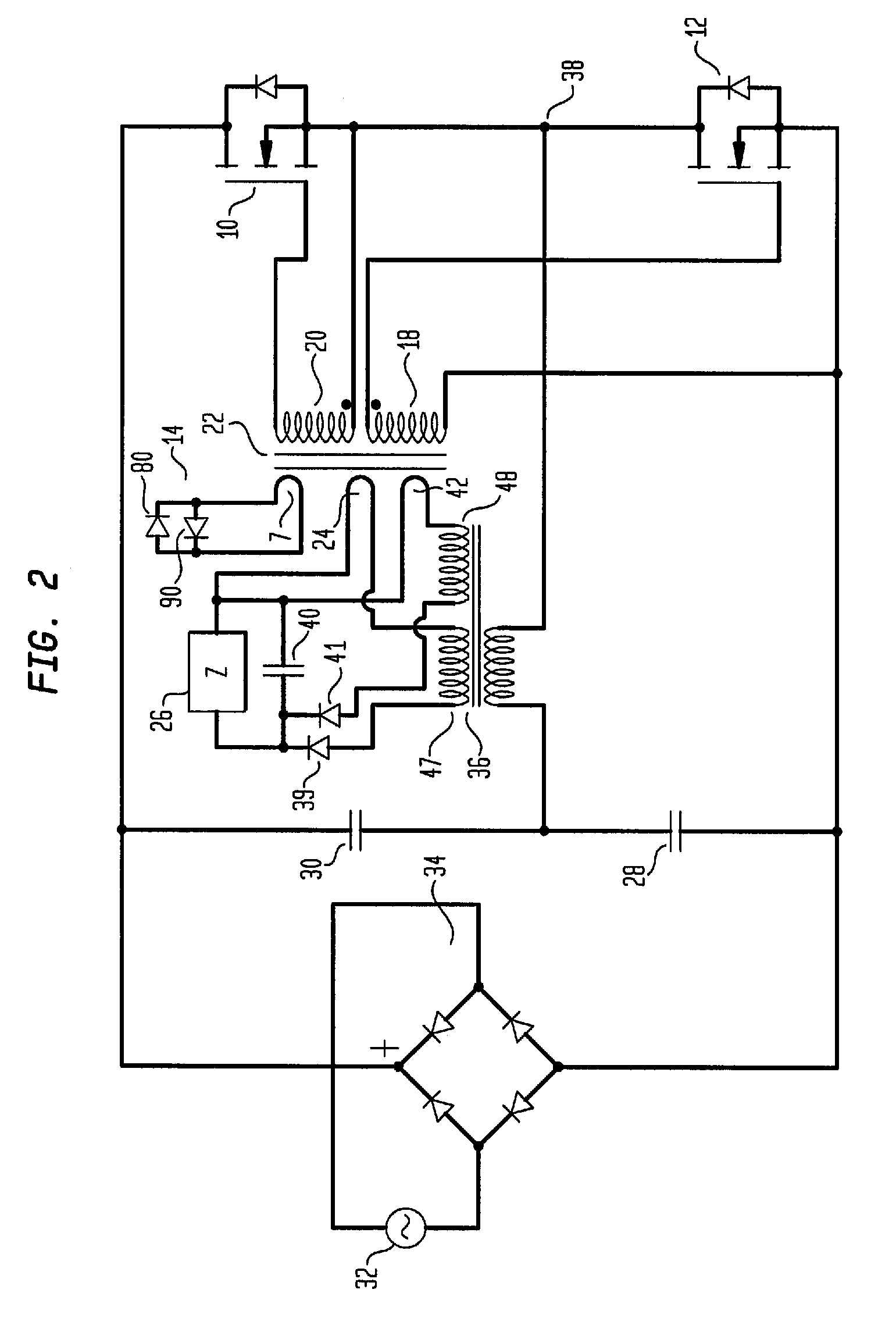

Adaptive resonant switching power system

InactiveUS7362594B2Minimize power consumptionSmall and efficient switching power transformerEfficient power electronics conversionAc-dc conversionOutput transformerMOSFET

A resonant switching power system operates with two resonant frequencies. A first frequency depends on the secondary leakage inductance of an output transformer and capacitor. The first frequency varies with changes in the load because load changes alter the leakage inductance. A second resonant frequency depends on the gate source capacitance of two MOSFET power devices in the circuit and the leakage inductance of the circuit's driving transformer. Power is thereby supplied that is always in phase with the load so that switching in the power supply occurs when current is near zero. High thermal efficiency is thereby achieved.

Owner:APOGEE TECH

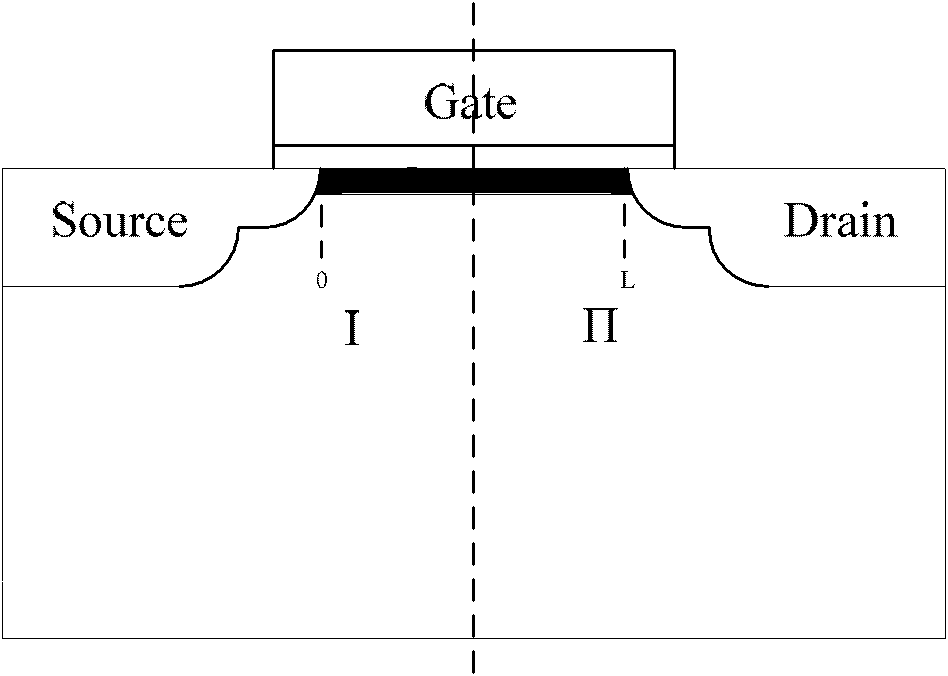

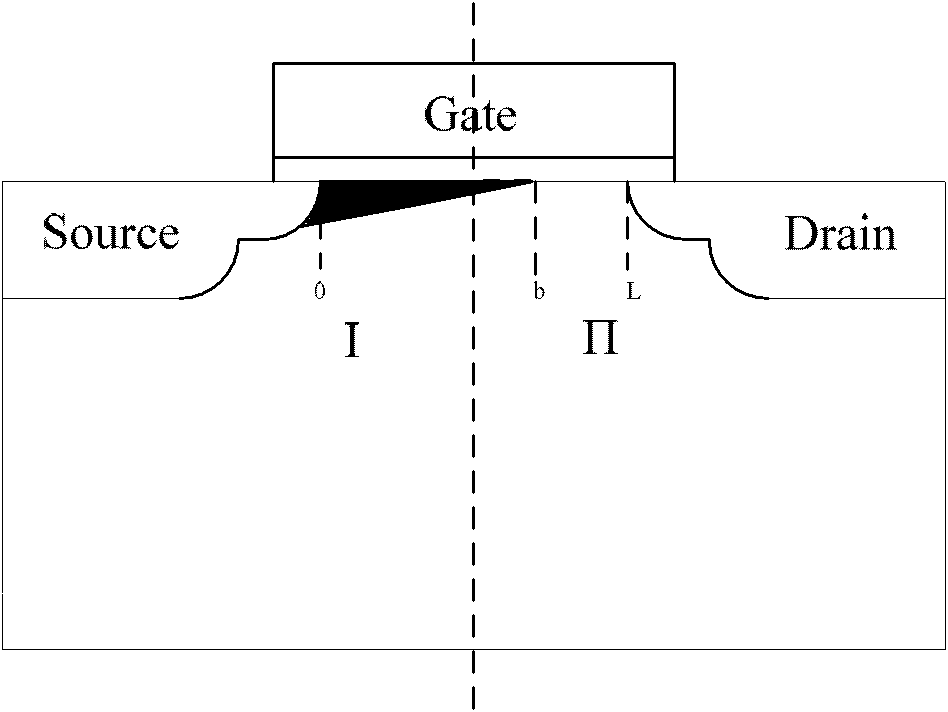

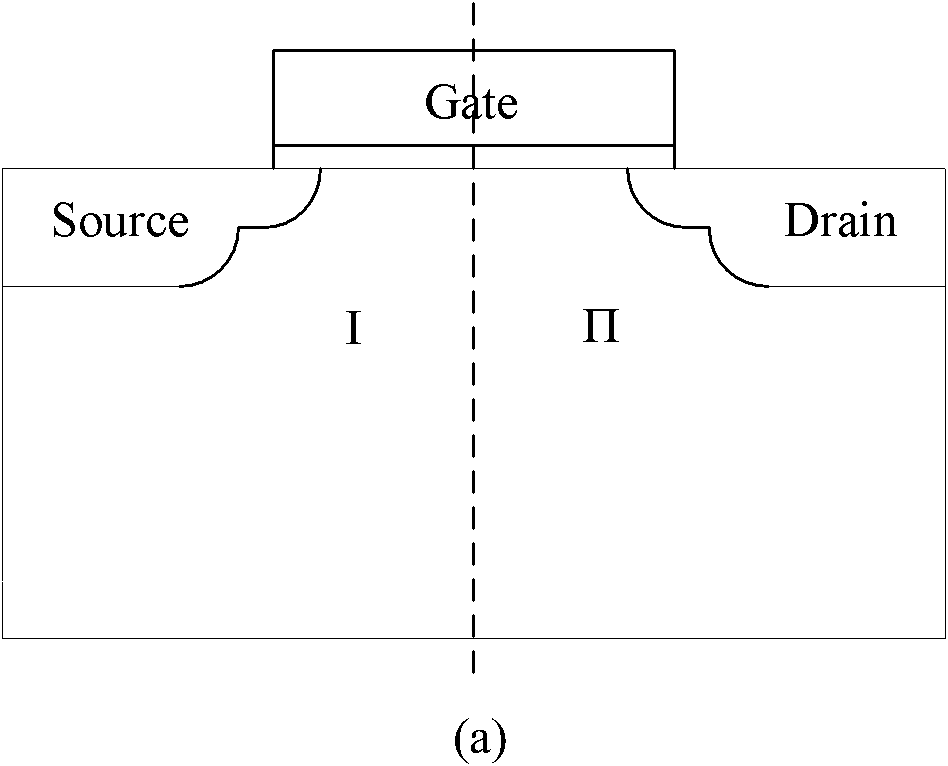

Estimation method of the relative position of the radiation displacement damage area in the coms device in the channel

The invention discloses a method for estimating relative position of a radiation displacement damage area of a COMS (Complementary Metal Oxide Semiconductor) device in a channel. In the method, the groove of the CMOS device is partitioned into two parts; a part close to a source end is an area I; and a part to a drain end is an area II. When the situation after radiation is compared with the situation before radiation, the radiation displacement damage area is in the area I if the gate source capacitance is decreased while the gate drain capacitance is increased; and the radiation displacement damage area is in the area II if the gate source capacitance is increased while the gate drain capacitance is decreased. Specific to the CMOS device, relative position of the radiation displacement damage area in the groove is represented according to the change of intrinsic capacitance before and after radiation. The method is simple, is easy to operate, and plays a great role in researching single particles, modeling single particles and reinforcing integrated circuits; and a thought for determining the position of the radiation displacement damage area on the CMOS device is provided.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

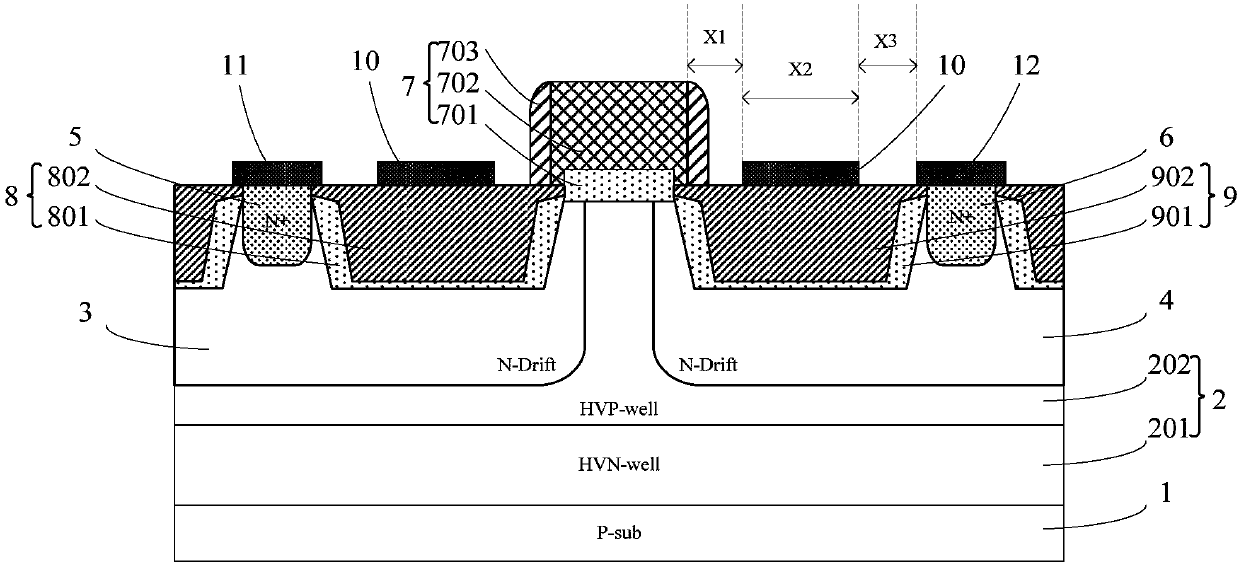

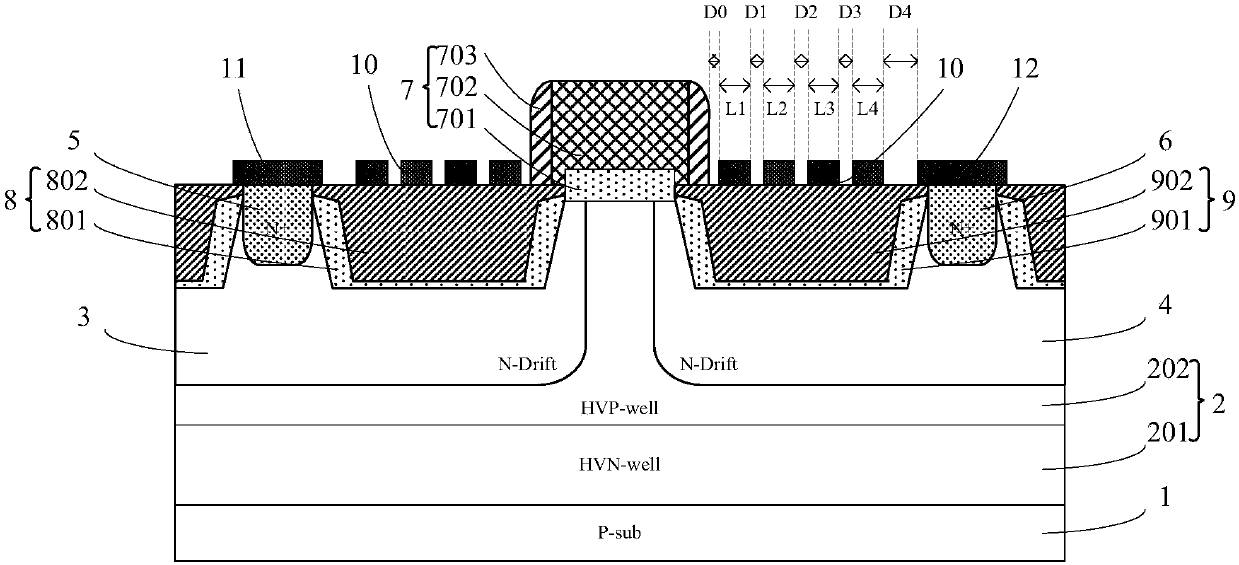

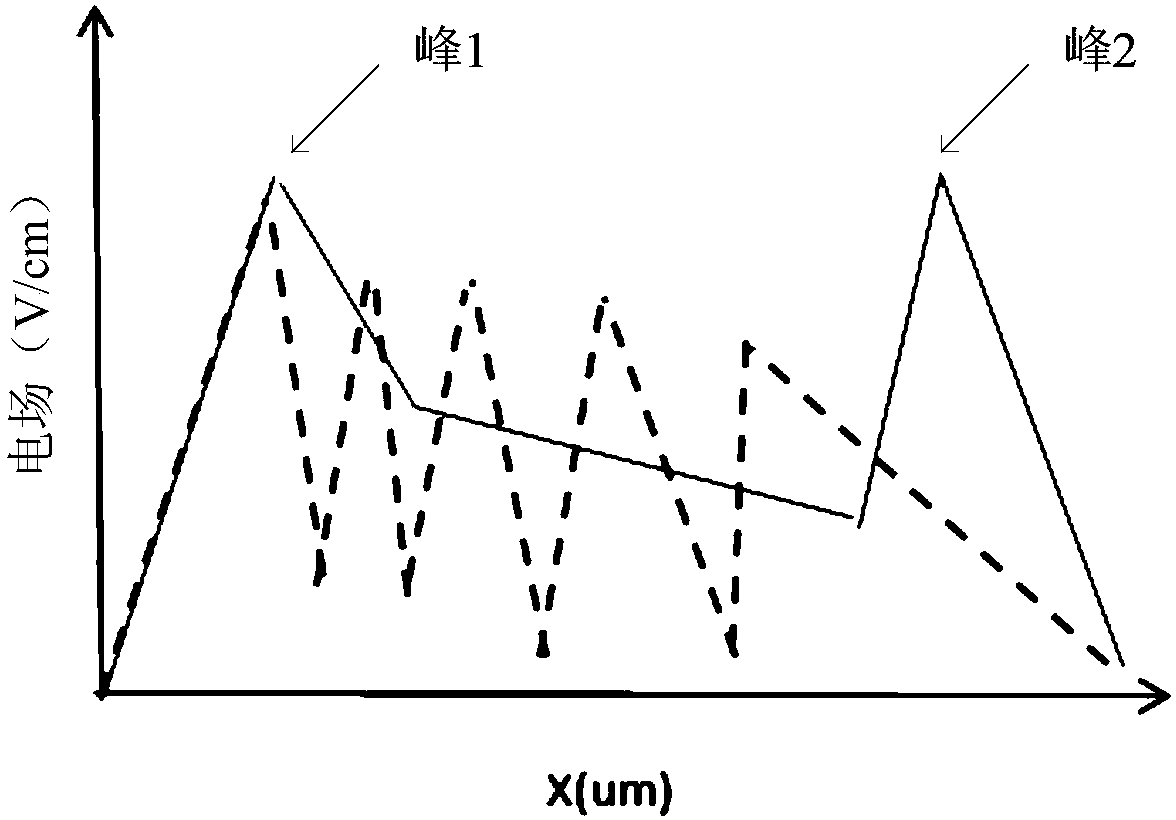

LDMOS (Lateral Diffusion MOS) structure

ActiveCN107785423AWill not increase the quantityIncrease the area of the depleted regionSemiconductor devicesLDMOSGate source capacitance

The invention provides a LDMOS (Lateral Diffusion MOS) structure. The LDMOS structure comprises a semiconductor substrate, a first drift area and a second drift area which are located in the semiconductor substrate and are arranged separately, a source which is located in the first drift area, a drain which is located in the second drift area, a gate structure which is located on the semiconductorsubstrate and whose two sides are contacted with the first drift area and the second drift area respectively, a first isolation structure which is located in the first drift area and isolates the source and the gate structure, and a second isolation structure which is located in the second drift area and isolates the drain and the gate structure, wherein both the first isolation structure and thesecond isolation structure are provided with floating field plates. One or more floating field plates is arranged on the isolation structures between the source-gate and the drain-gate, the area of adepleted area can be increased, collision ionization can be reduced, higher breakdown voltage and saturation leakage current Idsat can thus be acquired, and the gate-drain capacitance Cgd and the gate-source capacitance Cgs of the device are not deteriorated.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Trench insulated gate bipolar transistor device and generating method thereof

InactiveCN109473474AImprove consistencyEnsure consistencySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingDelayed time

The invention provides a trench insulated gate bipolar transistor device and a generating method thereof. A relatively thick gate oxide film is formed at the bottom of a trench region through a plasmafilm forming process. Due to the fact that the thickness of the gate oxide film at the bottom of a trench is increased, the consistency of the gate oxide thickness is guaranteed, the defect that a gate oxide layer at the bottom of the trench is easy to break down is eliminated, and the robustness of a gate oxide breakdown voltage is improved. Meanwhile, the area of a gate-drain capacitor is reduced, so that the Miller capacitance is reduced, the switch delay time is shortened, the switch dynamic loss of a device is reduced, and the switch characteristic of the device is improved. Meanwhile, the relatively thick gate oxide film is formed at the bottom of the trench, so that the upper surface of polycrystalline silicon subjected to back etching can be leveled and is slightly higher than thesurface of a silicon wafer of a N-type base region; and higher N+ emitter junction depth can be formed without increasing the injection energy of an N+ emitter and carrying out longer-time high-temperature trap pushing, so that the vertical overlapping area of the gate and the source is reduced, the gate-source capacitance is reduced, and the switch loss of an IGBT is reduced.

Owner:上海擎茂微电子科技有限公司

Split gate power MOS device

The invention belongs to the technical field of power semiconductors and relates to a split gate power MOS device. Compared with a traditional split gate power MOS, high K medium is introduced as a gate medium layer of a shielding gate and a control gate above the shielding gate is divided into two. When the device is in forward direction blocking, the enhancement of the high K medium assists depletion of a drift region, the concentration of the drift region is improved and the reduction of specific on-resistance is facilitated. When the device is in forward direction conduction, the drift region adjacent to the high K medium produces an electron accumulation layer, the high K medium enhances the accumulation effect and the specific on-resistance is reduced further. When the device is in a switching process, the control gate and the shielding gate are in strong coupling through the high K medium, so that the gate drain capacitance is reduced substantially. At the same time, due to the separately arranged control gate, the overlapping area is reduced, so that the gate source capacitance and the total gate charge are reduced. Compared with the traditional split gate power MOS, the split gate power MOS device has lower specific on-resistance and gate drain charge; the QGC*RDS (on) figure of merit is improved distinctively and drive loss and switch loss are reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

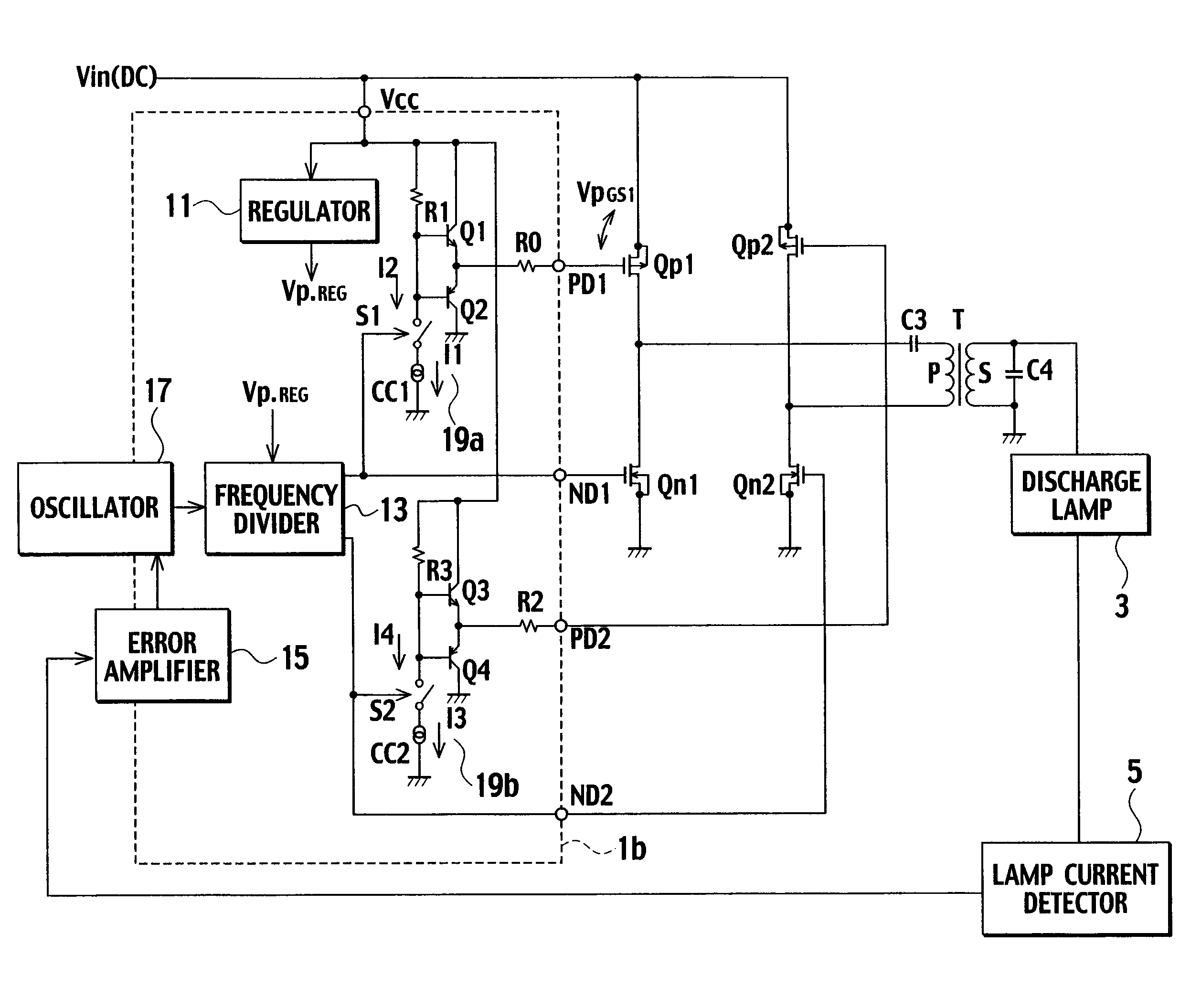

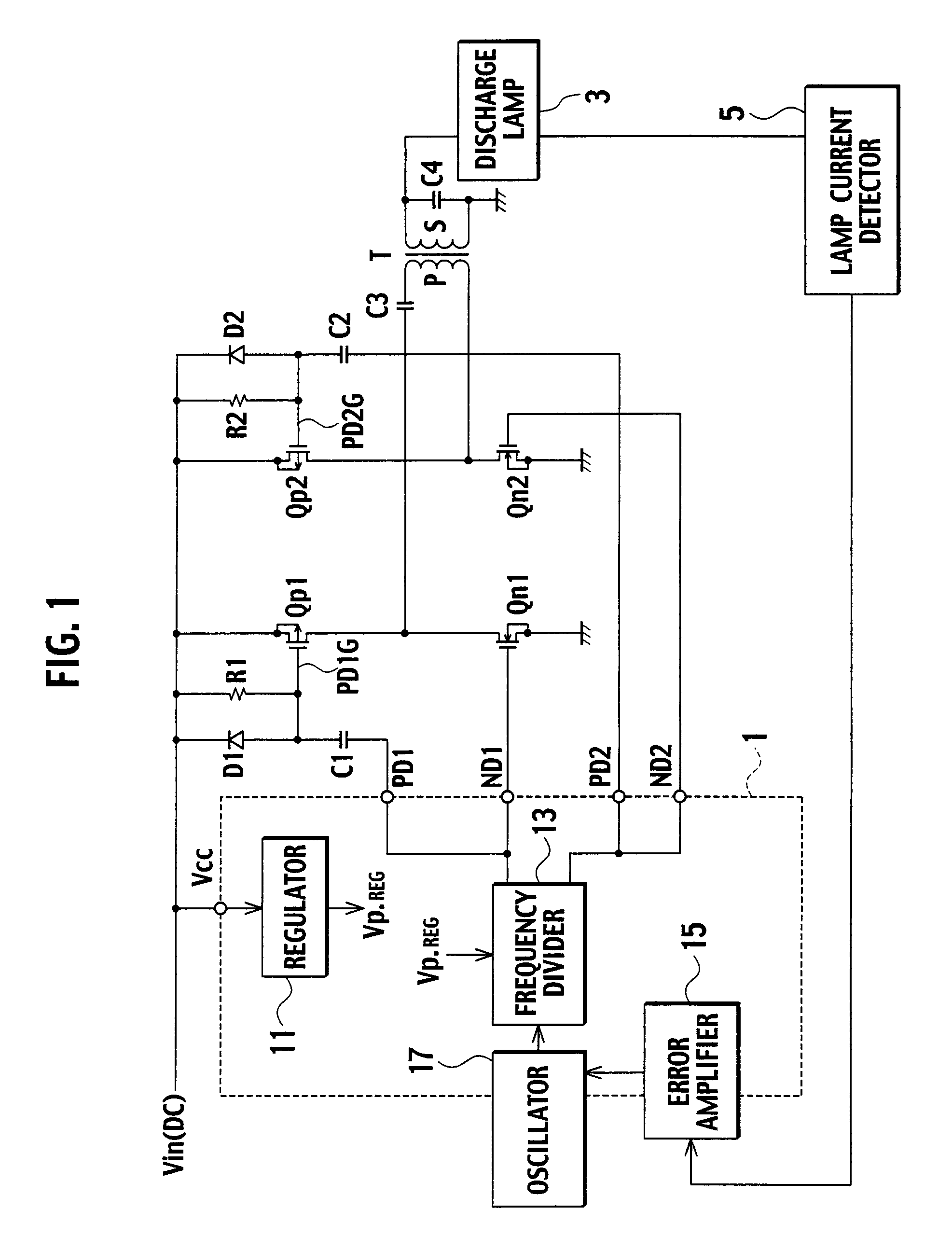

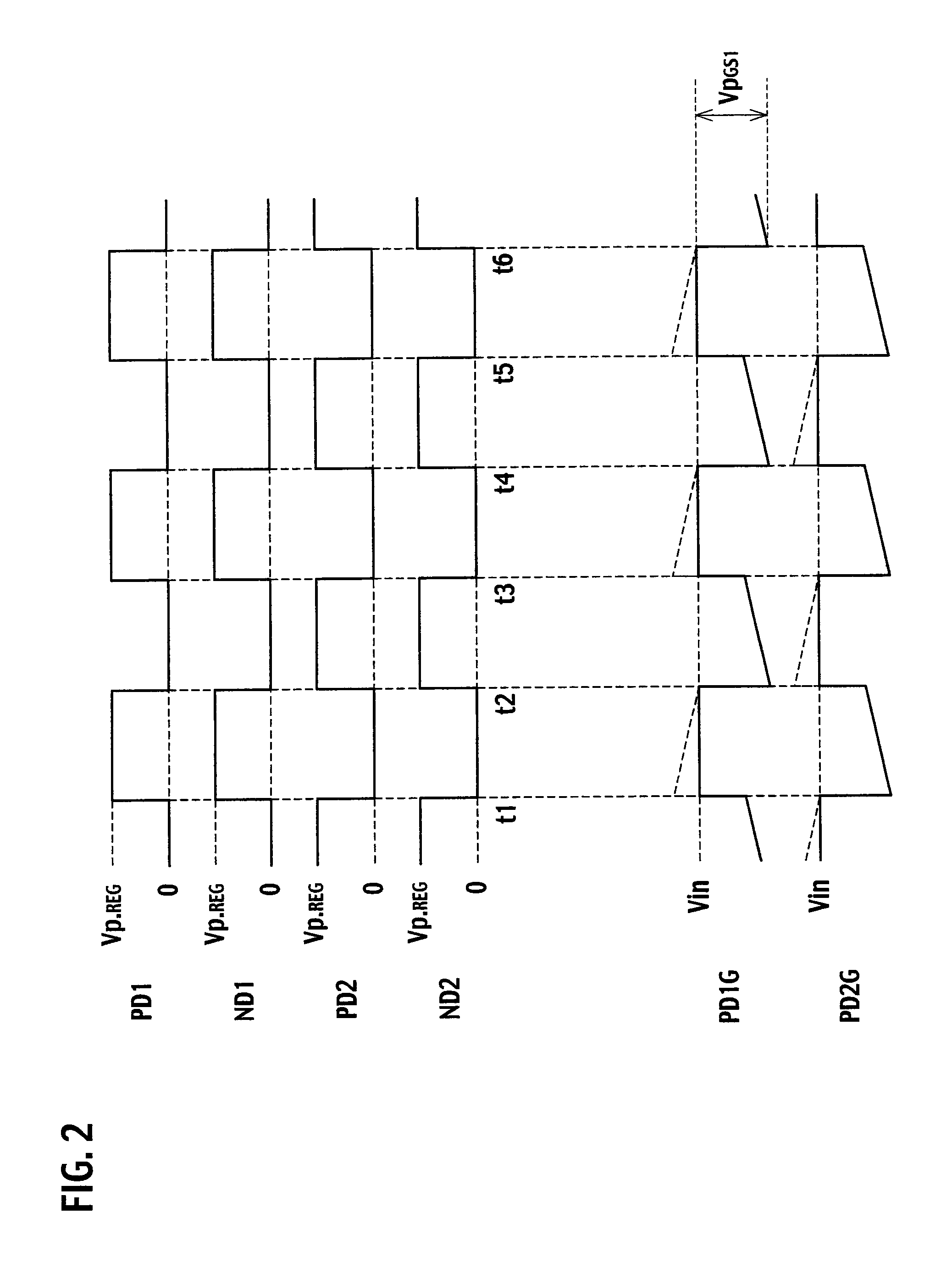

Discharge-lamp lighting apparatus

InactiveUS20080042586A1Improve efficiencyElectrical apparatusElectric light circuit arrangementTransformerEffect light

A discharge-lamp lighting apparatus includes series circuits connected to each end of a DC power source, a transformer, FETs Qp1, Qn1, Qp2, and Qn2, and a drive circuit. The drive circuit includes transistors Q1 and Q3 to discharge gate-source capacitances of the Qp1 and Qp2, resistance elements to determine gate potentials of the transistors Q1 and Q3 when the transistors Q1 and Q3 are turned on, transistors Q2 and Q4 to charge the gate-source capacitances of the Qp1 and Qp2, constant current circuits, and switches connected in series with the series circuits of the constant current circuits and resistance elements, respectively, to turn on / off the constant current circuits.

Owner:SANKEN ELECTRIC CO LTD

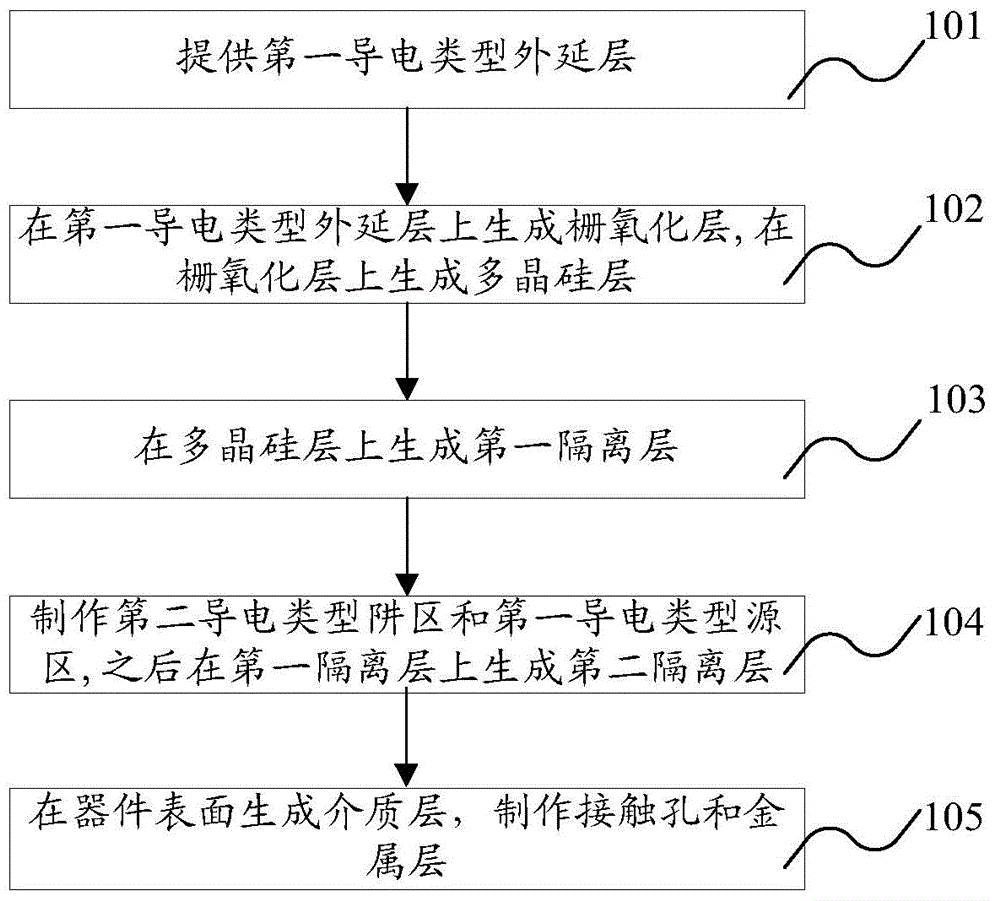

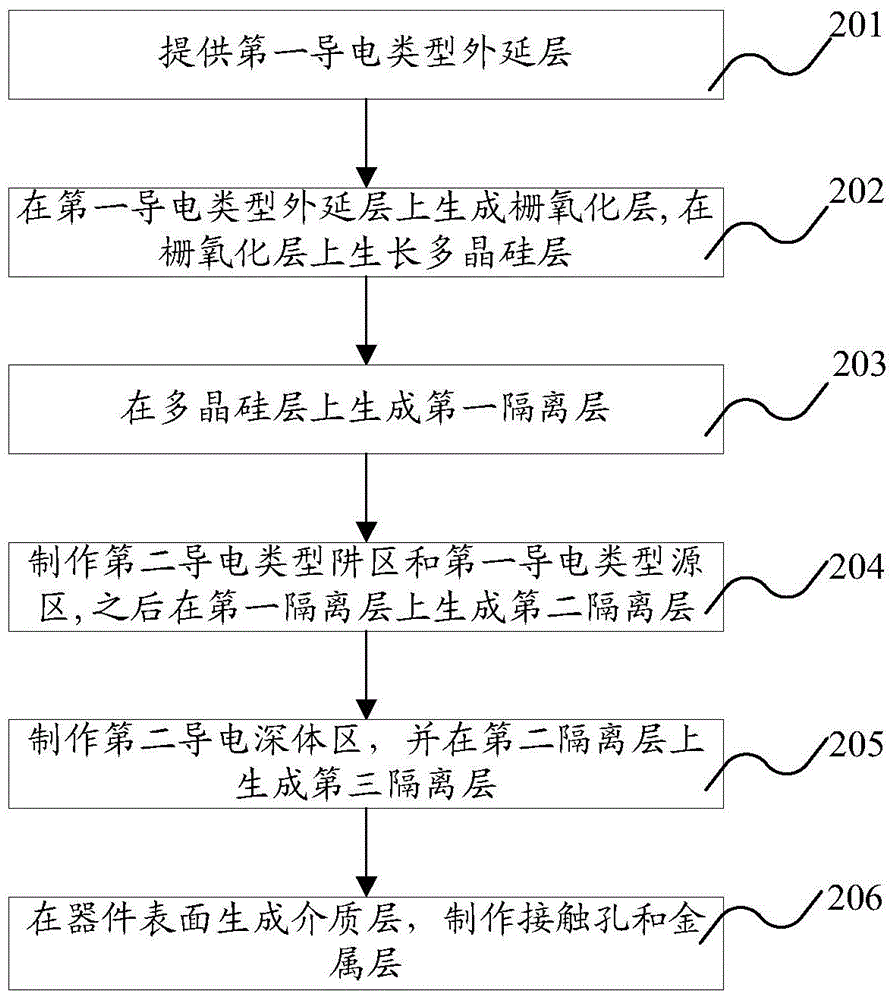

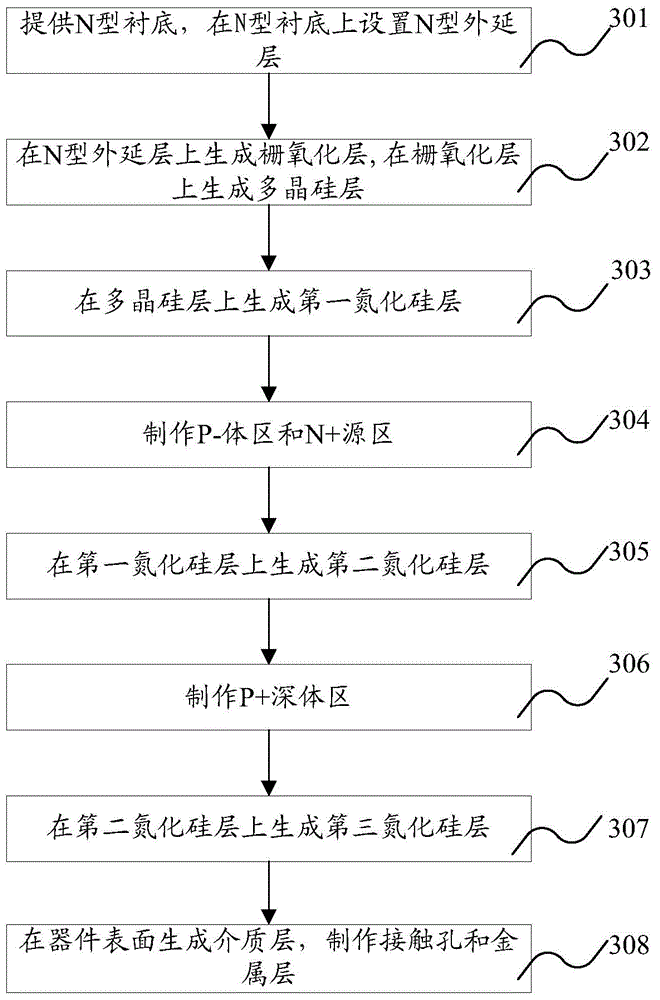

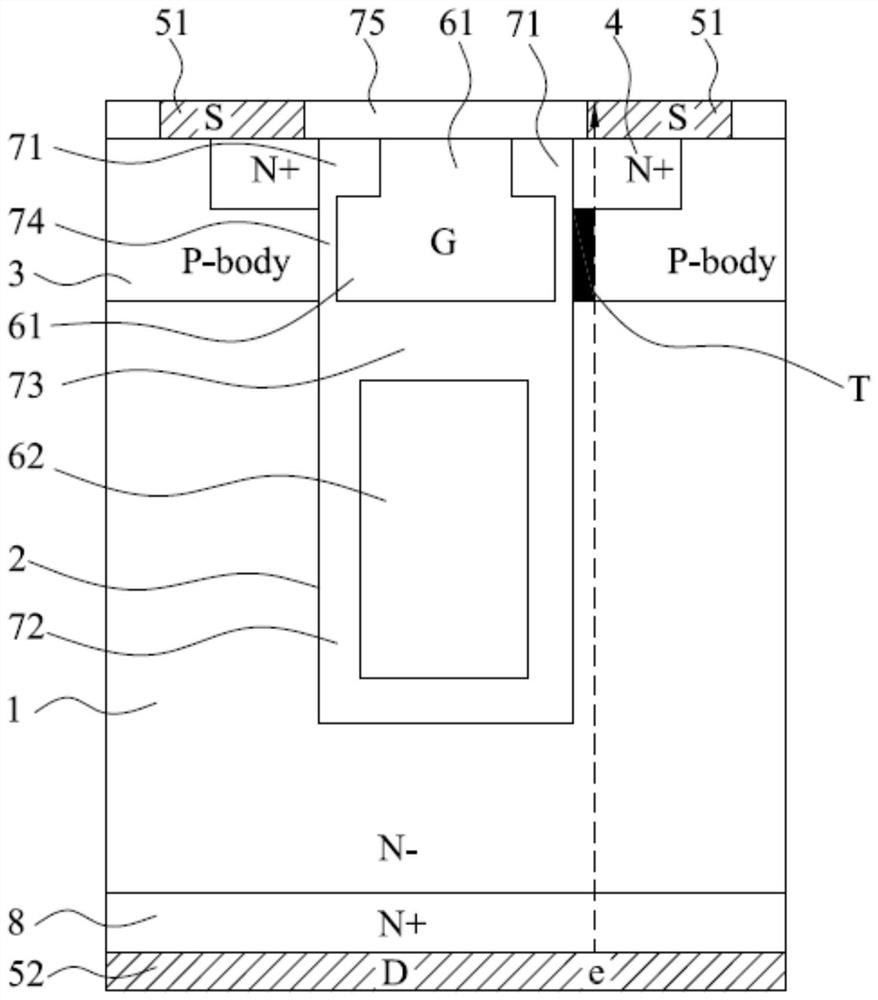

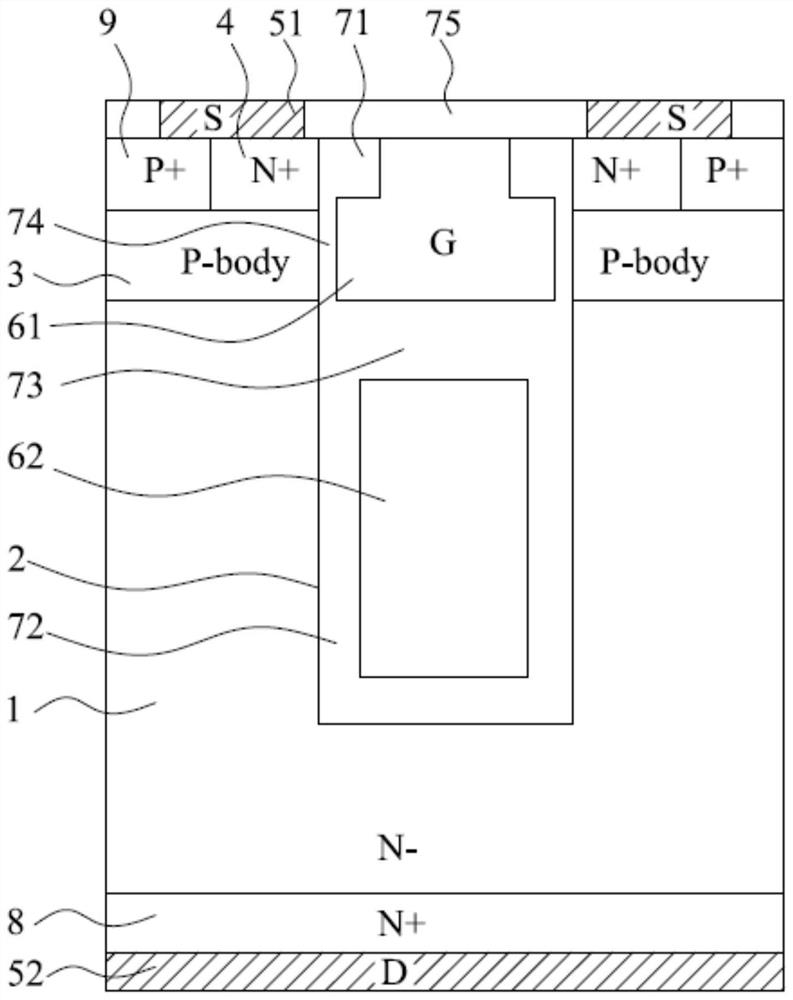

Planar VDMOS device and manufacturing method thereof

ActiveCN105244279AReduce switching lossesTight textureSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation layerGate source capacitance

The invention discloses a planar VDMOS device and a manufacturing method thereof. The method comprises the steps as follows: providing a first conductivity type substrate, and arranging a first conductivity type epitaxial layer on the first conductivity type substrate; generating a gate oxide layer on the first conductivity type epitaxial layer, and generating a polycrystalline silicon layer on the gate oxide layer; generating a first isolation layer on the polycrystalline silicon layer; making a second conductivity type well region and a first conductivity type source region; and generating a dielectric layer, making a contact hole and a metal layer, and generating a second isolation layer on the first generation layer, wherein the first conductivity type and the second conductivity type are opposite. By growing more dense isolation layers between the gate polycrystalline silicon layer and the source metal layer, the spacing between the gate and source plates is increased, and the gate capacitance and source capacitance of the planar VDMOS device are reduced.

Owner:FOUNDER MICROELECTRONICS INT

Shield grid MOSFET and manufacturing method thereof

ActiveCN113851523AQuick responseAvoid direct contactSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETGate source capacitance

The invention discloses a shield grid MOSFET and a manufacturing method thereof. The shield grid MOSFET comprises a drift region of a first conduction type, a trench located in the top of the drift region and body regions of a second conduction type located on the two sides of the trench; a grid electrode and a shield grid are arranged in the trench, the grid electrode is located above the shield grid, and a first doped region of a first conduction type is arranged on one side, close to the grid electrode, of the top of the body region; a source electrode is arranged on the top surface of the first doped region, and the body region is connected with the source electrode; the shield grid is connected with the source grid; and a first oxide layer is arranged between the grid electrode and the first doped region, a grid oxide layer is arranged between the grid electrode and the body region, a second oxide layer is arranged between the shield grid and the inner wall of the trench, a third oxide layer is arranged between the grid electrode and the shield grid, and the thickness of the first oxide layer is greater than that of the grid oxide layer. According to the shield grid MOSFET, the grid drain capacitance is reduced, the grid source capacitance is reduced, and the response speed of the shield gate MOSFET is improved.

Owner:VANGUARD SEMICON CORP

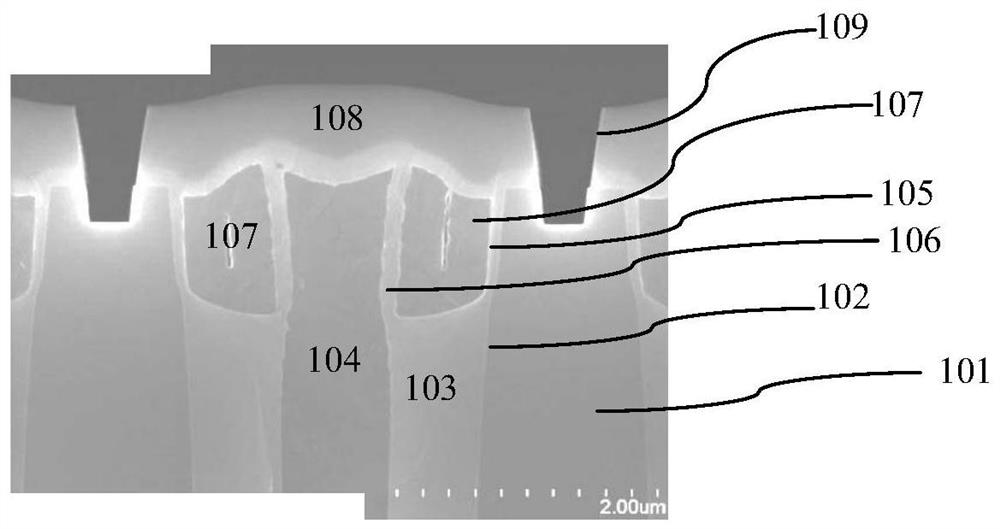

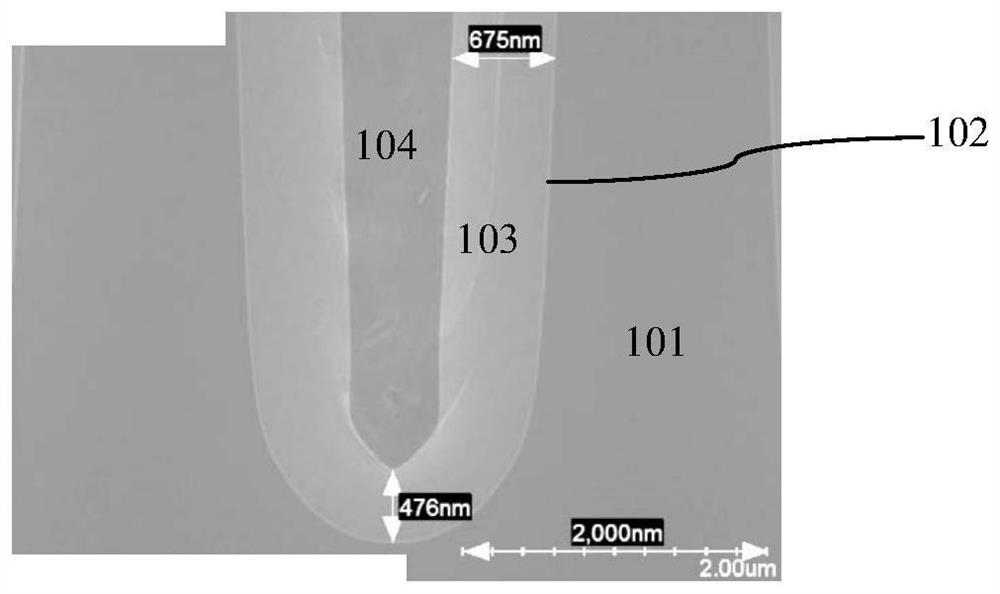

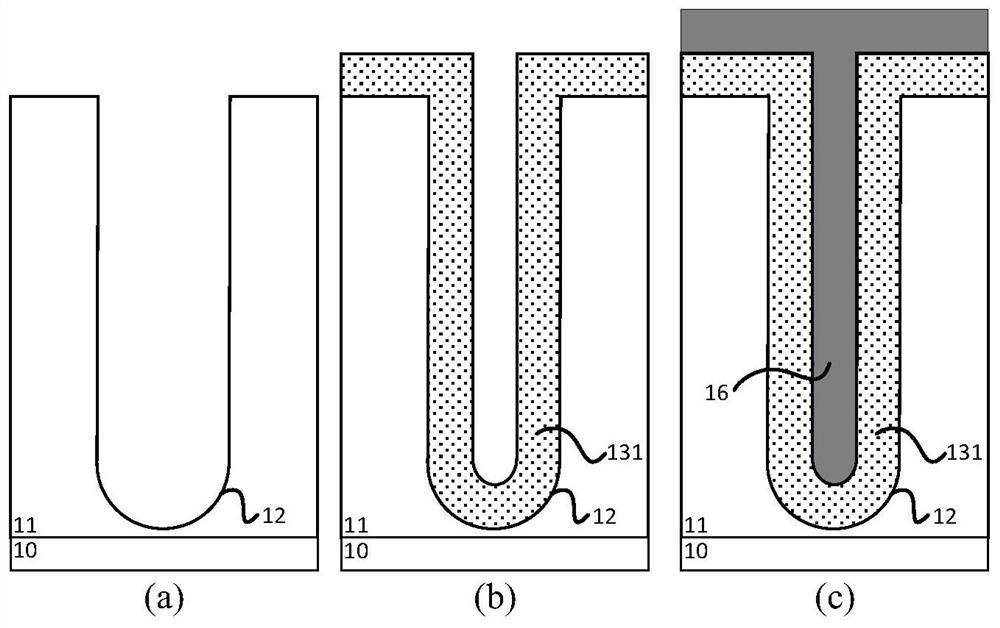

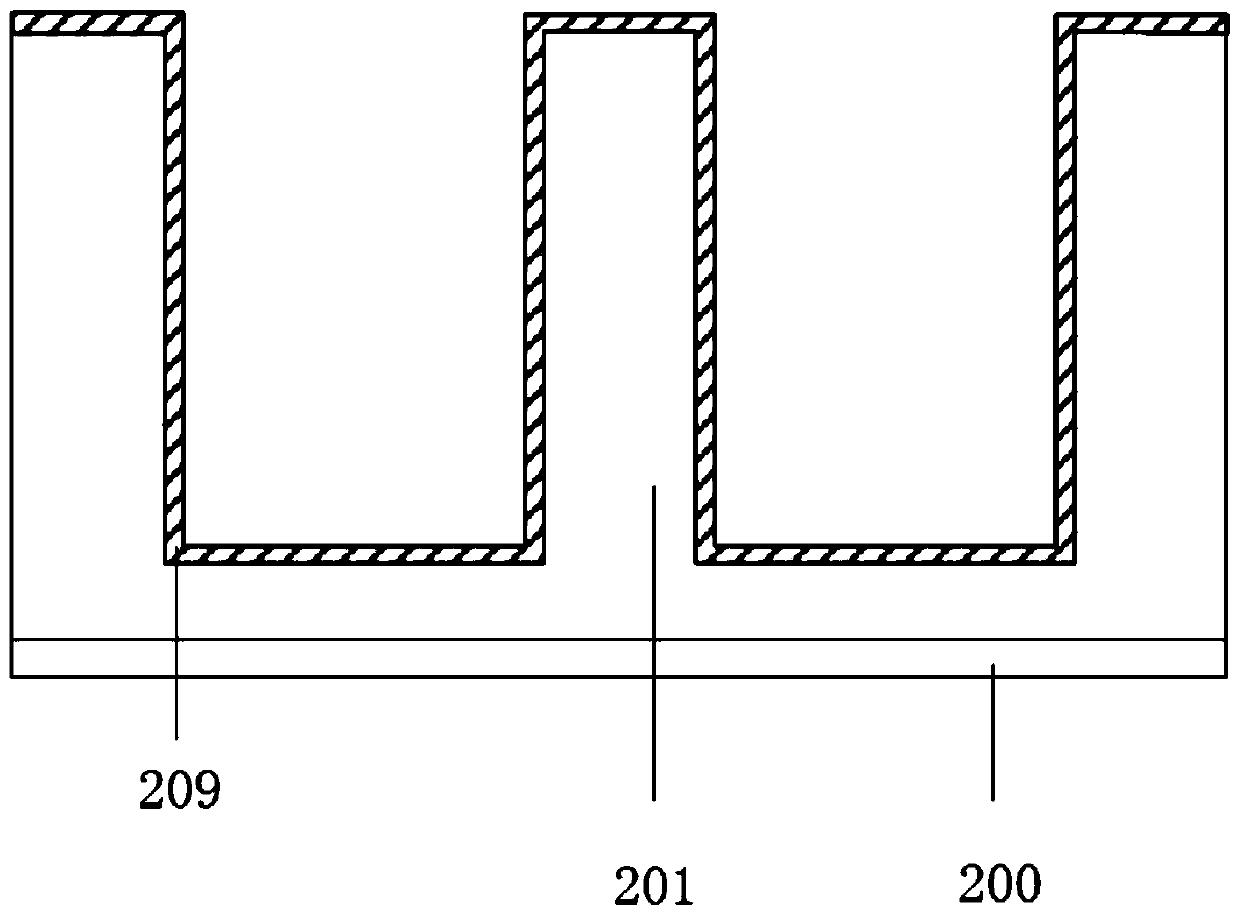

Manufacturing method of separation gate power MOSFET device

ActiveCN113078066ACgs decreaseLow gate charge characteristicsEfficient power electronics conversionSemiconductor/solid-state device manufacturingGate source capacitancePower MOSFET

The invention provides a manufacturing method of a separation gate power MOSFET device, which comprises the following steps of: after a dielectric layer between a control gate and a separation gate is formed, depositing or thermally growing a sacrificial oxide layer, depositing silicon nitride to fill the whole groove structure, and separating the silicon nitride from a silicon layer in an MESA region through the sacrificial oxide layer; after etching the silicon nitride, taking the silicon nitride reserved in the groove as a shielding layer for etching the oxide layer; etching the oxide layer until the interface of the oxide layer is higher than the upper interface of the stepped separation gate, and then etching the residual silicon nitride; and depositing polycrystalline silicon and performing back etching to form a control gate electrode. According to the device structure prepared by the invention, the lower half part of the control gate is relatively narrow, so that the gate-source capacitance Cgs can be greatly reduced, and meanwhile, the upper half part of the control gate increases the cross sectional area of gate current flowing, so that the gate resistance is reduced and the targets of high switching speed and low switching loss are achieved on the premise of ensuring that the gate-source capacitance Cgs and gate charge Qg are not degraded.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

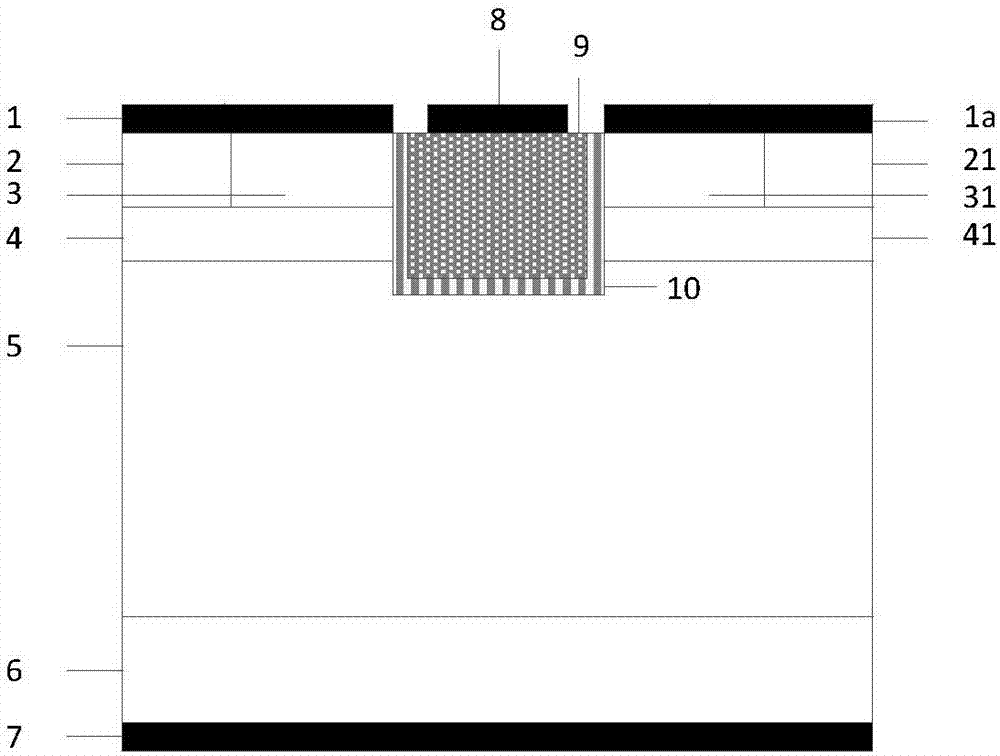

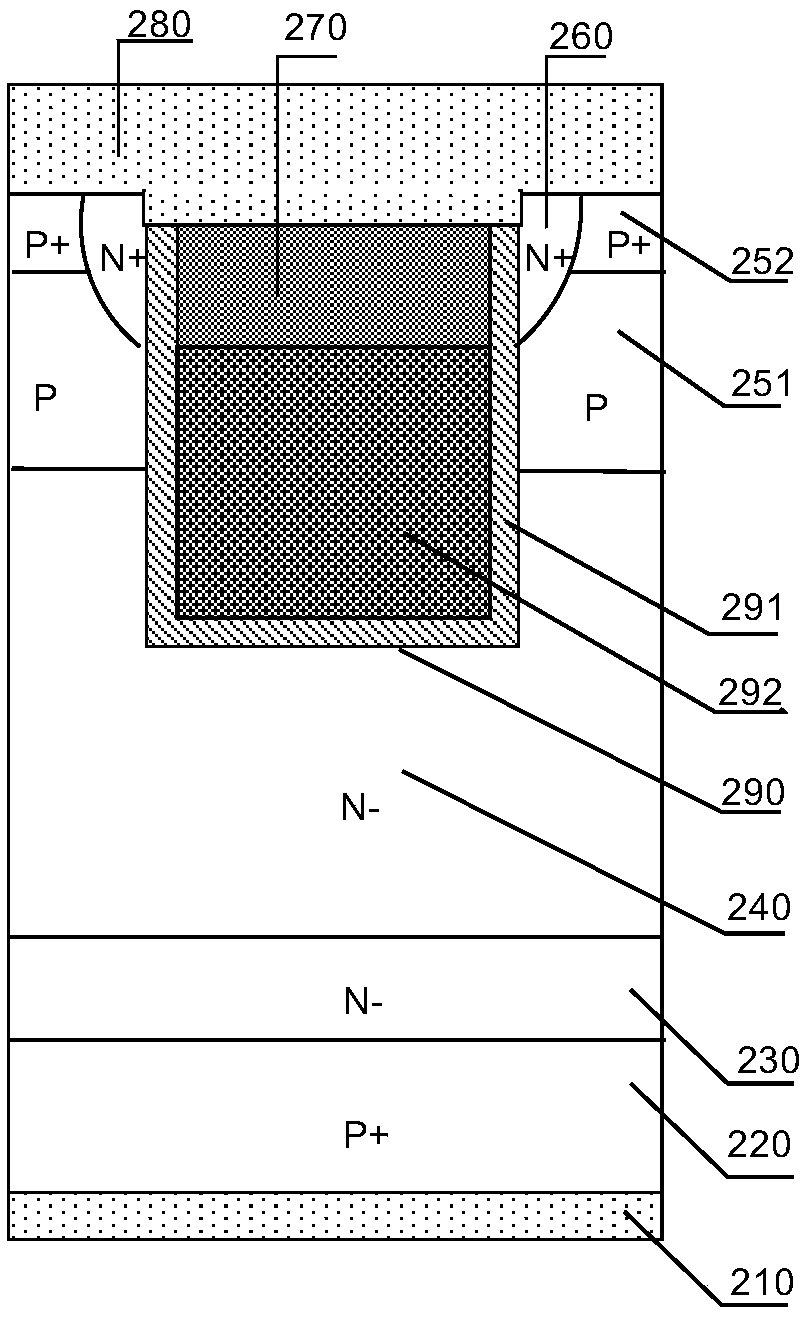

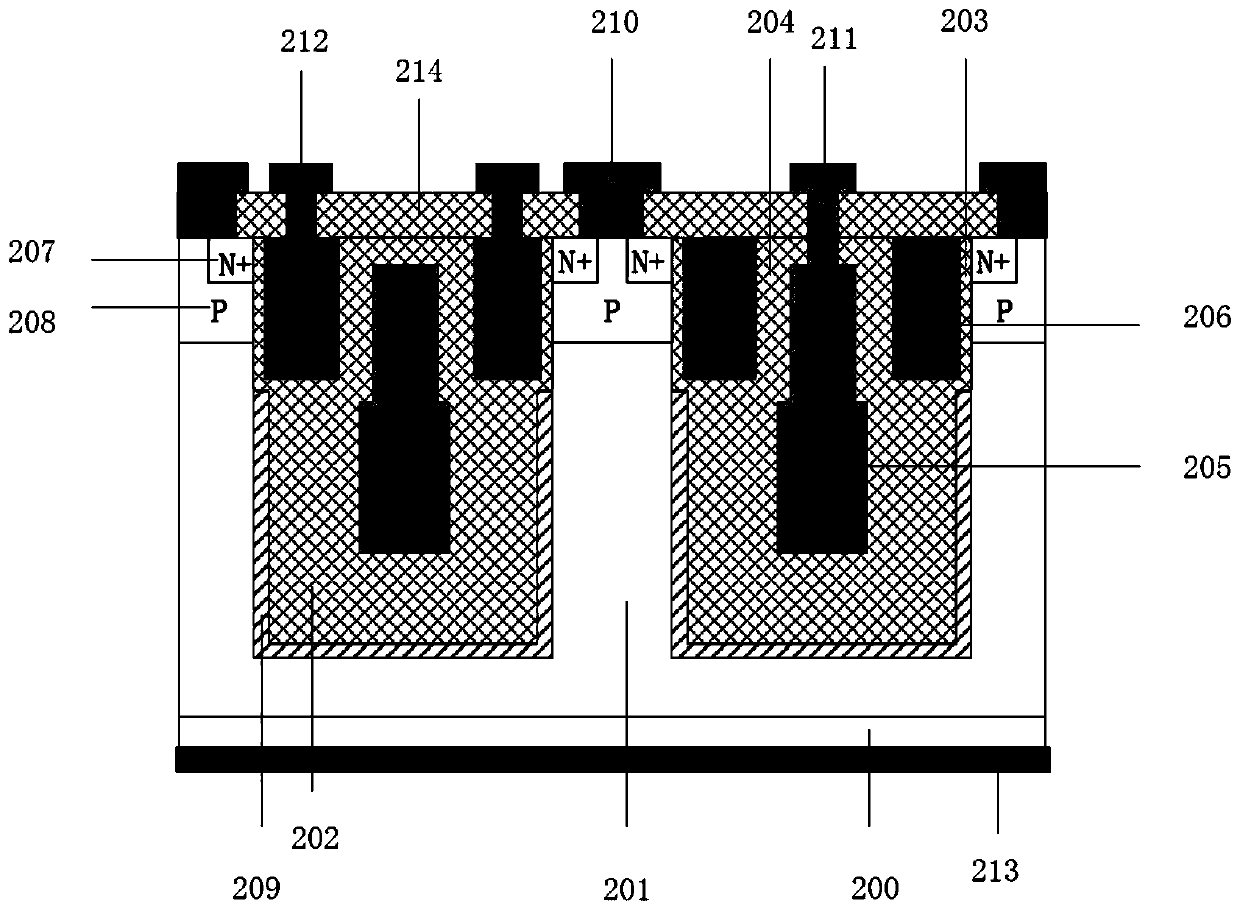

Power semiconductor device and method for fabricating same

PendingCN109830526AReduce gate-source capacitanceFast switching speedSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceGate source capacitance

A power semiconductor device and a method for fabricating the same are provided. In order to further increase the switching speed of a shielded gate trench field effect transistor and reduce the switching loss, the invention provides a shield gate trench field effect transistor device structure with a simple fabrication process and a method for fabricating the same. A gate oxide layer and an inter-electrode isolation dielectric layer are respectively formed in different steps, so that the formed inter-electrode isolation dielectric layer is relatively thick, thereby achieving effects of reducing the gate-source capacitance of the device, increasing the switching speed of the device, and reducing the switching loss.

Owner:安建科技(深圳)有限公司