Semiconductor device and preparation method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their production, can solve problems such as capacitance mismatch, achieve the effect of increasing gate-source capacitance and solving mutual mismatch

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

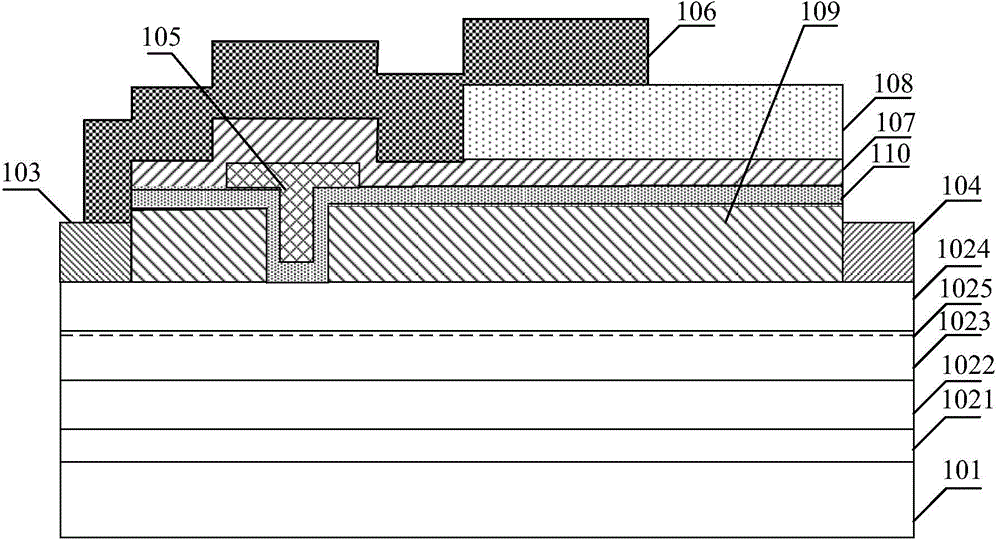

[0044] figure 1 is a schematic cross-sectional view of the semiconductor device provided by Embodiment 1 of the present invention. Such as figure 1 As shown, the semiconductor device includes:

[0045] Substrate 101.

[0046] In this embodiment, the material of the substrate 101 can be sapphire, silicon nitride, gallium nitride, silicon or other materials suitable for growing gallium nitride; the deposition method of the substrate 101 can be atmospheric pressure chemical vapor deposition (APCVD) , Subatmospheric pressure chemical vapor deposition (SACVD), metal organic compound chemical vapor deposition (MOCVD), low pressure chemical vapor deposition (LPCVD), high density plasma chemical vapor deposition (HDCVD), ultra-high vacuum chemical vapor deposition Deposition method (UHCVD), plasma enhanced chemical vapor deposition method (PlasmaEnhancedChemicalVaporDeposition, referred to as PECVD), catalytic chemical vapor deposition method (Cat-CVD), mixture physical and chemica...

Embodiment 2

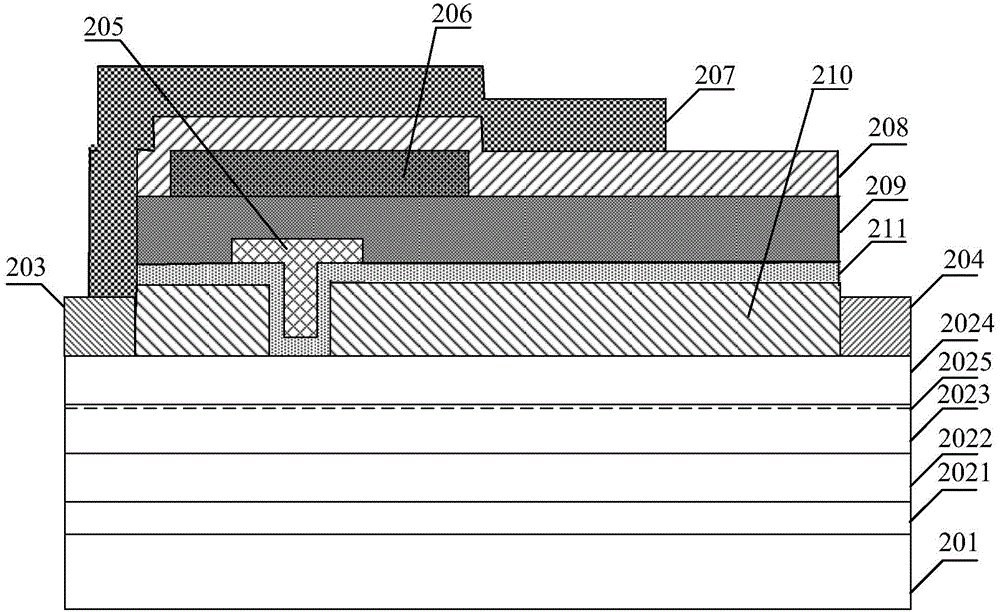

[0084] figure 2 is a schematic cross-sectional view of the semiconductor device provided by Embodiment 2 of the present invention. Such as figure 2 As shown, the semiconductor device provided in the second embodiment includes:

[0085] Substrate 201.

[0086] In this embodiment, the material of the substrate 201 can be sapphire, silicon nitride, gallium nitride, silicon or other materials suitable for growing gallium nitride; the deposition method of the substrate 201 can be atmospheric pressure chemical vapor deposition (APCVD) , Subatmospheric pressure chemical vapor deposition (SACVD), metal organic compound chemical vapor deposition (MOCVD), low pressure chemical vapor deposition (LPCVD), high density plasma chemical vapor deposition (HDCVD), ultra-high vacuum chemical vapor deposition Deposition method (UHCVD), plasma enhanced chemical vapor deposition method (PlasmaEnhancedChemicalVaporDeposition, referred to as PECVD), catalytic chemical vapor deposition method (Ca...

Embodiment 3

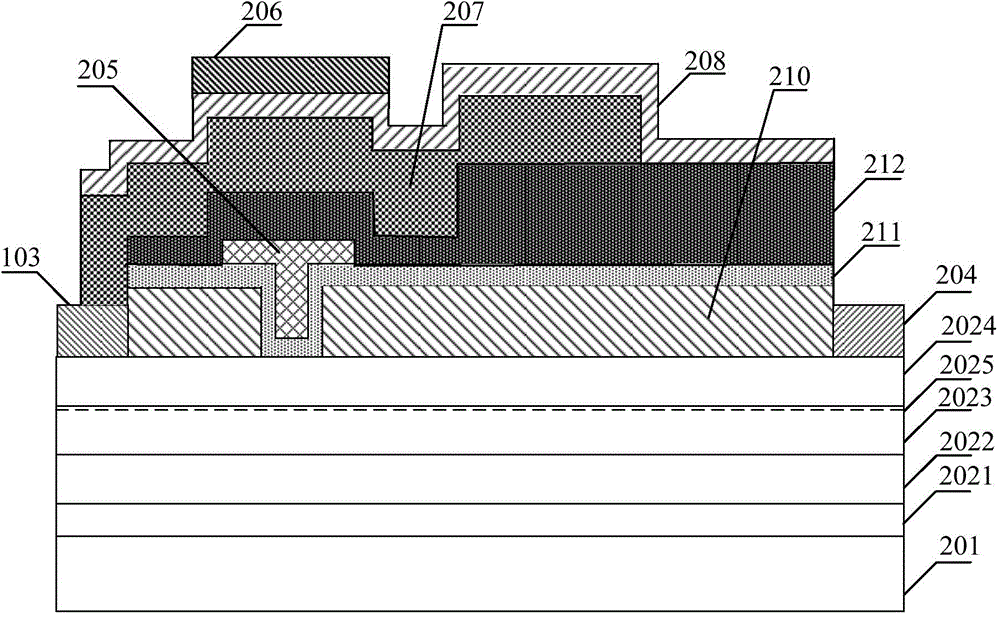

[0119] image 3 is a schematic cross-sectional view of the semiconductor device provided by Embodiment 3 of the present invention. Such as image 3 As shown, the difference from the semiconductor device provided in Embodiment 2 is that the gate field plate 206 of the semiconductor device provided in Embodiment 3 is located above the source field plate 207, and the semiconductor device does not include a second dielectric layer, But also include:

[0120] The third dielectric layer 212 is located between the gate 205 and the source field plate 207 .

[0121] In this embodiment, the third dielectric layer 212 is used to isolate the gate 205 and the source field plate 207; the smaller the thickness of the third dielectric layer 212, the larger the gate-source capacitance of the resulting semiconductor device.

[0122] Wherein, the material of the third dielectric layer 212 may be silicon nitride, silicon oxide, aluminum oxide or hafnium oxide; the manufacturing process of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More