Planar VDMOS device and manufacturing method thereof

A manufacturing method and planar technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems affecting the dynamic characteristics of VDMOS switches, limited improvement effects, and affecting the metal filling of contact holes, etc., to achieve good switches Effects of dynamic characteristics, reduced capacitance, and increased distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

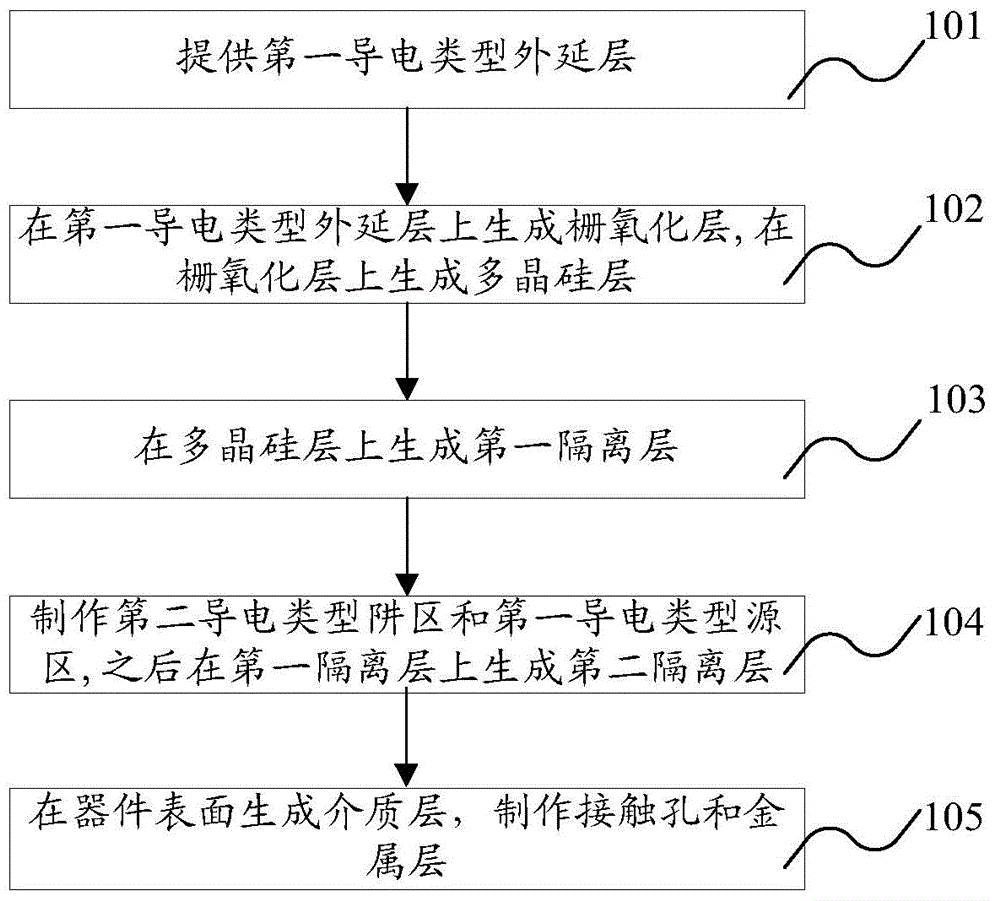

[0034] figure 1 The process flow of a method for manufacturing a planar VDMOS device disclosed in the present invention specifically includes the following steps:

[0035] Step 101: providing a first conductivity type epitaxial layer;

[0036] In this step, a substrate of the first conductivity type can be provided first, and an epitaxial layer of the first conductivity type is formed on the substrate of the first conductivity type. The substrate of the first conductivity type can be an N-type substrate or a P-type substrate. Bottom, when the substrate of the first conductivity type is an N-type substrate, the first conductive epitaxial layer disposed on the N-type substrate is an N-type epitaxial layer; when the substrate of the first conductivity type is a P-type substrate At the bottom, the first conductive epitaxial layer disposed on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More