A kind of manufacturing method of flash memory wafer

A manufacturing method and wafer technology, applied in the direction of transistors, semiconductor/solid-state device manufacturing, diodes, etc., can solve problems affecting product storage performance, weakening the coupling rate of control gate and floating gate, etc., and achieve the effect of realizing height and adjustment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the purpose, technical solution and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings.

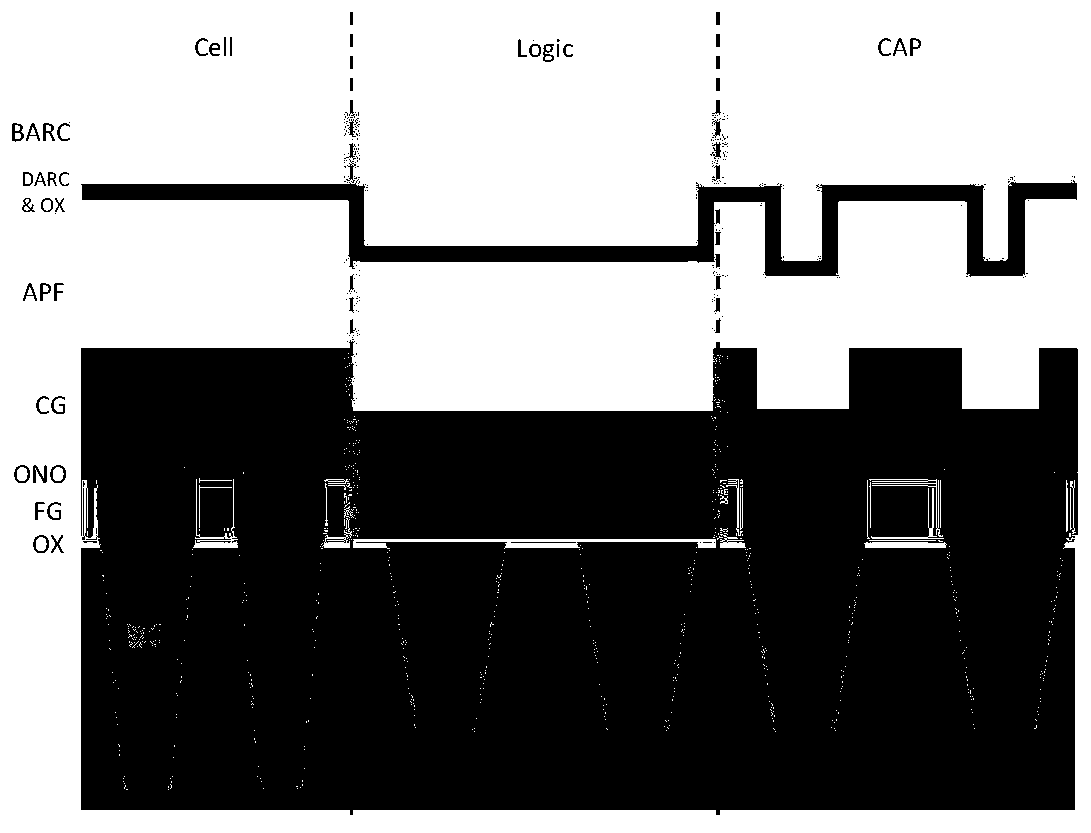

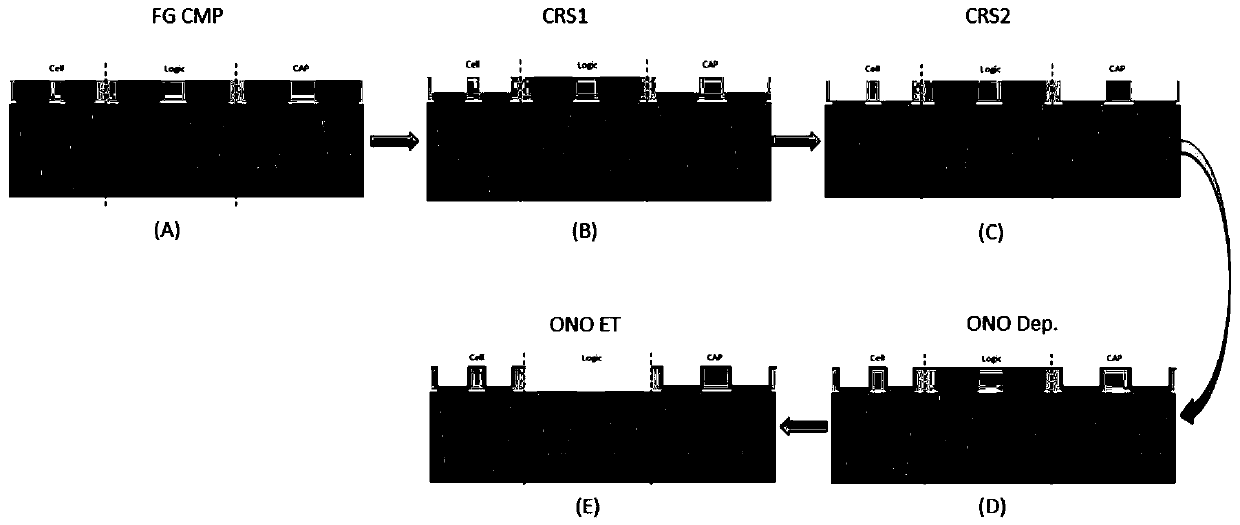

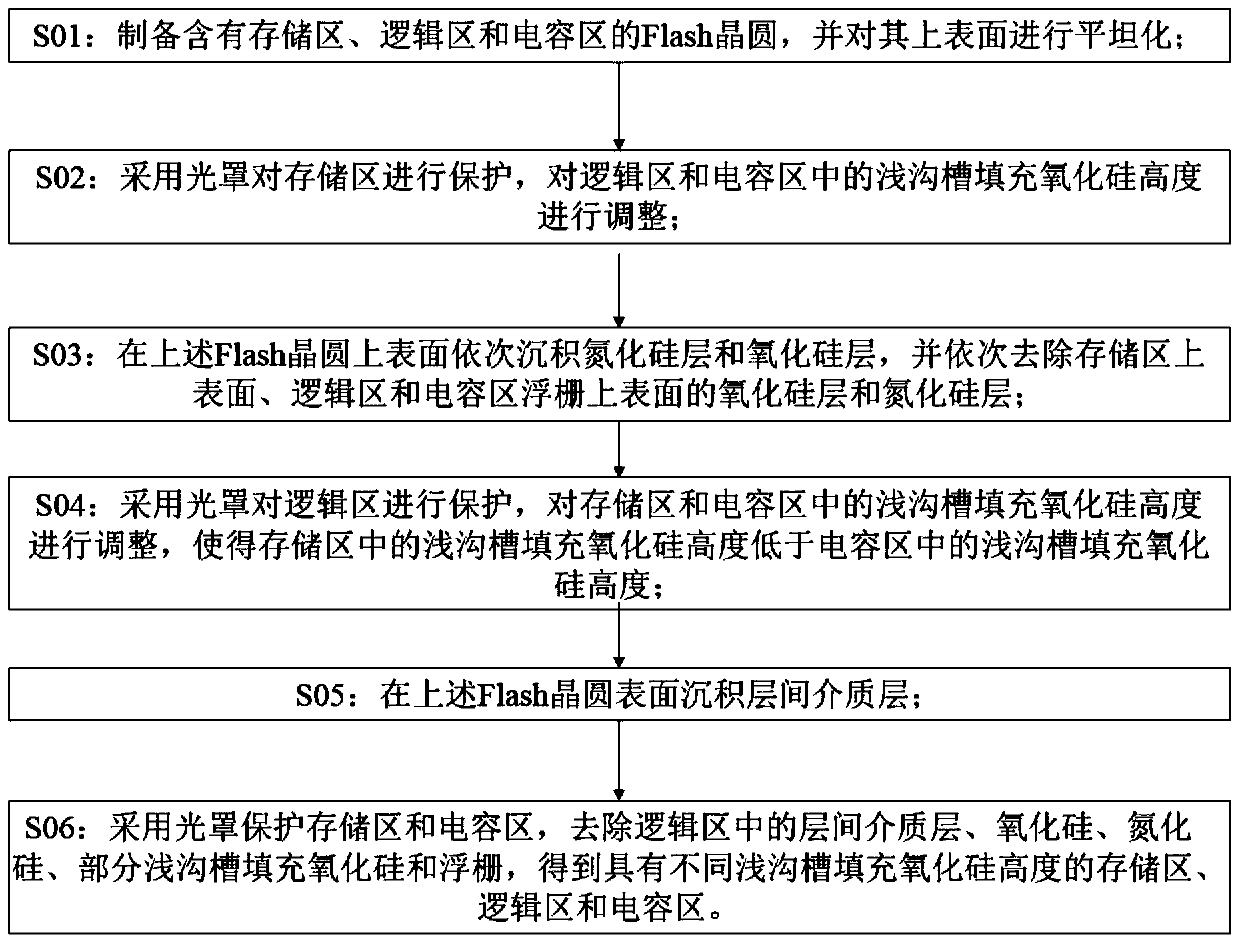

[0035] as attached image 3 And attached Figure 4 As shown, a kind of preparation method of flash memory wafer provided by the present invention comprises the following steps:

[0036] S01: If Figure 4 As shown in A, a flash memory wafer containing a storage area, a logic area, and a capacitor area is prepared, and its upper surface is planarized, wherein the storage area, the logic area, and the capacitor area all include shallow trench isolation and an active area, and the shallow The trench isolation is located in the gap of the active area, and there is a floating gate above the active area. The shallow trench isolation contains shallow trench filling silicon oxide, and the planarized shallow trench filling silicon o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More