Semiconductor structure and forming method therefor

一种半导体、栅极结构的技术,应用在半导体结构及其形成领域,能够解决半导体器件电学性能有待提高等问题,达到改善栅漏电流问题的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

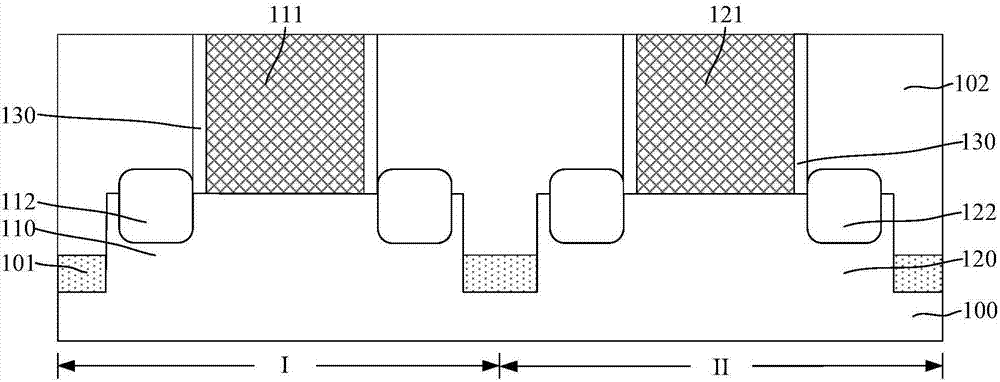

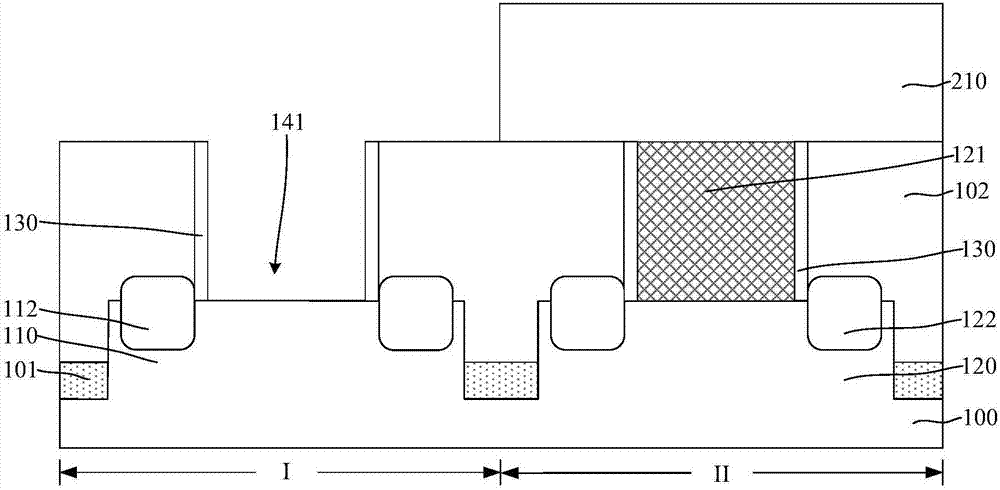

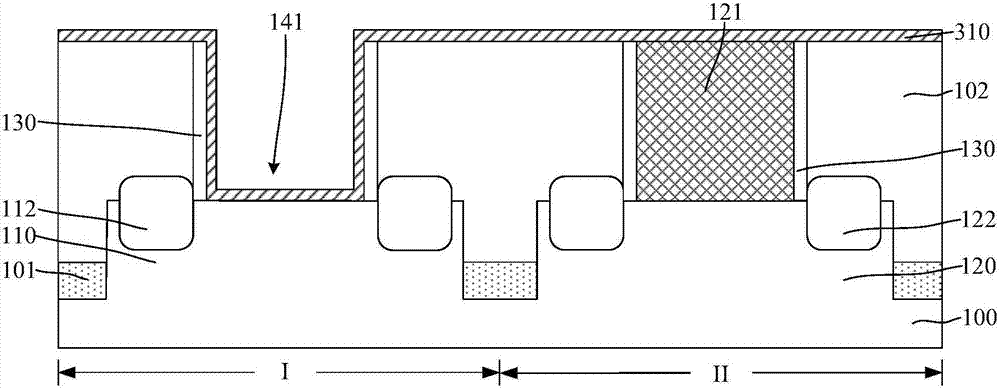

[0012] It can be seen from the background technology that with the continuous reduction of semiconductor device technology nodes, high-k gate dielectric materials are currently used instead of traditional silicon dioxide gate dielectric materials to improve semiconductor gate leakage current (Gate Leakage) and equivalent gate oxide thickness (EOT )And other issues. However, the electrical performance of semiconductor devices still needs to be improved. Combined with a method of forming a semiconductor structure, the reason is analyzed.

[0013] The forming method includes: providing a substrate, the substrate includes an NMOS region and a PMOS region, the NMOS region substrate is a III-V group compound substrate, and the PMOS region substrate is a germanium-containing substrate; using an oxidation process, the substrate is forming an interface layer on the interface layer; forming a high-K gate dielectric layer on the interface layer; forming a metal layer on the high-K gate ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| annealing point | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com