Method for outputting power-up constant value of six-tube SRAM (Static Random Access Memory) for single-threshold CMOS (Complementary Metal Oxide Semiconductor) device

An output method and single-threshold technology, applied in the direction of instruments, static memory, digital memory information, etc., to achieve the effect of improving reliability and correct function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

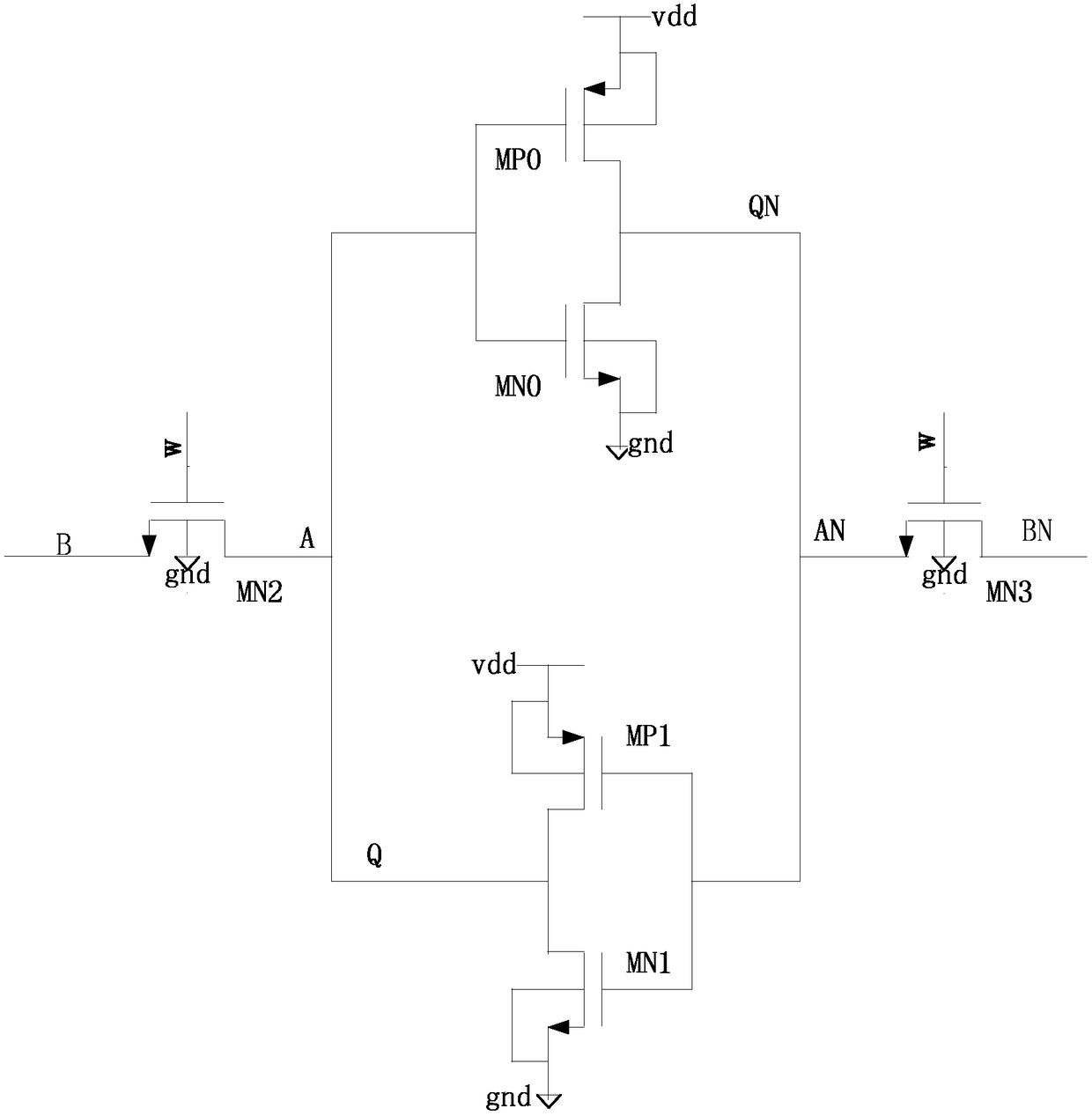

[0031] Such as figure 1 As shown, MP0 and MP1 are P-channel enhancement type PMOS transistor devices, and MN0, MN1, MN2, and MN3 are N-channel enhancement type NMOS transistor devices. MP0, MN0, MP1, and MN1 transistors form a cross-coupled latch circuit to form a stable current source similar to a miniature milliampere level. MN2 and MN3 transistors are switching gate devices of the memory. When the transistor MN0 is off and the transistor MP0 is on, the output signal Q is logic “0” and QN is logic “1”. When these signals are inverted, the output signal Q is a logic "1" and QN is a logic "0". The left and right bit line B and BN signals are mutually opposite data signals, and the operation of reading and writing data of the memory can be realized by controlling the B and BN signal lines. The six-tube SRAM memory cell has two switching gat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More