Preparation method of chip packaging body and chip packaging body

A chip packaging and chip technology, which is applied in the field of integrated circuit chip packaging, can solve the problems of low efficiency in the interconnection process between flip chips and circuit boards, and achieve the effect of improving efficiency and improving interconnection efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention.

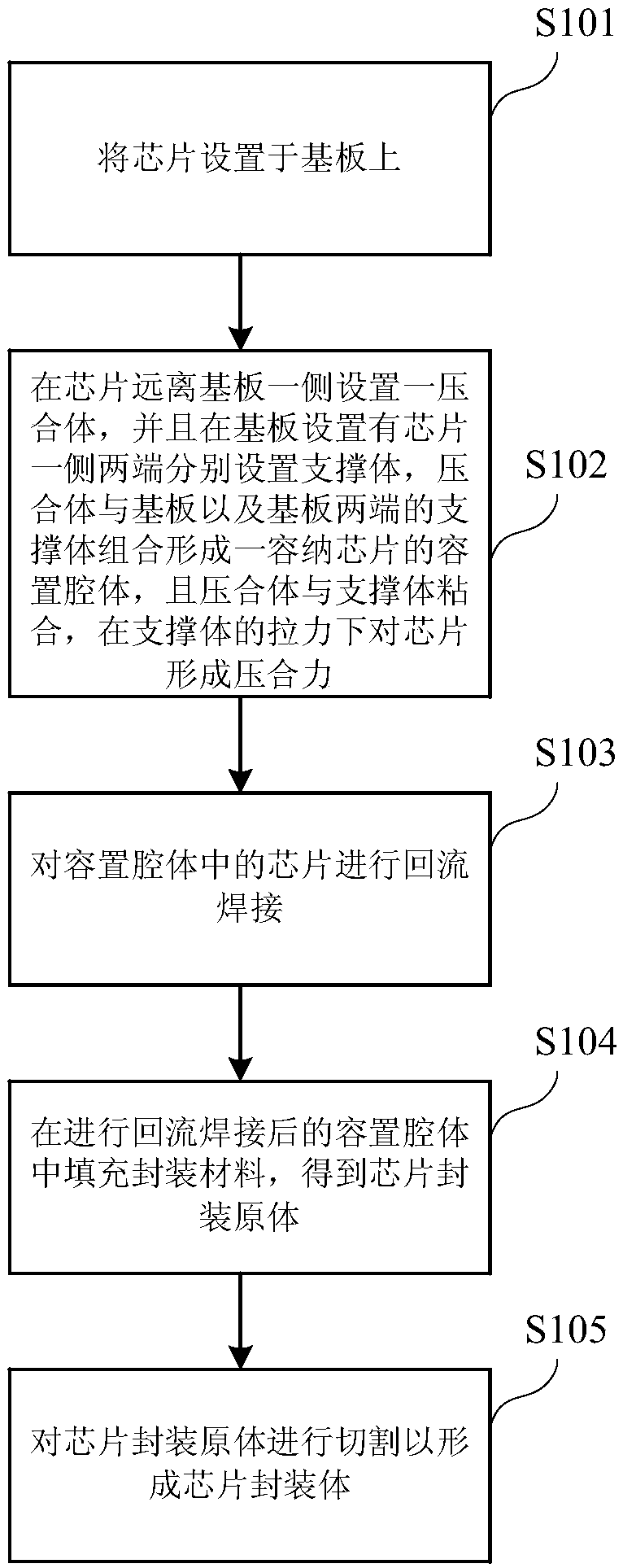

[0024] see figure 1 , figure 1 is a schematic flow chart of the first embodiment of the chip package manufacturing method of the present invention.

[0025] S101: disposing the chip on the substrate;

[0026] In this embodiment, the substrate is the carrier platform of the chip. Since the chip is provided with many precision parts and circuit pins, and the cost of chip preparation is expensive, in order to protect the structural integrity of the chip, the chip is arranged on the substrate. The substrate is connected to the external circuit. While providing sufficient protection strength for the chip, the plasticity of the substrate is higher than that of the chip, so the substrate and the connection structure of the external circuit can be adapted to each other to realize th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More