Heterogeneous integration method and heterogeneous integrated device of compound semiconductor and silicon-based complementary metal oxide semiconductor wafer

A technology of oxide semiconductors and complementary metals, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problems that different material devices cannot be mixed and integrated, process compatibility cannot be achieved, and device selection is limited, etc., to achieve Facilitate automatic application, improve production efficiency, and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

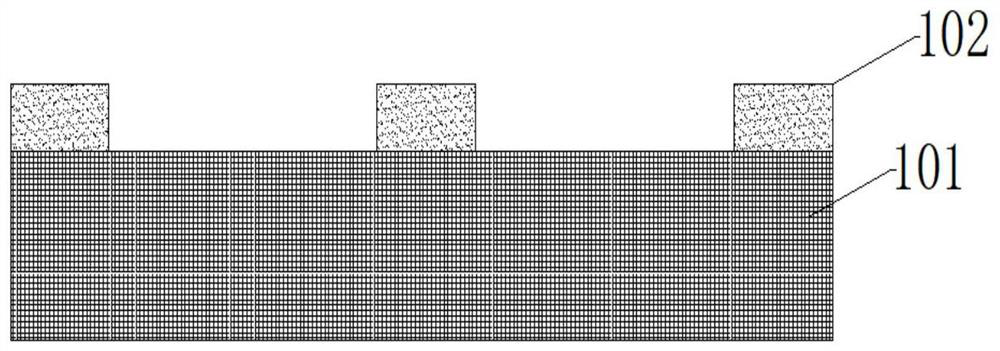

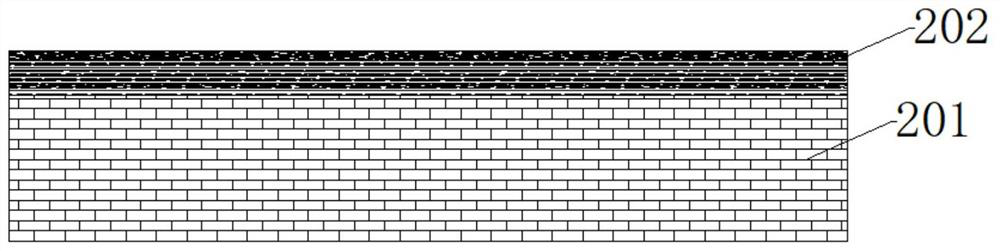

[0038] Such as Figure 1-6 As shown, this embodiment provides a method for heterogeneous integration of a compound semiconductor and a silicon-based complementary metal oxide semiconductor wafer. The compound semiconductor may specifically be an indium phosphide sheet, which includes a compound semiconductor substrate 101 and a compound semiconductor substrate 101 The epitaxial layer 102 deposited on the surface of the bottom 101, the silicon-based complementary metal oxide semiconductor wafer is a silicon-based wafer processed by a CMOS process, including the following steps:

[0039] Selective etching of the compound semiconductor epitaxial layer 102, specifically, etching along the longitudinal and lateral directions of the compound semiconductor epitaxial layer 102 until the surface of the compound semiconductor substrate 101 is exposed, so as to form criss-cross etch grooves on the compound semiconductor ;

[0040] Form a bonding dielectric layer 103 on the etched surfac...

Embodiment 2

[0046] This embodiment provides a method for heterogeneous integration of a compound semiconductor and a silicon-based complementary metal oxide semiconductor wafer. The compound semiconductor may specifically be a gallium arsenide wafer, which includes a compound semiconductor substrate and a compound semiconductor substrate deposited on the surface of the compound semiconductor substrate. The epitaxial layer, the silicon-based complementary metal oxide semiconductor wafer is a silicon-based wafer processed by a CMOS process, including the following steps:

[0047] Selectively etching the compound semiconductor epitaxial layer, specifically, etching along the longitudinal and lateral directions of the compound semiconductor epitaxial layer until the surface of the compound semiconductor substrate is exposed, so as to form criss-cross etch grooves on the compound semiconductor;

[0048] Form a bonding dielectric layer on the etched surface of the epitaxial layer and the inner g...

Embodiment 3

[0054] This embodiment provides a method for heterogeneous integration of a compound semiconductor and a silicon-based complementary metal oxide semiconductor wafer. The compound semiconductor may specifically be a gallium arsenide wafer, which includes a compound semiconductor substrate and a compound semiconductor substrate deposited on the surface of the compound semiconductor substrate. The epitaxial layer, the silicon-based complementary metal oxide semiconductor wafer is a silicon-based wafer processed by a CMOS process, including the following steps:

[0055] Selectively etching the compound semiconductor epitaxial layer, specifically, etching along the longitudinal and lateral directions of the compound semiconductor epitaxial layer until the surface of the compound semiconductor substrate is exposed, so as to form criss-cross etch grooves on the compound semiconductor;

[0056] Form a bonding dielectric layer on the etched surface of the epitaxial layer and the inner g...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More