Transistor and preparation method thereof

A transistor and modulation technology, which is applied in the field of transistors and their preparation, can solve problems such as poor reliability and characteristic degradation, and achieve the effects of reducing electric field strength, improving device reliability, and avoiding device characteristic degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

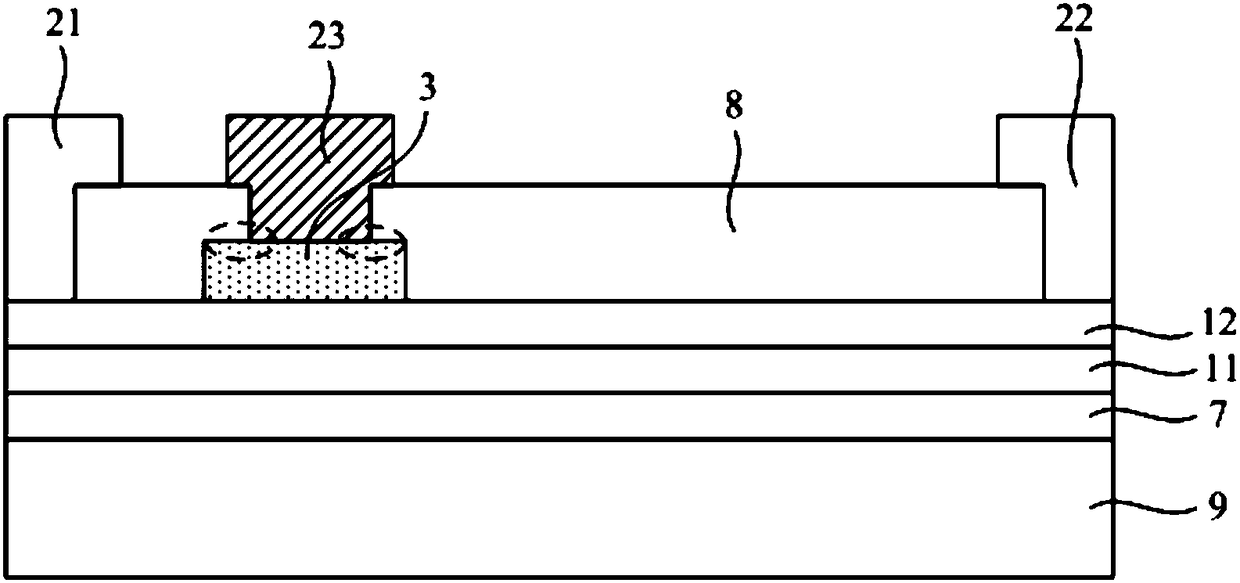

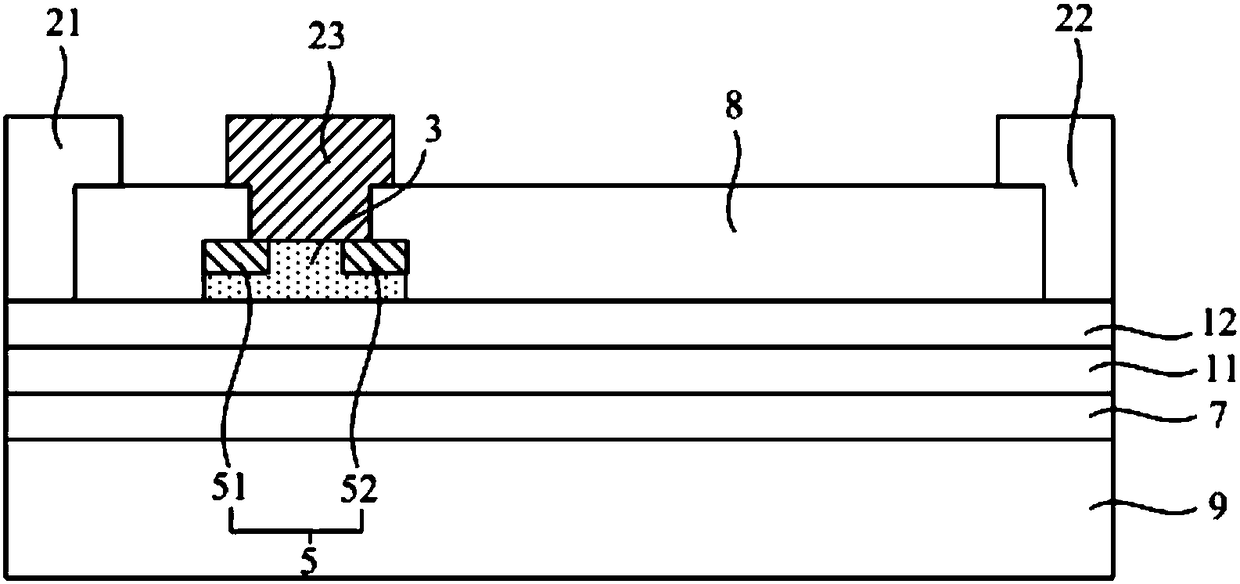

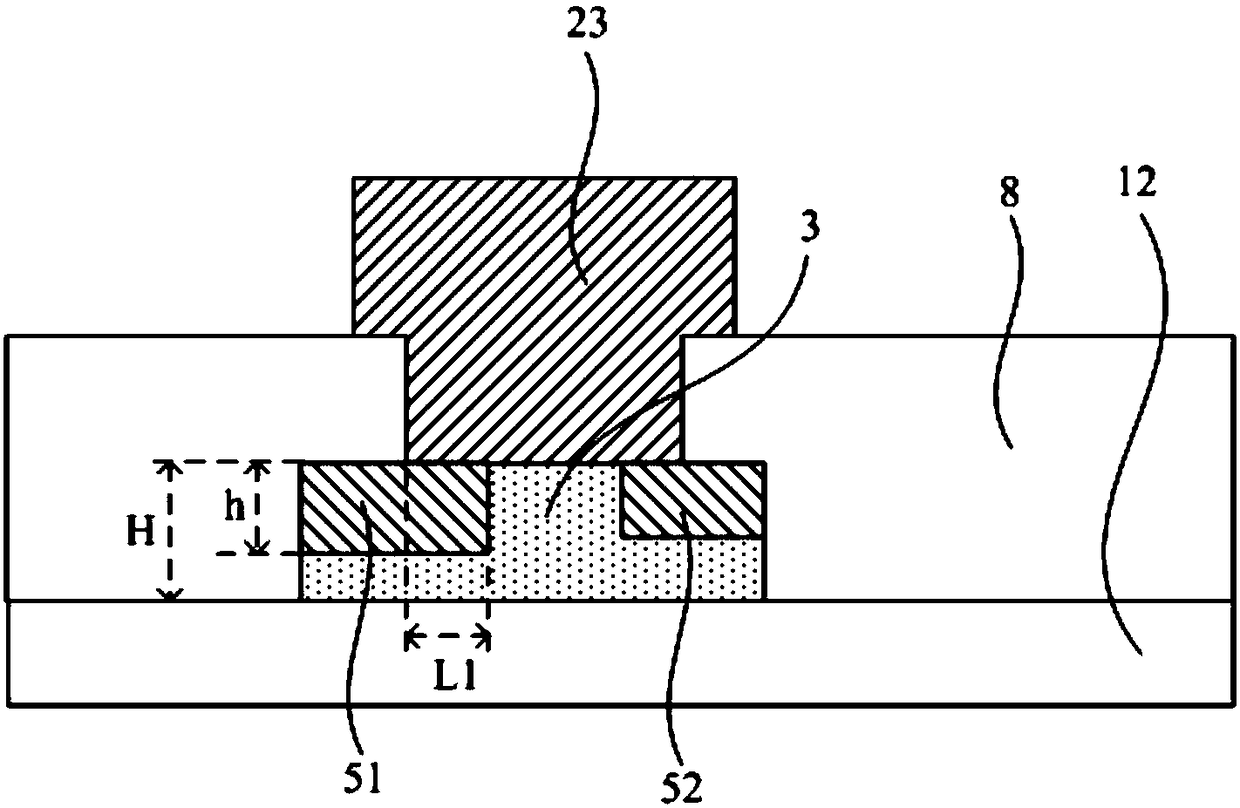

[0039] Such as Figure 2 to Figure 7 As shown, this embodiment provides a transistor, which includes:

[0040] stacked channel layer 11 and barrier layer 12;

[0041] The source 21, the drain 22, and the gate 23 are arranged at intervals on the side of the barrier layer 12 away from the channel layer 11; wherein, the gate 23 is located between the source 21 and the drain 22, and is provided between the barrier layer 12 There is a P-type cap layer 3, and a Schottky contact is formed between the P-type cap layer 3 and the gate 23;

[0042] Such as figure 2 As shown, the transistor of this embodiment includes a stacked channel layer 11 and a barrier layer 12, a heterojunction is formed between the channel layer 11 and the barrier layer 12, and the barrier layer 12 has a larger forbidden band width , so that a two-dimensional electron gas (2DEG) can be formed on the side of the heterojunction interface close to the channel layer 11 . On the side of the barrier layer 12 away f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More