A kind of mosfet that improves UIS avalanche tolerance and preparation method thereof

An avalanche tolerance and consistent technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of low avalanche breakdown tolerance, achieve the effect of improving avalanche tolerance and robustness, and improving breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

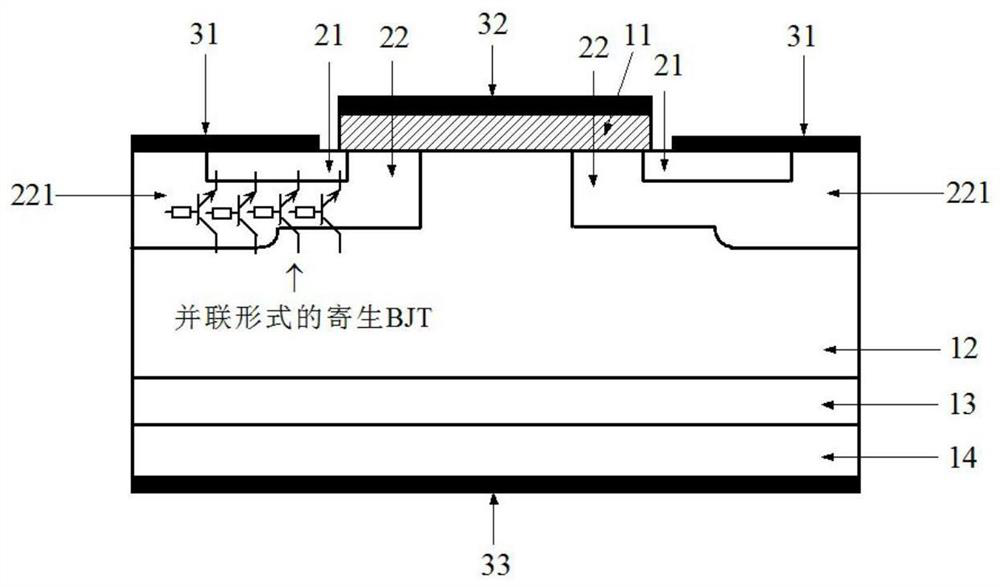

[0042] combine figure 2 , 3 , a MOSFET for improving UIS avalanche tolerance in this embodiment includes a second conductivity type doped source region 21, a first conductivity type doped base region 22 and a semi-insulating region 222, and a second conductivity type doped source region 22. The region 21 is located on top of the semi-insulating region 222 , and the base region 22 doped with the first conductivity type is located on the side of the source region 21 and the semi-insulating region 222 doped with the second conductivity type.

[0043] The existence of the semi-insulating region 222 reduces the area where parasitic BJTs exist, that is, reduces the number of parasitic BJTs, but there are still a small amount of parasitic BJTs under the channel region, but due to the great reduction in the number of parasitic BJTs, the Under UIS conditions, the current in the MOSFET limits the temperature increase, and the avalanche breakdown time of the MOSFET is increased from th...

Embodiment 2

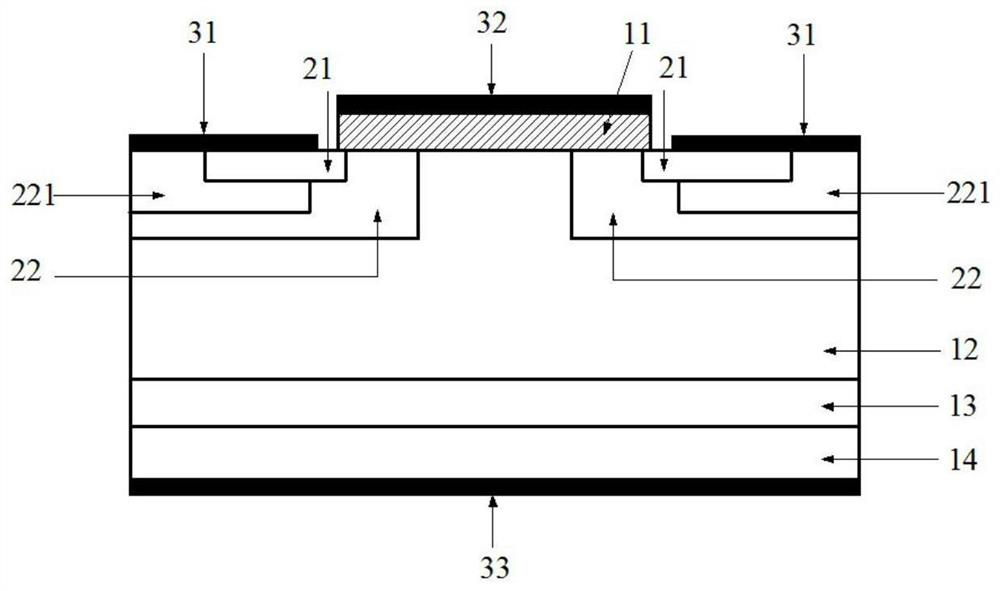

[0048] combine figure 2 , 3 , a MOSFET with improved UIS avalanche tolerance in this embodiment is further improved on the basis of Embodiment 1. The depth of the base region 22 doped with the first conductivity type is the same as the depth of the source region 21 and the semi-insulating region doped with the second conductivity type. The sum of the heights of the regions 222 is equal. The width ratio of the base region 22 doped with the first conductivity type and the source region 21 doped with the second conductivity type is 1:1-3. For specific applications, you can choose values such as 1:1; 1:2; 1:3; 1:1.5; 1:2.8.

[0049] Precisely control the effective width of the conductive channel formed by the base region 22 doped with the first conductivity type, and does not change due to the introduction of the semi-insulating region 222 to ensure the threshold voltage, on-resistance, transconductance, output characteristics, etc. of the MOSFET The parameters do not change...

Embodiment 3

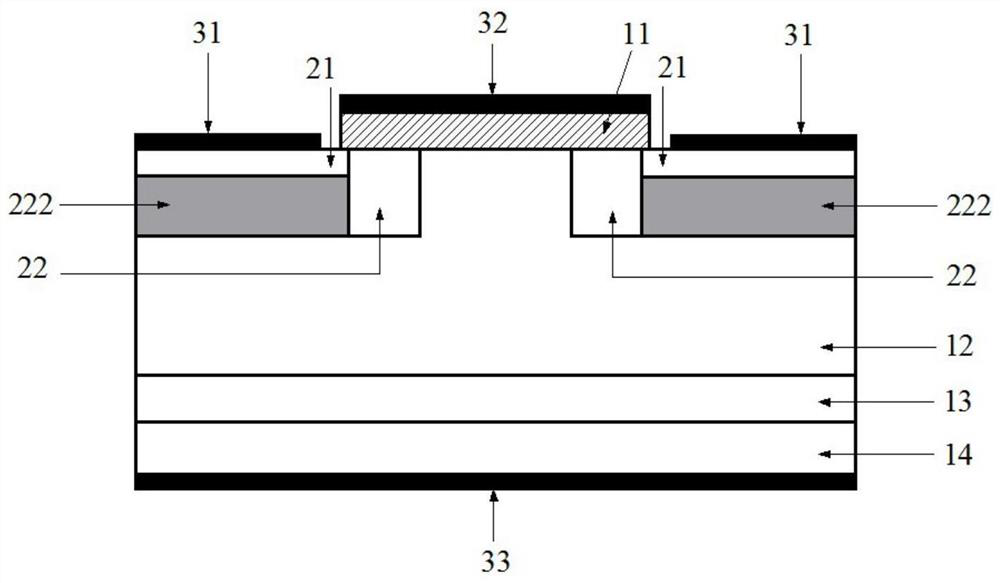

[0051] combine figure 2 , 3 , a MOSFET with improved UIS avalanche tolerance in this embodiment is further improved on the basis of Embodiments 1 and 2. The width of the source region 21 doped with the second conductivity type is the same as the width of the semi-insulating region 222 .

[0052] It is ensured that the effective channel length of the MOSFET does not change due to the introduction of the semi-insulating region 222, and that parameters such as threshold voltage, on-resistance, transconductance, and output characteristics of the MOSFET do not change due to the introduction of the semi-insulating region.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More