CPCI bus test device and method

A technology for bus testing and test results, which is applied in the direction of error detection/correction and faulty computer hardware and instrument detection, and can solve the problems of high labor costs and low efficiency of bus detection, so as to reduce labor costs, realize automated testing, The effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

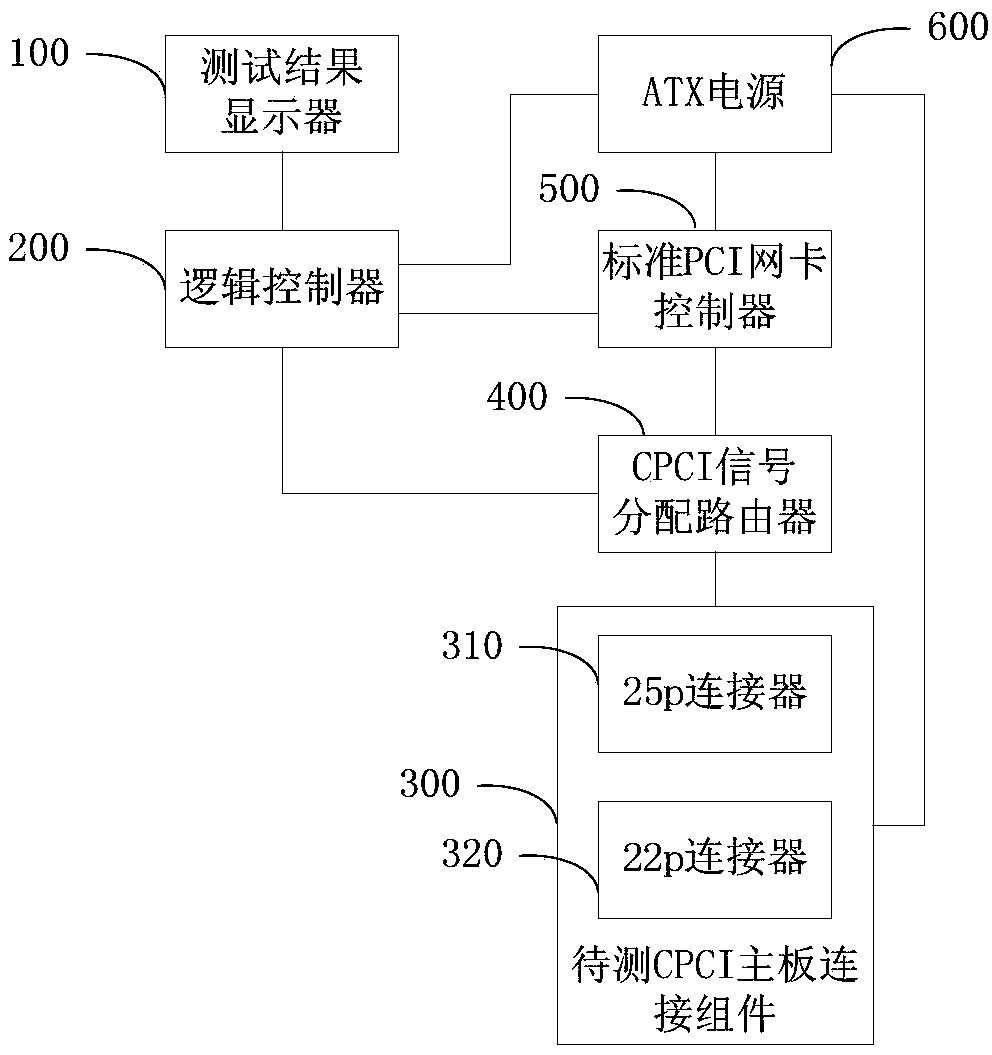

[0033] see figure 1 , a structural diagram of a CPCI bus testing device provided by an embodiment of the present invention. A kind of CPCI bus testing device that the embodiment of the present invention provides, comprises: test result display 100, logic controller 200, to-be-tested CPCI motherboard connection assembly 300, CPCI signal distribution router 400, standard PCI network card controller 500 and ATX power supply 600. The test device adopts the connection component of the CPCI motherboard to be tested to provide an external standard 6U CPCI slot for installing the CPCI motherboard to be tested. After completing the basic connection, start the test. for an intuitive display.

[0034] The logic controller 200 is connected with the ATX power supply 600, the standard PCI network card controller 500 and the CPCI signal distribution router 400 respectively, and the standard PCI network card controller 500, the CPCI signal distribution router 400, and the CPCI motherboard co...

Embodiment 2

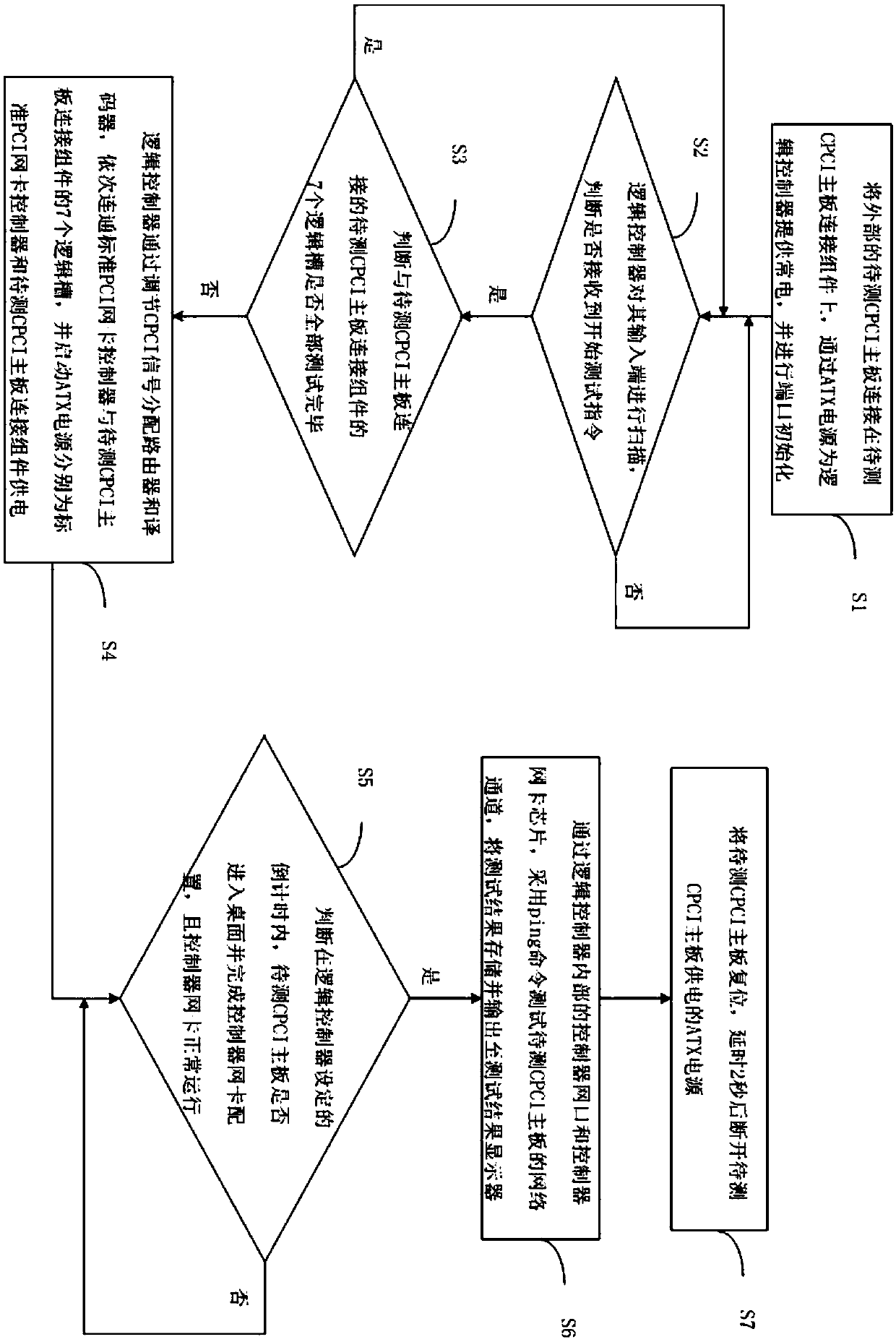

[0042] see figure 2 , a flowchart of a CPCI bus testing method provided by an embodiment of the present invention. A kind of CPCI bus testing method that the embodiment of the present invention provides, comprises:

[0043] Step 1: Connect the external CPCI motherboard to be tested to the CPCI motherboard connection component to be tested, provide constant power to the logic controller through the ATX power supply, and perform port initialization. The logic controller is the STM32F107VCT6 ARM microcontroller of ST Company, which is used to connect the standard PCI network card to the tested 6U CPCI motherboard in sequence, and is also used to store and display the test results on the test result display. Further, the logic controller includes a controller network port and a controller network card; the controller network port and the controller network card are connected to a standard PCI network card controller. Further, the connection components of the CPCI motherboard to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More