Reconfigurable chip architecture for high-traffic network processing

A technology of network processing and large traffic, applied in the field of reconfigurable chip architecture, can solve the problems of long development cycle, high replacement cost, strong hardware dependence, etc., and achieve the effects of improving processing speed, protecting equipment investment, and facilitating development

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be further introduced below in conjunction with the accompanying drawings and specific embodiments.

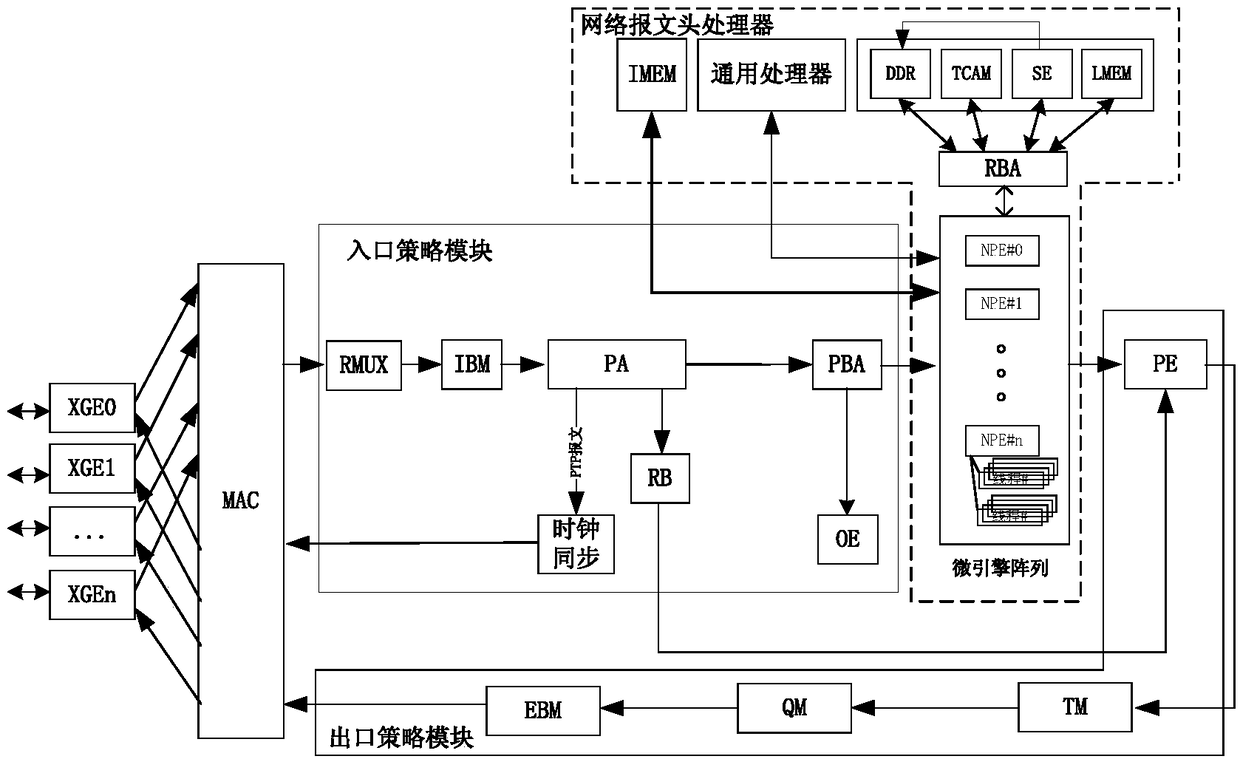

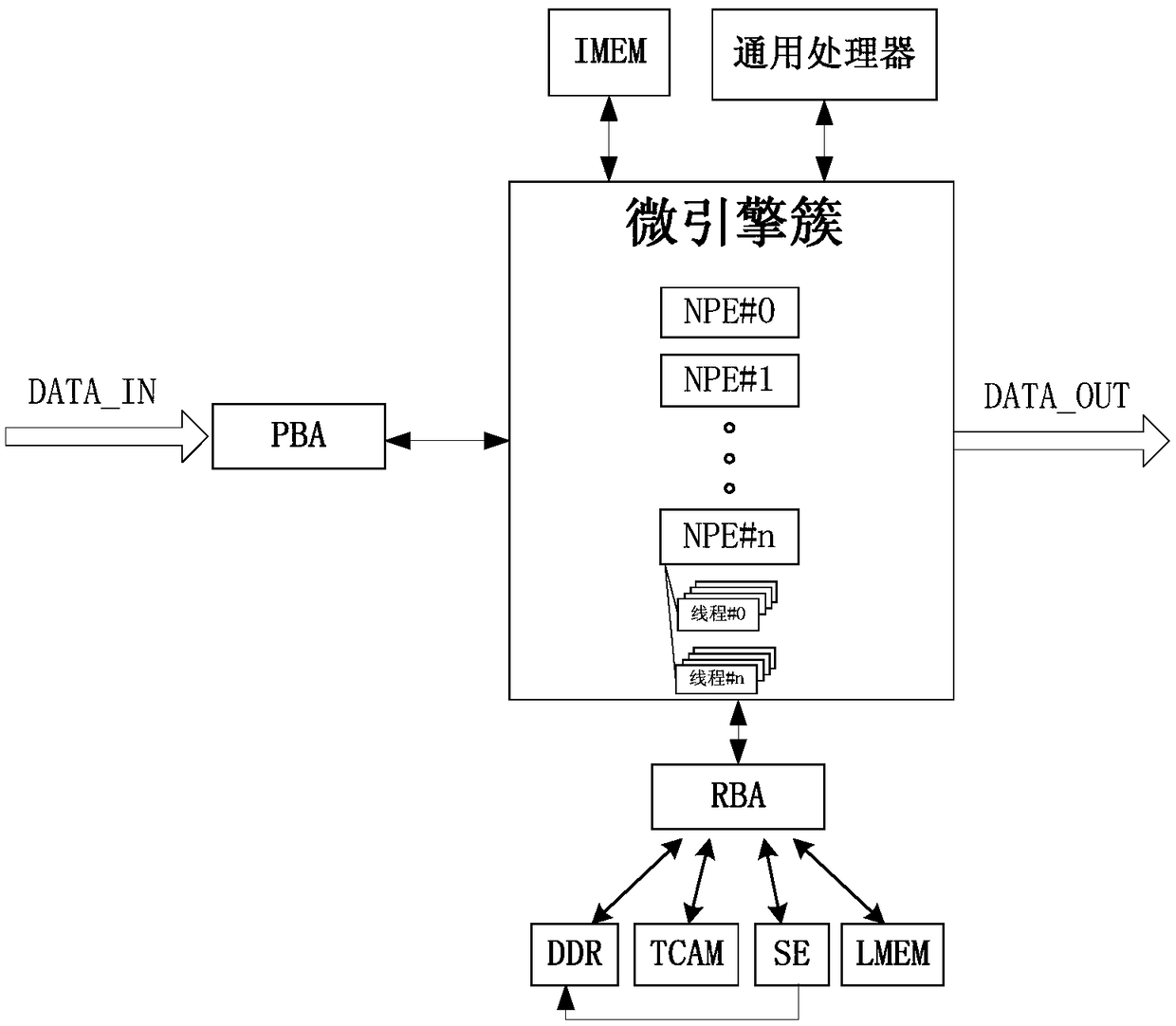

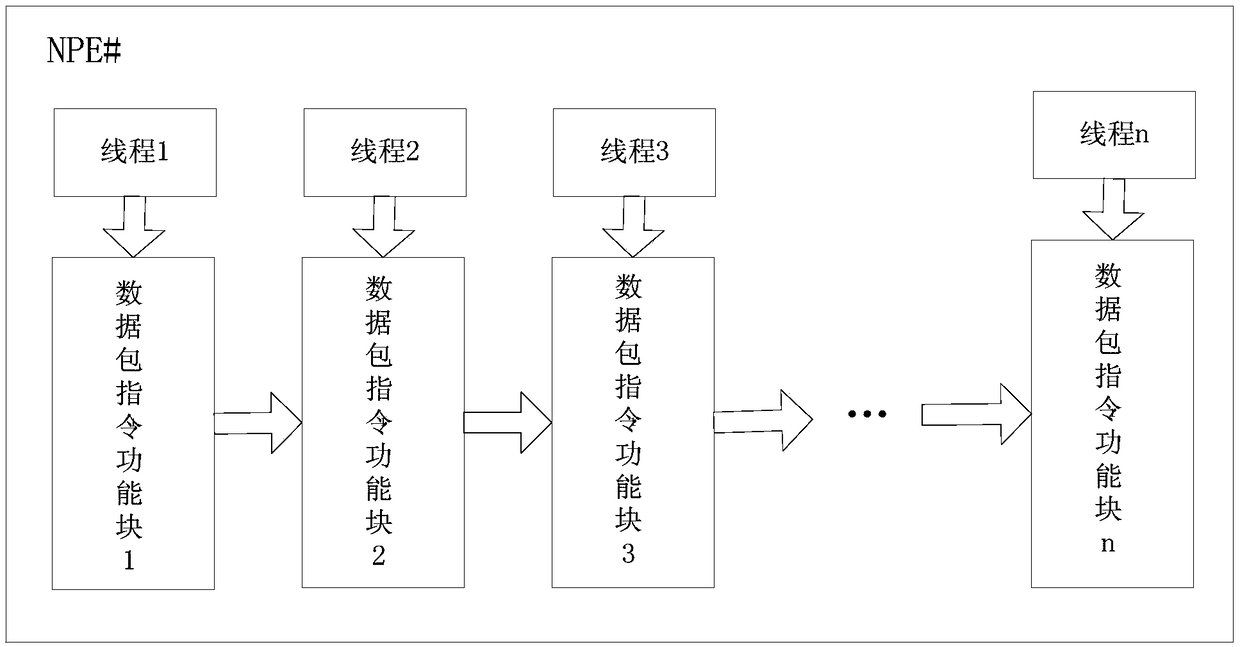

[0045] The present invention provides a large-scale network data processing system based on a reconfigurable switching chip architecture. The system includes XGE1-XGEn ports, a MAC module, an entry policy module, a network message header processor, and an exit policy module; wherein:

[0046] XGE (Ten-Gigabit Etherent) 1~XGEn ports, receive the message, and mark the time stamp of the message arrival time, form a message with a time stamp and send it to the MAC module; forward the data sent by the MAC module;

[0047] The MAC module identifies, checks and filters each message with a time stamp, filters out invalid messages, stores the remaining valid messages in the receiving buffer, and forwards them to the ingress policy module; The message sent by the egress policy module is stored in the sending buffer, and then the data is read from the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com