Coprocessor, and method and system for matrix operation acceleration

A technology of co-processor and matrix operation, which is applied in the computer field and can solve problems such as poor computing power

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

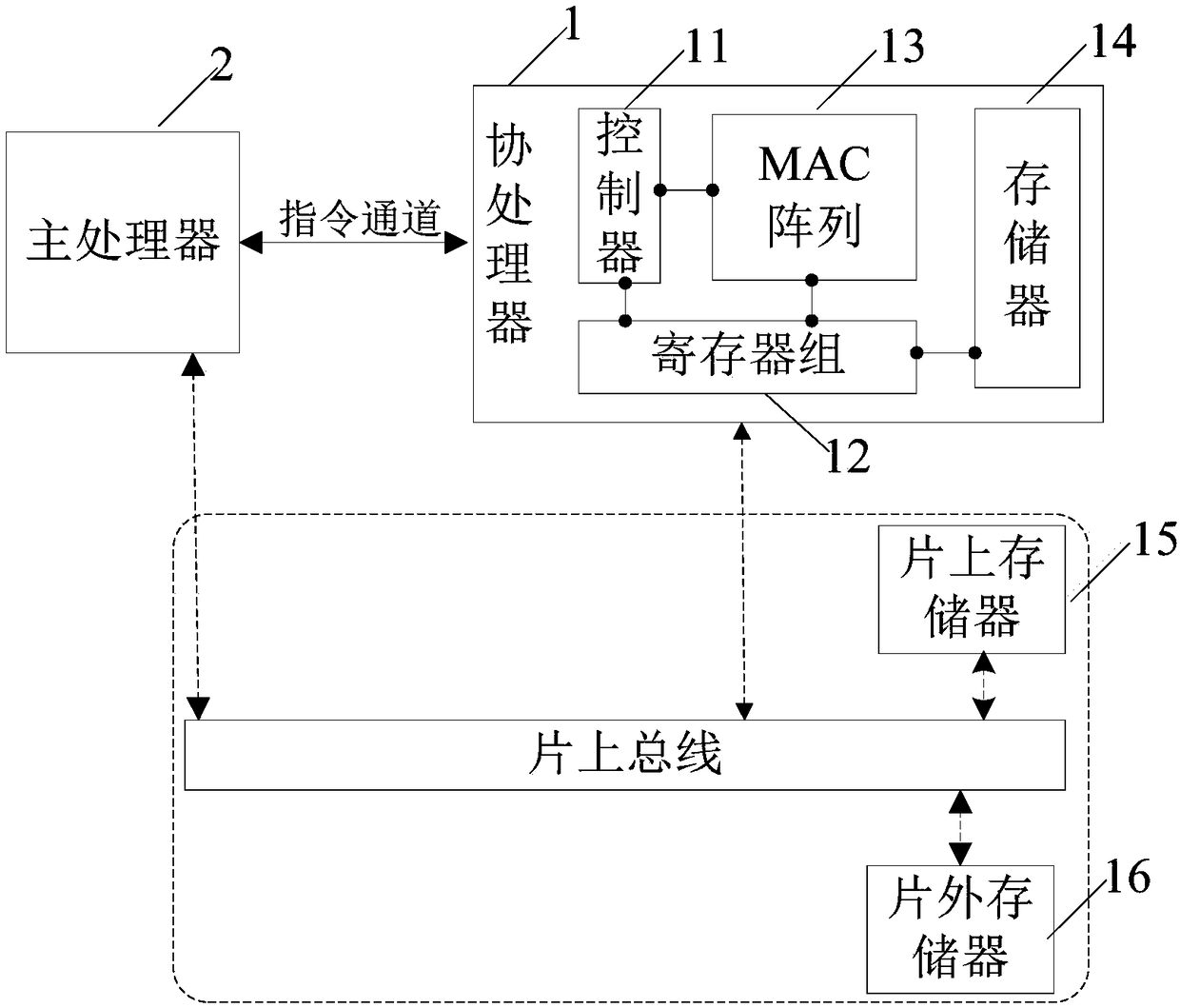

[0032] figure 1 A schematic structural diagram of the coprocessor provided by the embodiment of the present application is shown, as shown in figure 1 As shown, the co-processing 1 includes a controller 11, a register set 12, a MAC array 13 and a memory 14, wherein,

[0033] The controller 11 is connected to the MAC array 13 and the register set 12 respectively;

[0034] The register group 12 is also connected to the memory 14, and the group number of the register group 12 is greater than 1;

[0035] The coprocessor 1 communicates with the main processor 2 through an instruction channel. The interaction between the main processor 2 and the coprocessor 1 at the interface for transmitting instructions follows the coprocessing interface rules of the general processor.

[0036] The controller 11 is used to analyze the vector extension instruction received by the coprocessor 1, and is also used to call and send the data to be operated to the register group 12 according to the an...

Embodiment 2

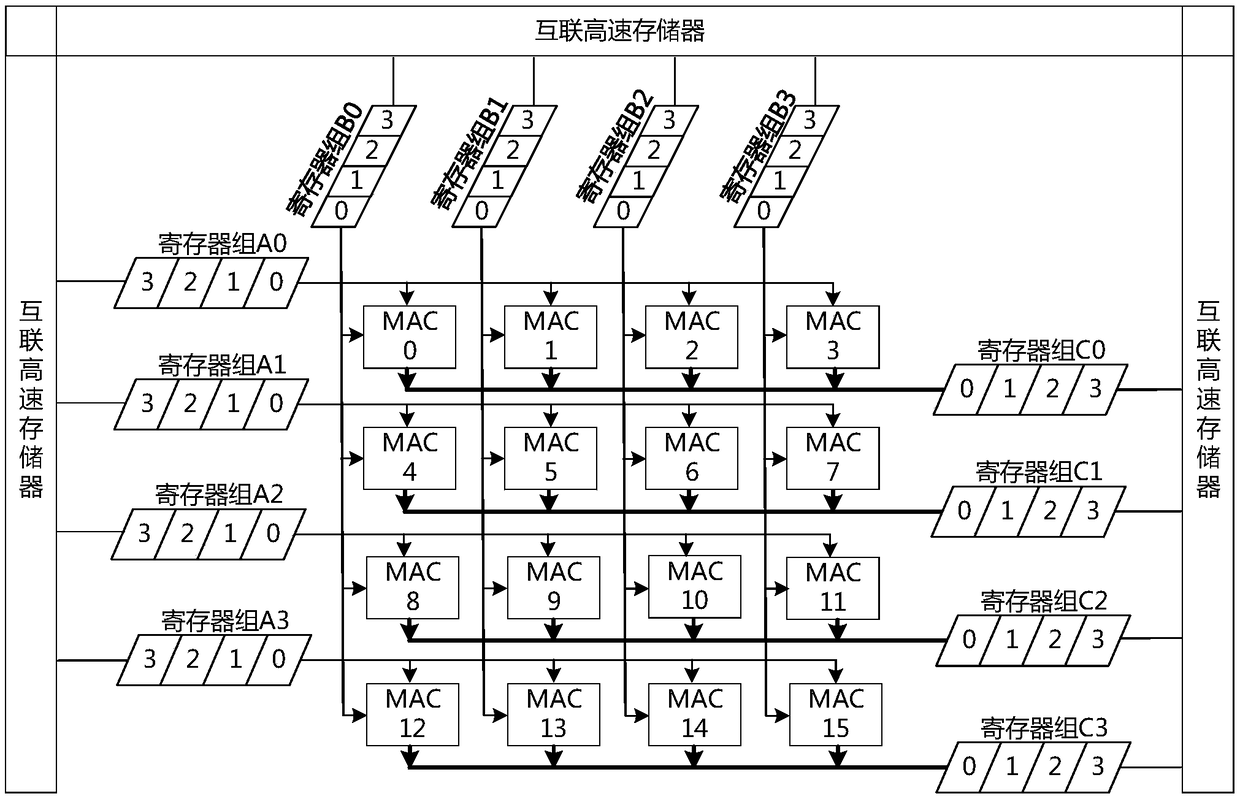

[0053] In another embodiment provided by the present application, the MAC array includes m*n MACs, and the m*n MACs are arranged in a two-dimensional matrix structure to form the MAC array, where m and n are not less than 3 positive integer of .

[0054] Further, the arrangement structure of the register set is consistent with the arrangement structure of the MAC array, that is, it consists of m*n registers.

[0055] In this embodiment, each vector extension instruction parsed by the controller 11 includes a data transfer instruction and a matrix operation instruction. The data transfer instruction is used to instruct the register bank 12 to forward the data to be operated to the MAC array 13, and is also used to Instruct the register set 12 to forward the operation result of the MAC array 13 to the memory 14; the matrix operation instruction is used to instruct the MAC array 13 to perform a matrix operation on the received data to be processed, and the matrix operation instru...

Embodiment 3

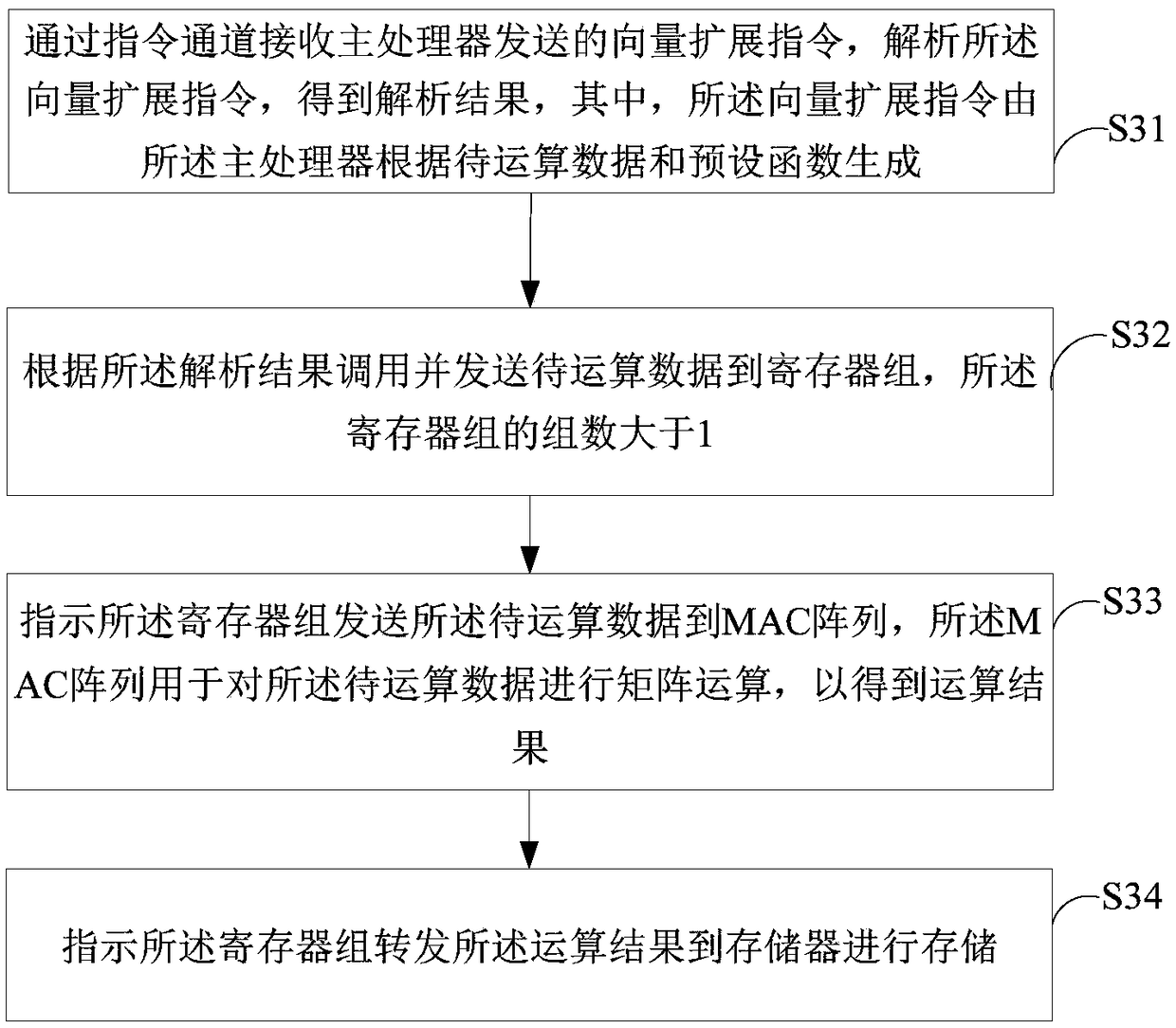

[0068] Corresponding to the coprocessor described in the above embodiment, image 3 It shows the implementation flowchart of the matrix operation acceleration method provided by the embodiment of the present application, and the details are as follows:

[0069] The matrix operation acceleration method runs in the coprocessor provided in Embodiment 1 or Embodiment 2, including:

[0070] Step S31, receiving the vector extension instruction sent by the main processor through the instruction channel, analyzing the vector extension instruction, and obtaining an analysis result, wherein the vector extension instruction is generated by the main processor according to the data to be operated and a preset function;

[0071] In the embodiment provided by the present application, the coprocessor receives the vector extension instruction through the instruction channel, and after the coprocessor receives the vector extension instruction, the controller configured therein analyzes the vect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More