Chip on film package

A chip-on-film and package technology, applied in the field of chip-on-film packages, can solve problems such as limiting integrated circuits and chip space.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0079] Reference will now be made in detail to the presently preferred embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used in the drawings and description to refer to the same or like parts.

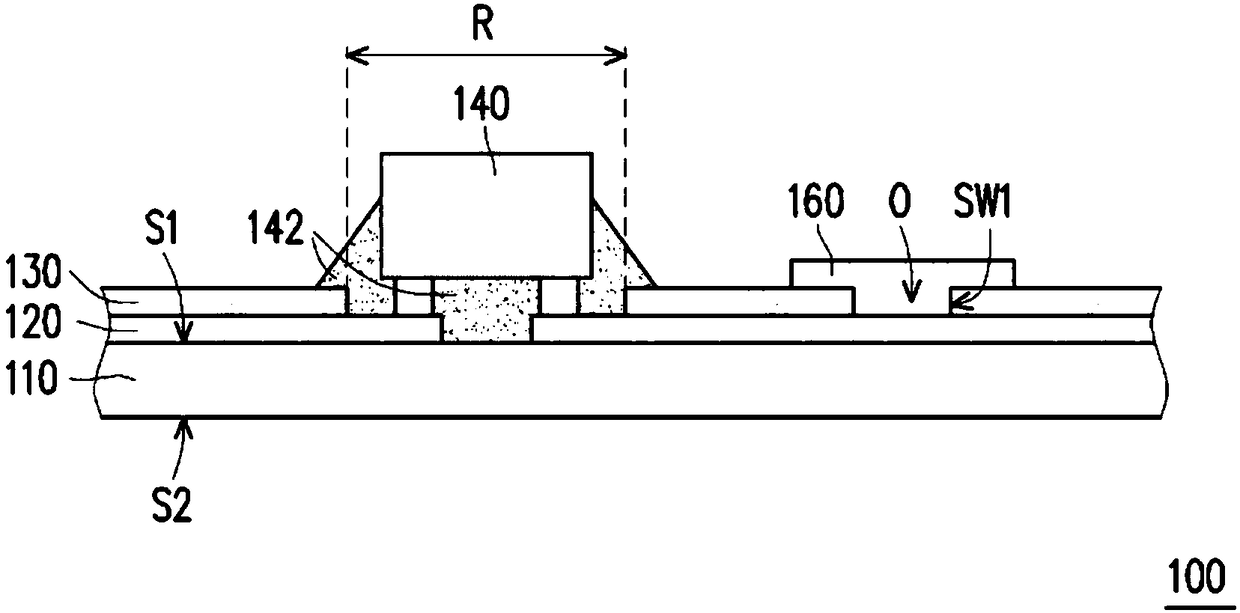

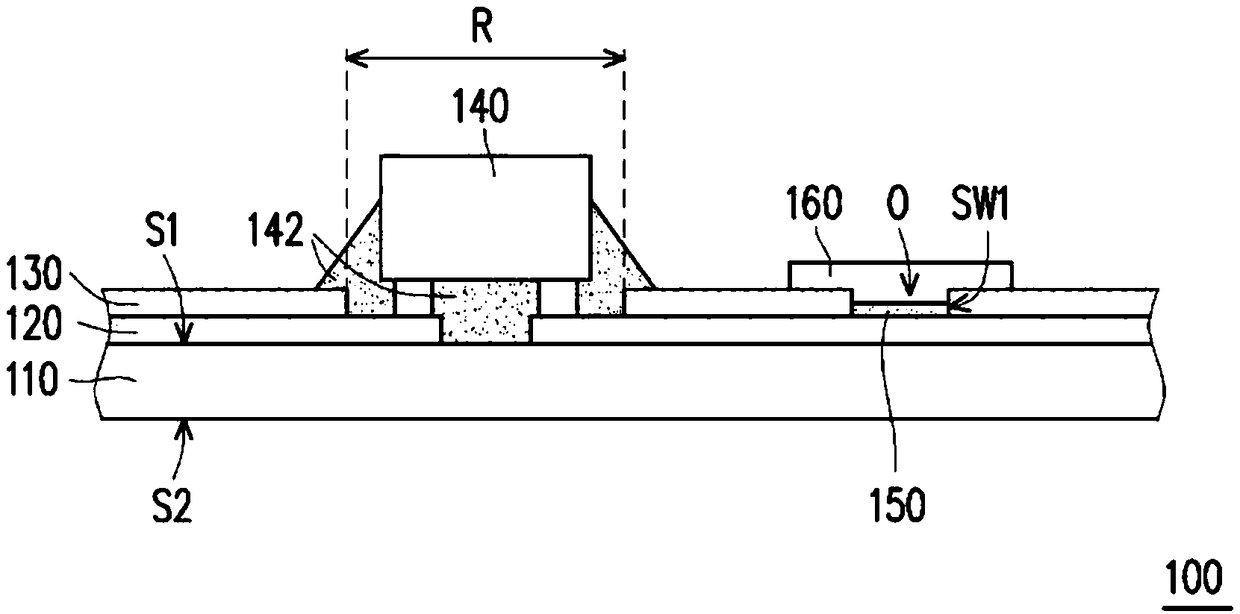

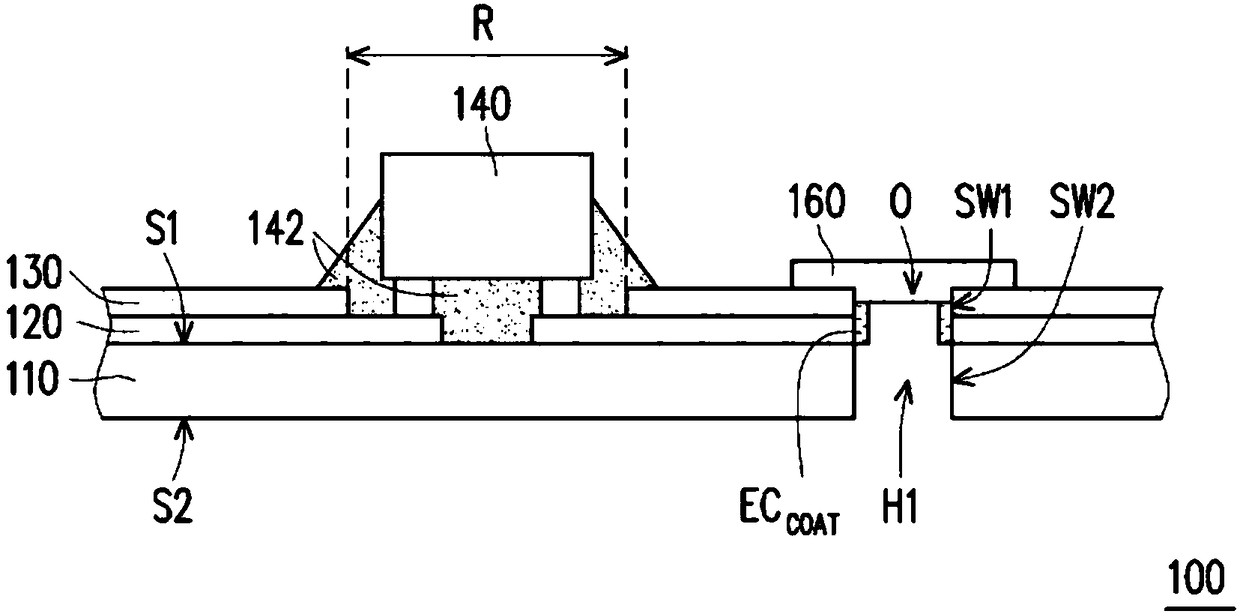

[0080] Figures 1A to 1E Each is a cross-sectional view of a chip-on-film package according to an embodiment of the present invention. Figure 2A to Figure 2B are top views of chip-on-film packages according to embodiments of the present invention, respectively. It should be noted that Figure 1A to Figure 1E each of which is Figure 2A to Figure 2B A cross-sectional view of either one along line A-A'.

[0081] refer to Figure 1A , in this embodiment, the chip-on-film package 100 includes a base film 110 , a patterned circuit layer 120 , a first solder resist layer 130 , a chip 140 and a first conductive film 160 . The base film 110 includes a first surface S1 and a mounting region ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More