A DDR management and control system based on FPGA hardware acceleration

A management control and hardware acceleration technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve the problems of unclear storage information, complex operation modes, low system bandwidth, etc., to speed up data transmission efficiency and improve data processing efficiency. , The effect of reducing CPU usage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The technical solution of the present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments, and the following embodiments do not constitute a limitation of the present invention.

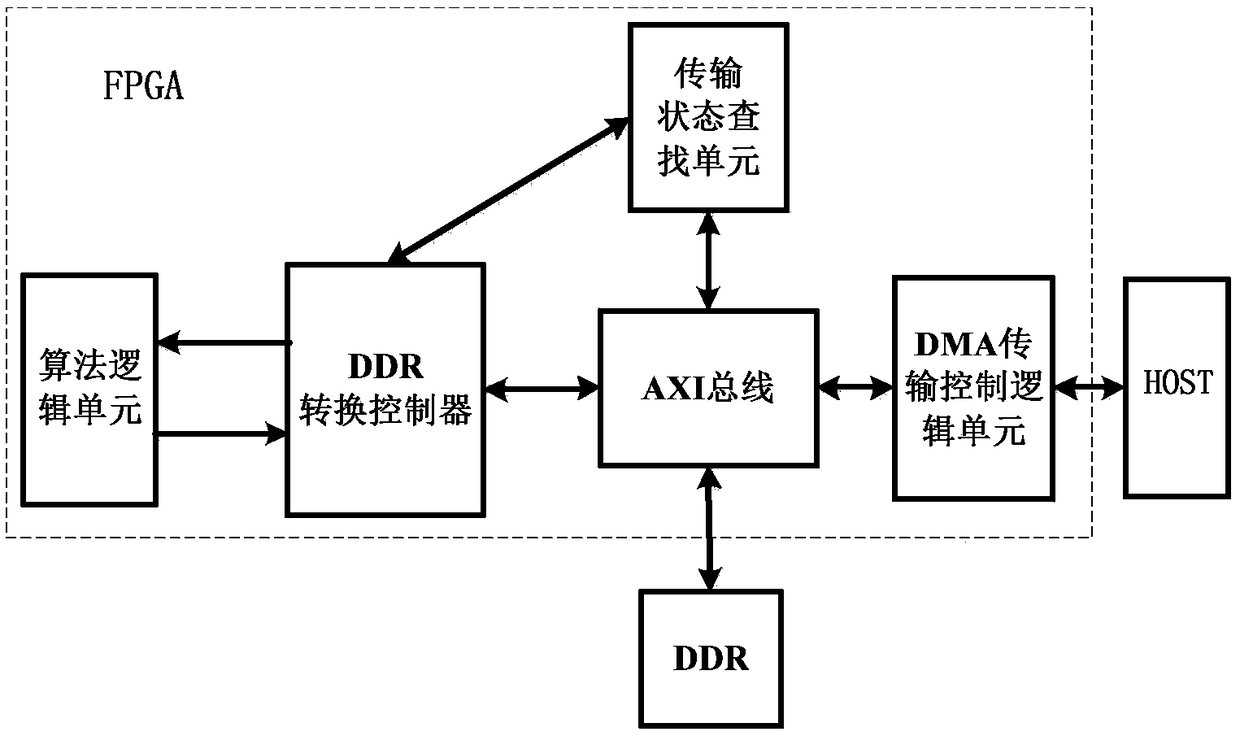

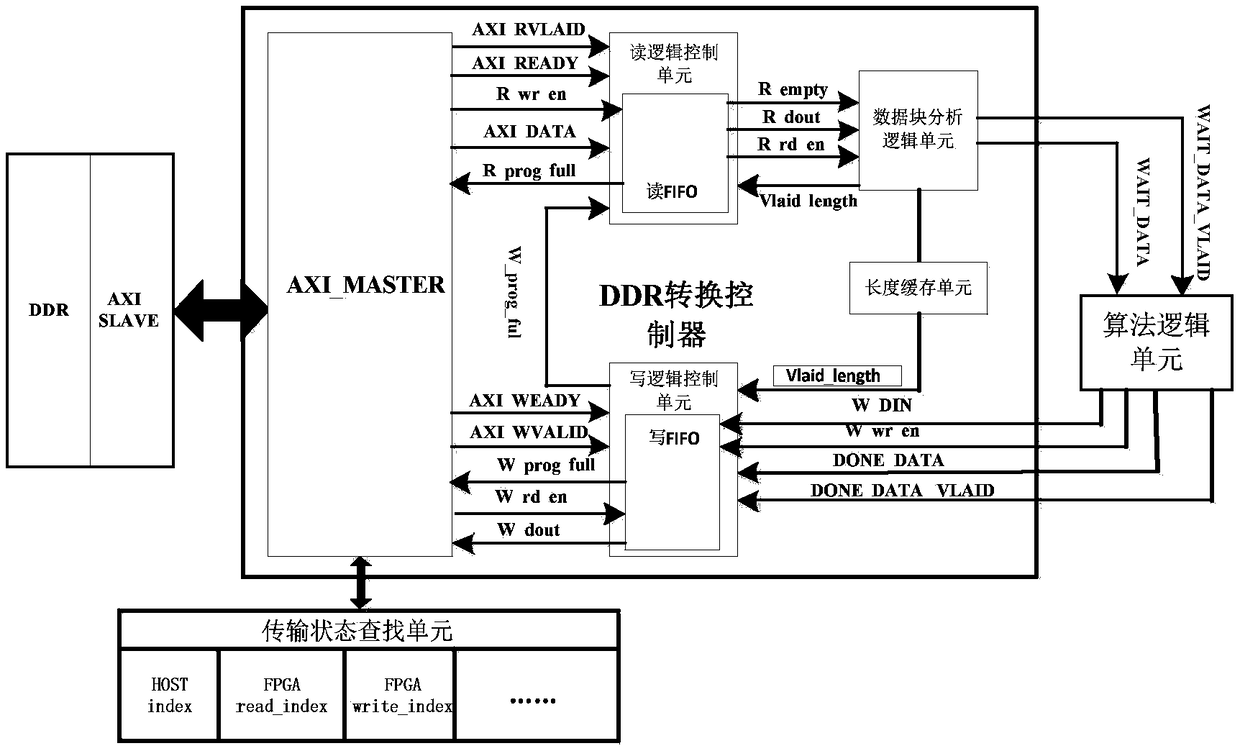

[0034] Such as figure 1Shown, a kind of DDR management and control system based on FPGA hardware acceleration comprises host end (HOST), FPGA end and memory DDR, and described FPGA end comprises the DMA transmission control logic unit connected by AXI bus line, DDR conversion controller, transmission A state search unit, and an algorithm logic unit connected to the DDR conversion controller, the FPGA end is connected to the host end through the DMA transfer control logic unit, the FPGA end is connected to the memory DDR through the AXI bus, and the DDR conversion control The device is connected with the transmission status lookup unit, wherein:

[0035] The DMA transmission control logic unit is based on the DMA data transmission m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More