A memory cell and a memory array and an OTP formed by the memory cell and the memory array

A technology of memory cells and drains, applied in the field of memory arrays and memory cells of one-time programmable read-only memory, can solve the problems of complicated wiring, unfavorable miniaturization, large area, etc., so as to improve the design margin and save the area. , the effect of halving the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

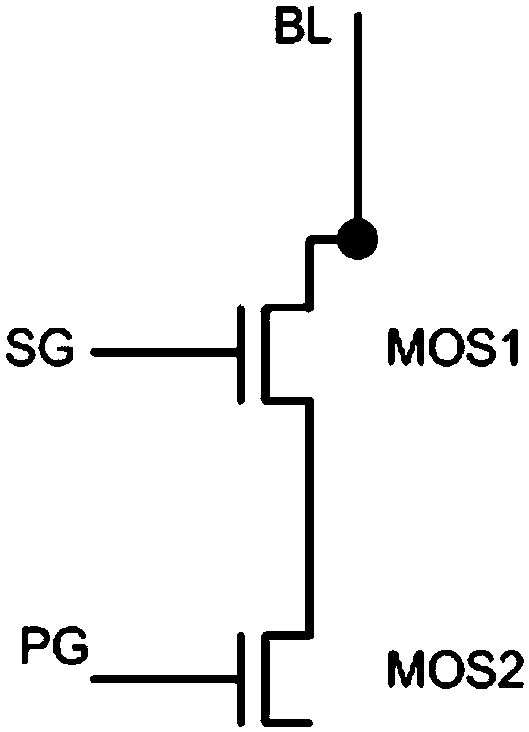

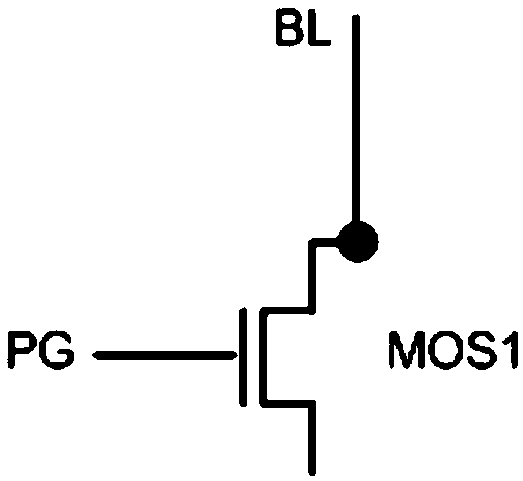

[0079] Such as figure 2 As shown, the storage unit provided by the present invention is composed of an NMOS;

[0080] In programming mode, the gate of the NMOS is connected to a preset voltage, and the preset voltage is greater than or equal to the breakdown voltage of the NMOS.

[0081] In read mode, the NMOS drain is connected to 0V voltage, and the NMOS gate is connected to the circuit voltage.

[0082] If the measured NMOS gate-to-drain current value is less than the first threshold of 10 nanoampere-100 nanoamperes, it is judged that the memory cell has not been programmed; if the measured NMOS gate-to-drain current value is greater than the second threshold value of 0.1 mA -1mA judges that the memory cell is programmed. An unprogrammed memory cell represents a data 0, and a programmed memory cell represents a data 1.

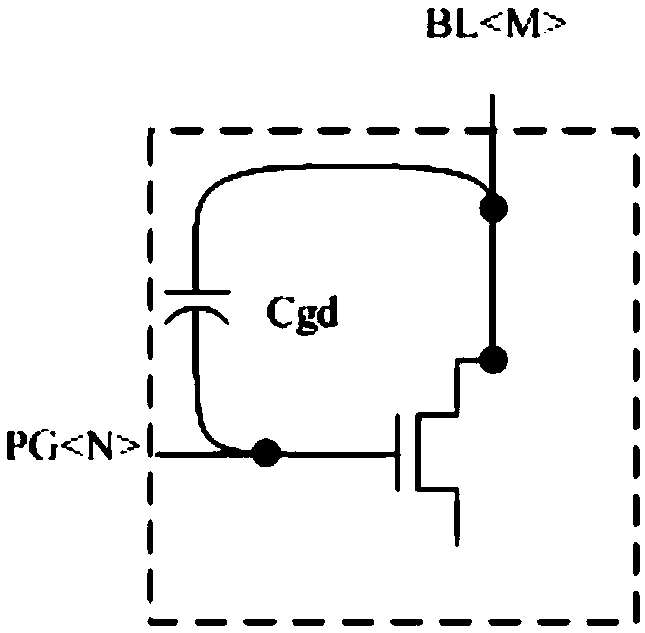

[0083] Such as Figure 5 As shown, the present invention provides a storage array composed of the storage units, the storage array is an n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More