A multi-level low-latency interconnect structure based on axi protocol

An interconnection structure and multi-level technology, applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problem of low data throughput rate of data consistency interconnection bus, achieve the effect of improving performance, improving effective bandwidth, and increasing transmission bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described below in conjunction with the accompanying drawings.

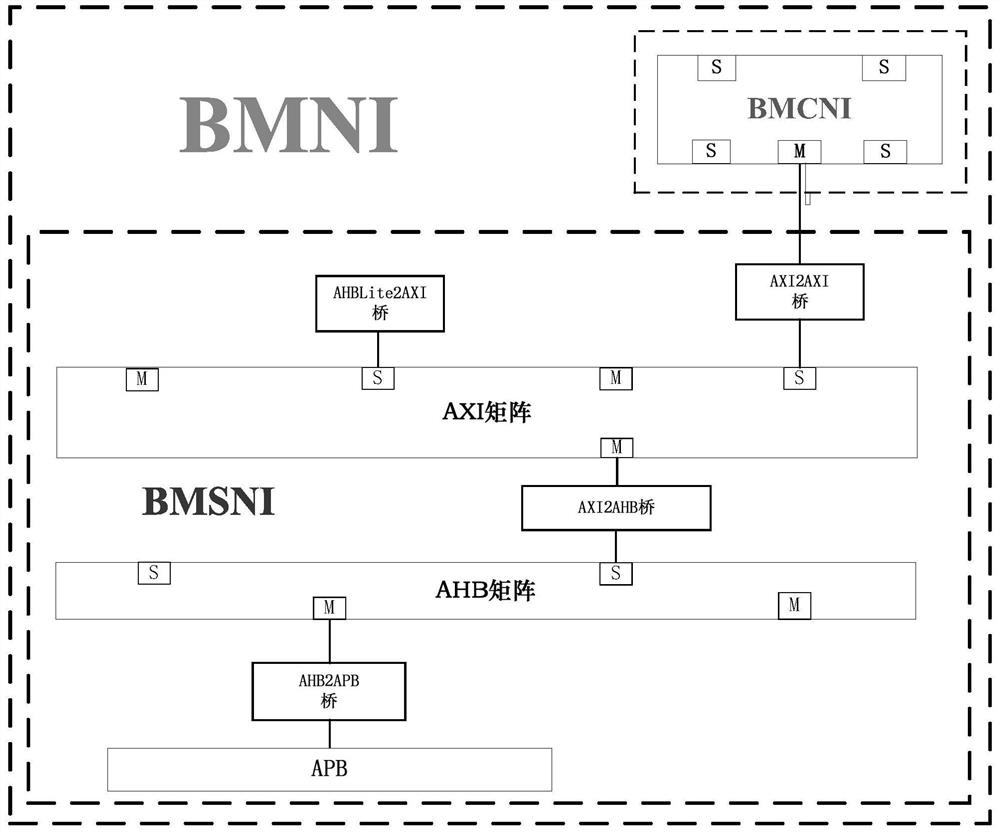

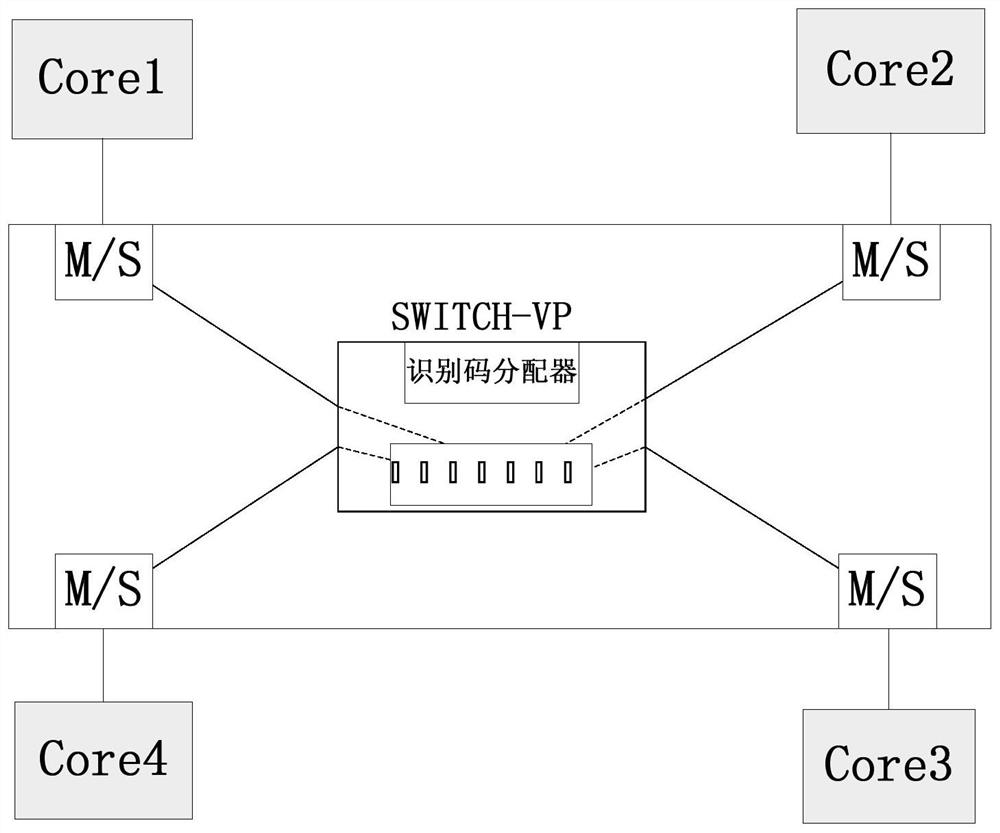

[0029] Such as figure 1 As shown, the multi-level low-delay interconnection structure of the present invention is mainly composed of two parts: a high-throughput low-delay inter-core bus interconnection unit BMCNI and a multi-level parallel multiplexing on-chip bus interconnection unit BMSNI; the multi-level low-delay interconnection structure BMNI includes AMBA multi-level interconnection structure, AMBA slave device interface, AMBA master device interface and multiple conversion bridges.

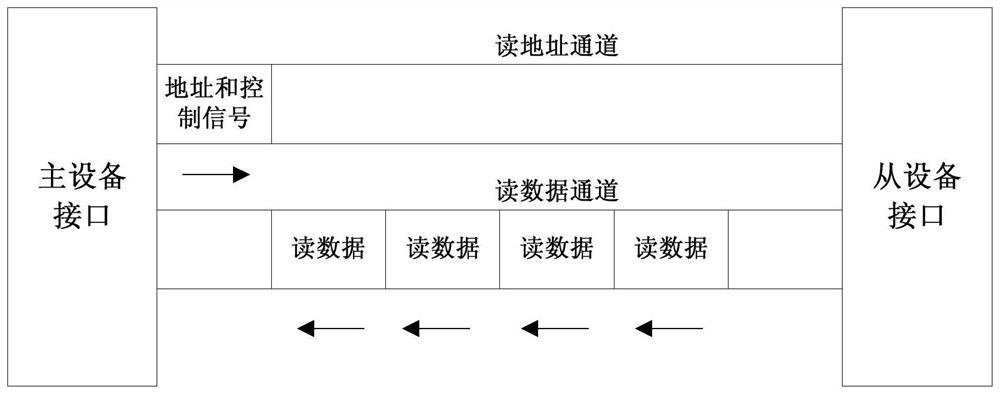

[0030] AMBA multi-level interconnection structure includes AXI bus matrix switch and AHB bus switch; AXI bus matrix switch is used to connect AXI master device and AXI slave device, establish efficient communication between AXI master device and AXI slave device, through AXI master device interface Connect AXI slave device, connect AXI master device through AXI slave device interf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More