SOC chip field programmable logic array prototype integration method and system

A kind of programming logic, 1. SOC technology, applied in the field of SOC chip field programmable logic array prototype synthesis, can solve the problems of low reliability, low reusability, low scalability, etc., achieve high degree of automation, improve efficiency, expand good sex effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] In order to fully understand the technical content of the present invention, the technical solutions of the present invention will be further introduced and illustrated below in conjunction with specific examples, but not limited thereto.

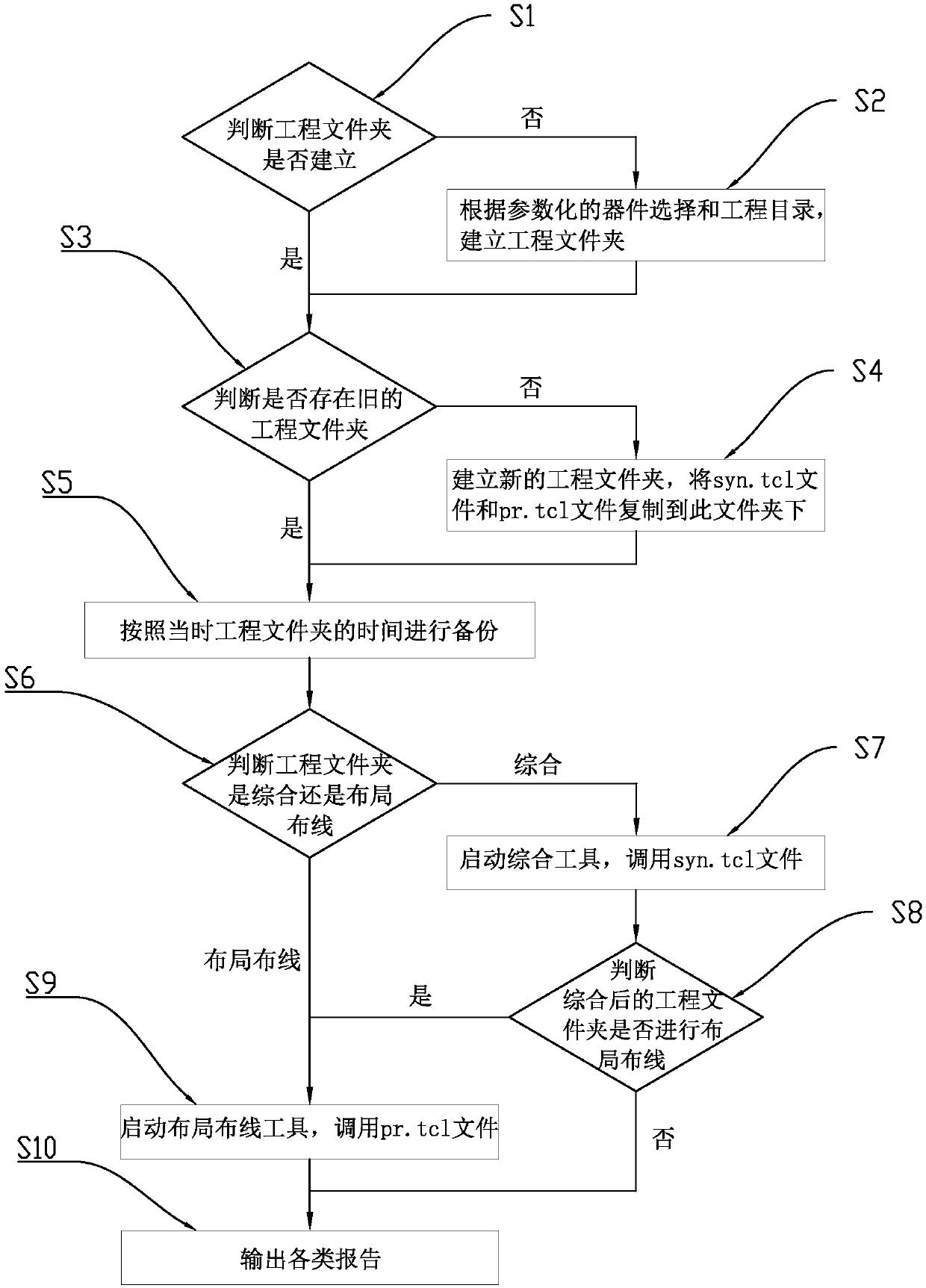

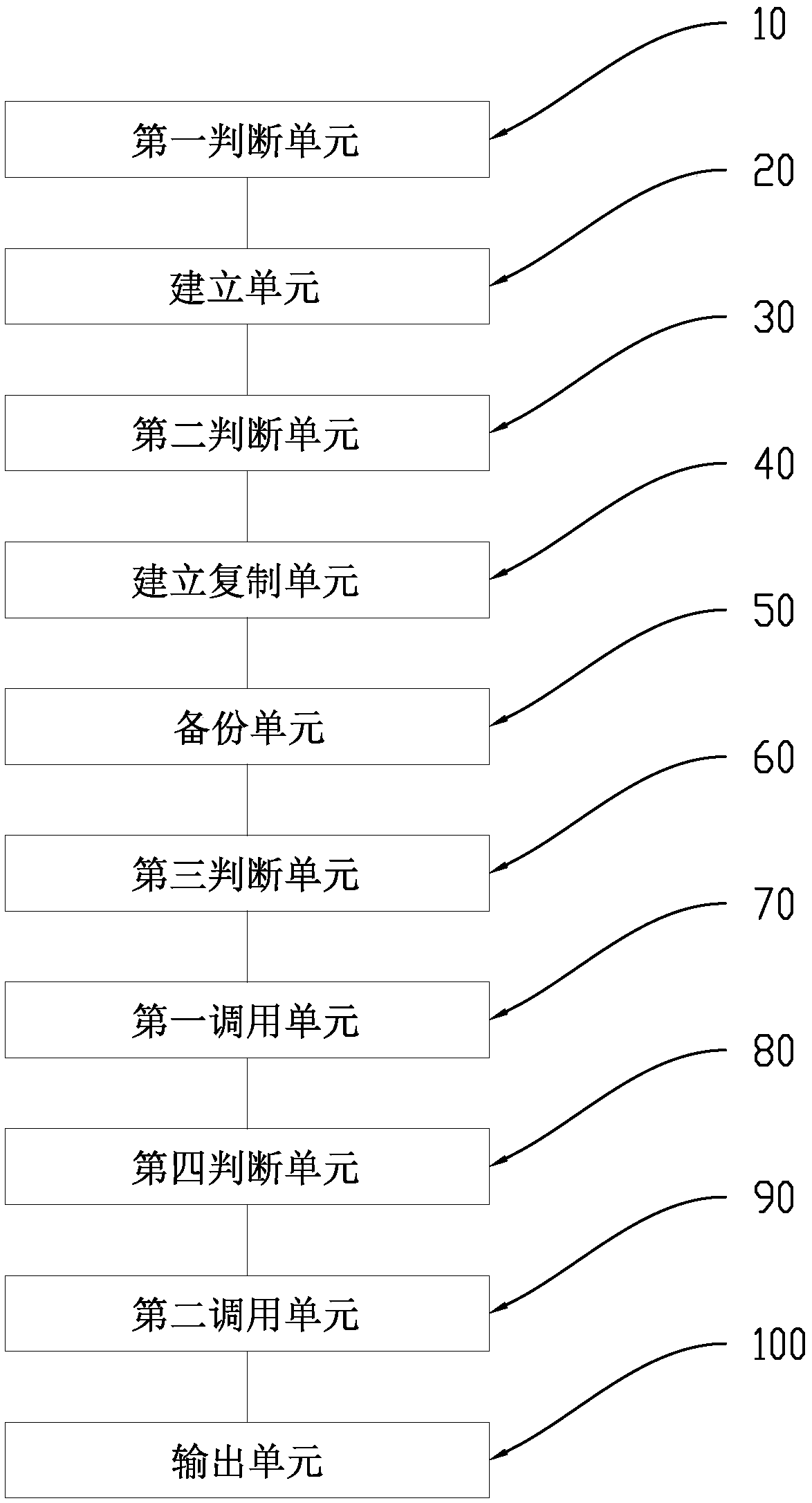

[0045] Such as Figure 1 to Figure 2 Shown specific embodiment, wherein, the present invention discloses the method for SOC chip field programmable logic array prototype synthesis, comprises the following steps:

[0046] S1, determine whether the project folder is established; if so, enter S3; if not, enter S2;

[0047] S2, according to the parameterized device selection and project directory, establish a project folder for storing data;

[0048] S3, judging whether there is an old project folder; if so, enter S5; if not, then enter S4;

[0049] S4, create a new project folder, and copy the syn.tcl file and the pr.tcl file to this folder;

[0050] S5, back up according to the time of the current project folder;

[0051] S6, judgi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More