Neural network chip of a binary memristor

A neural network and binary neural technology, applied in the field of computer and electronic information, can solve the problems of consuming too many memristor units, complex network structure, complex regulation, etc., and achieve the effect of improving computing efficiency and speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

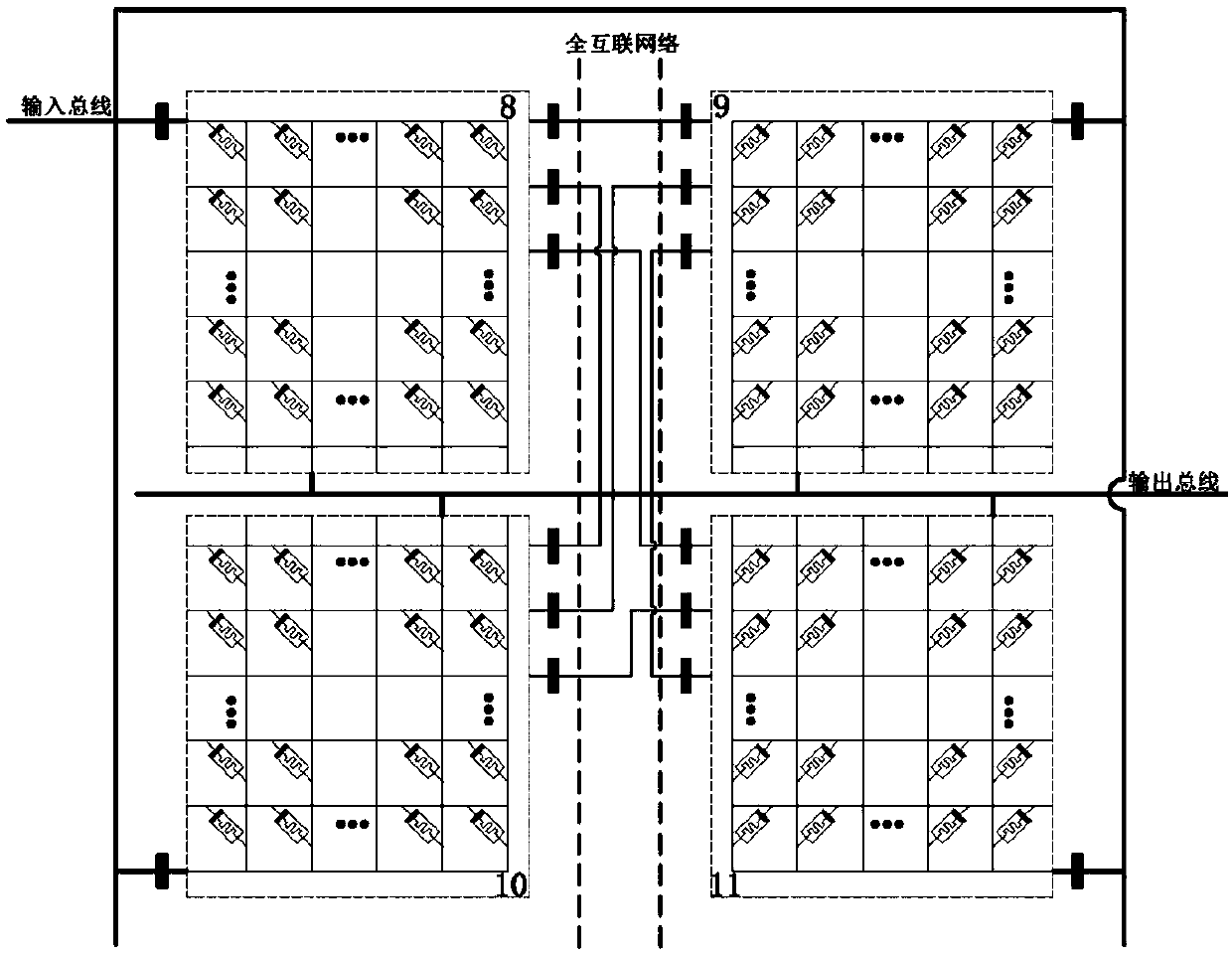

[0036] A X86-based Intel E5-2620V4 central processing unit is used for simulation with a 30*3 memristor cross-array structure.

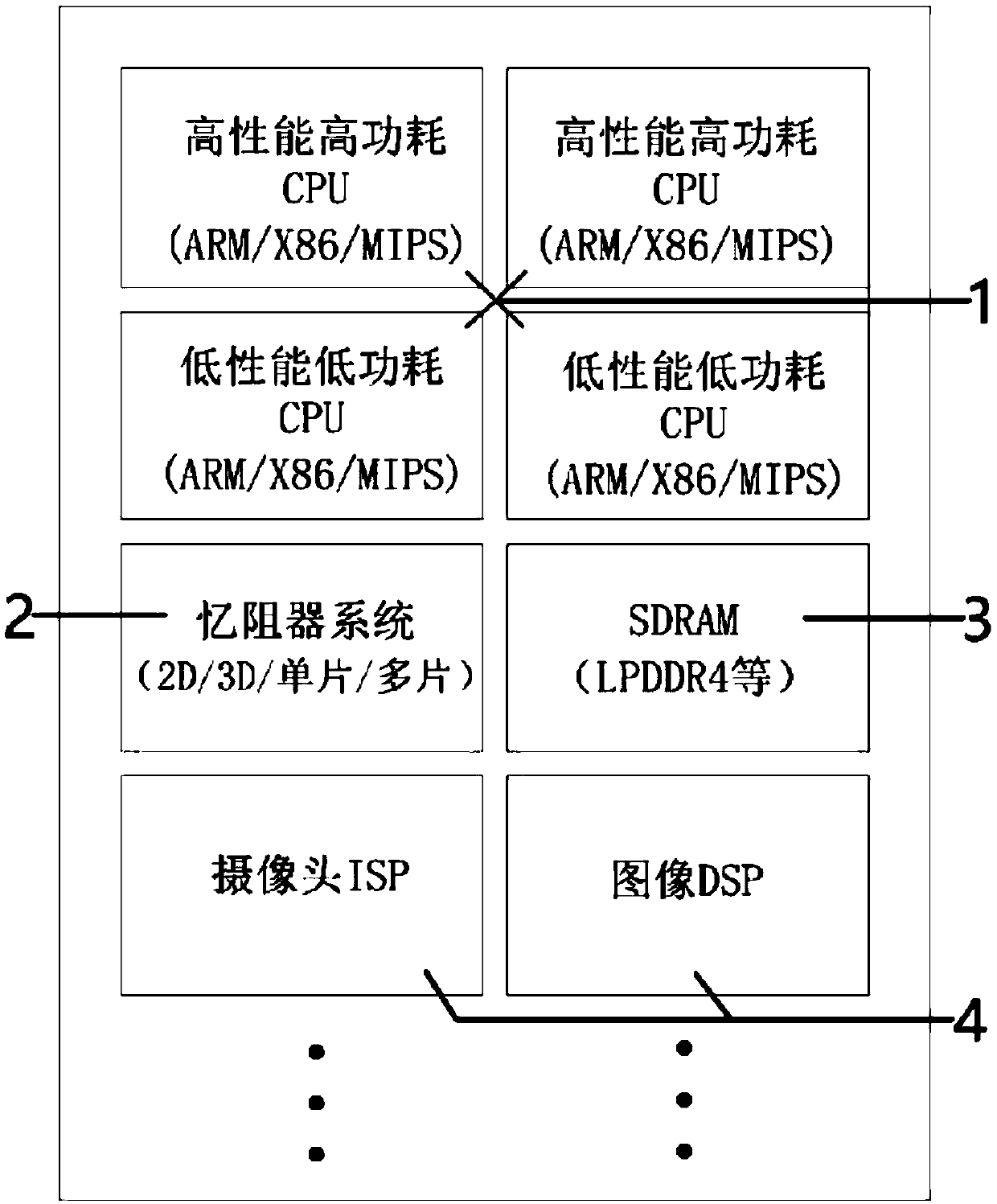

[0037] Wherein, the design of central processing unit 1 can use ARM, X86 or MIPS framework, can be divided into a plurality of single-core or multi-core central processing units with high performance, high power consumption and low performance and low power consumption according to needs, and can be selected according to the heavy degree of tasks Processed by different CPU modules. An example can be given here: 2 strongest ARM Cortex-A72 cores, clocked at 2.5GHz; 2 enhanced A53e cores, clocked at 2.0GHz; 4 ordinary low-power A53 cores, clocked at 1.4GHz, together constitute the central processing unit 1.

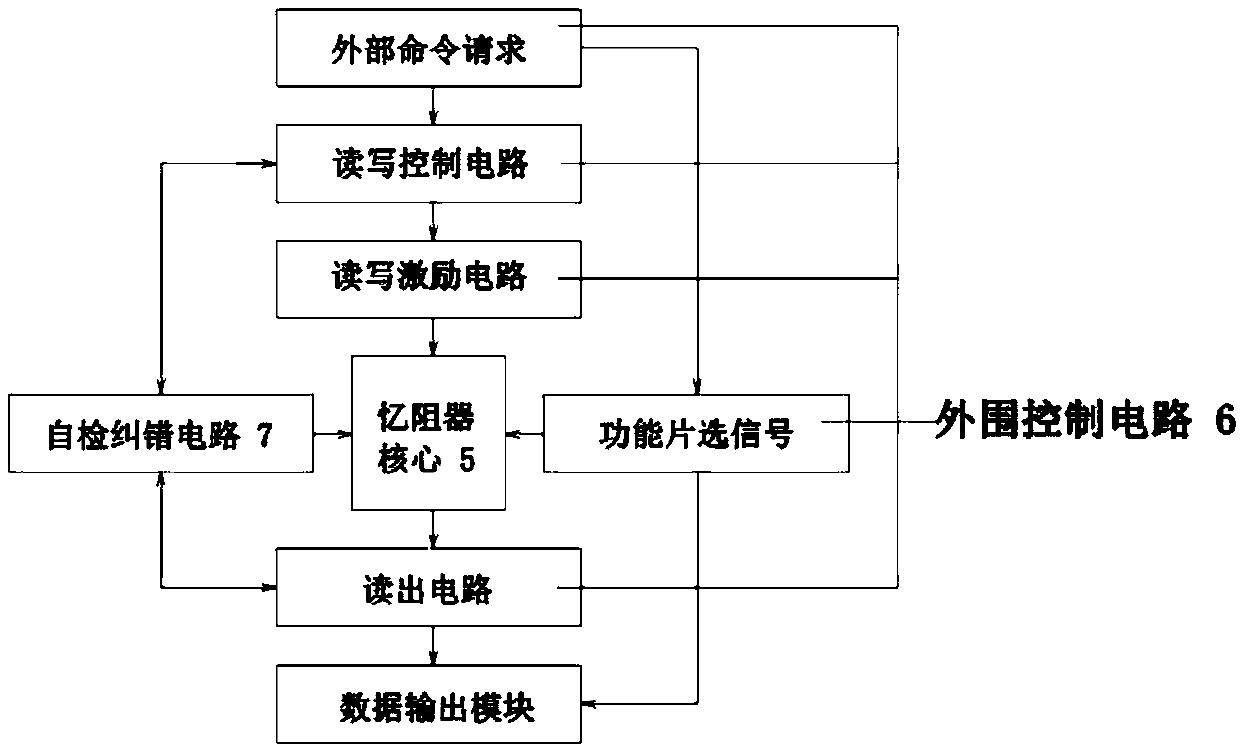

[0038] Such as image 3 As shown, in this example for figure 2 The memristor chip in the memristor core 5 a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More