Layout and wiring method suitable for improving CPU core frequency

A layout and routing, CPU core technology, applied in the field of layout and routing of CPU core frequency increase, can solve problems such as repair hold time violation, timing pessimism, impact CPU core frequency breakthrough, etc., achieve high area and controllable power consumption, simple process , The effect of speeding up the timing convergence speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

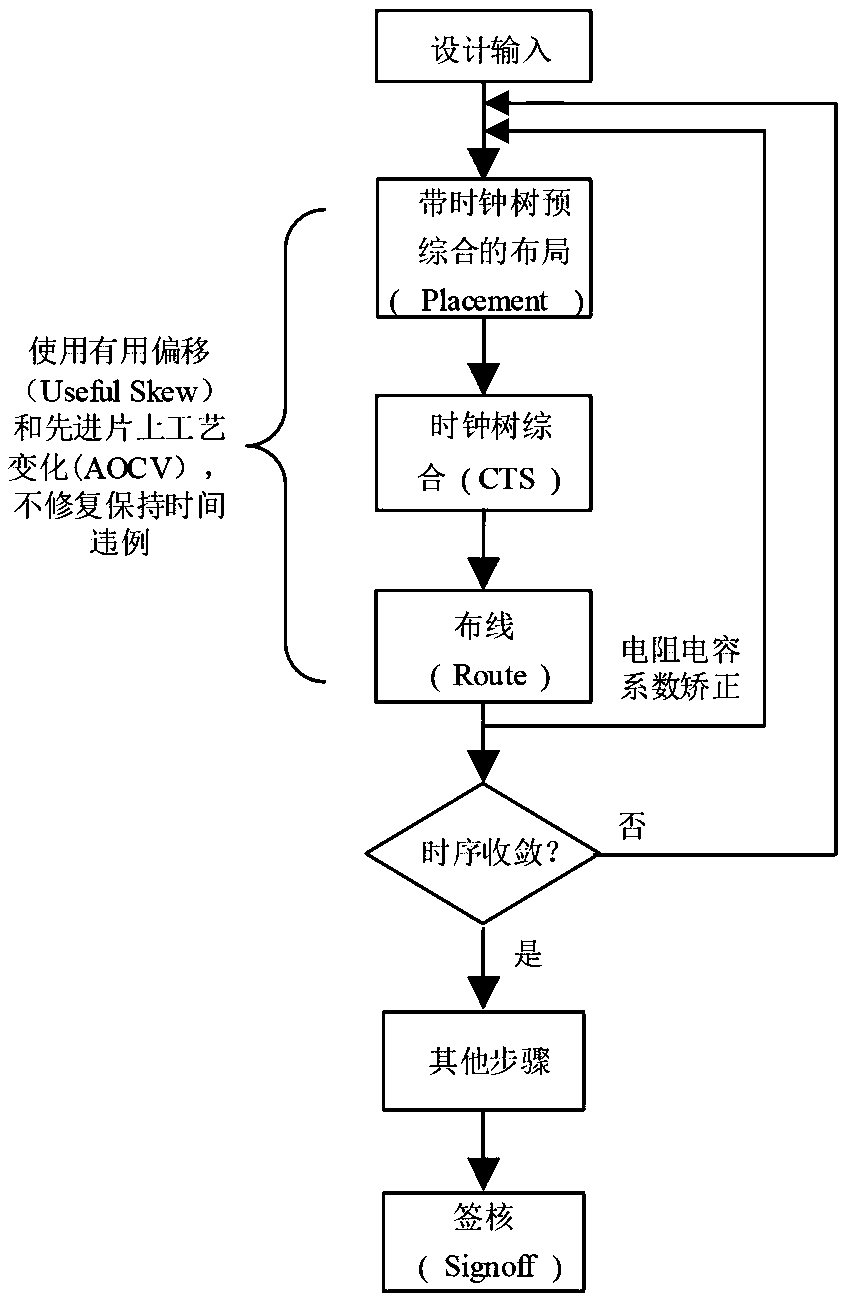

[0030] Such as figure 1 As shown, the implementation steps of the placement and routing method applicable to CPU core frequency boosting in this embodiment include:

[0031] 1) Input the design file;

[0032] 2) Set process constraints, execute layout with clock tree pre-synthesis, and do not fix hold time violations during the layout process, use useful offsets to fix setup time violations, and use advanced on-chip process changes to add different timing paths on different timing paths Process deviation value;

[0033] 3) Perform clock tree synthesis, and do not repair hold time violations during clock tree synthesis, use useful offsets to repair setup time violations, and use advanced on-chip process changes to add different process deviation values to different timing paths;

[0034] 4) Execute routing to complete the routing of clock lines and signal lines according to the rules, and do not repair hold time violations during the wiring process, use useful offsets to re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com