Polysilicon thin film transistor and manufacturing method thereof

A technology of polysilicon thin film and manufacturing method, which is applied in the direction of transistor, semiconductor/solid-state device manufacturing, semiconductor device, etc., can solve the problems of transistor characteristic loss, source and drain punch-through, etc., to improve characteristics, prevent source-drain punch-through, and reduce overlap Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

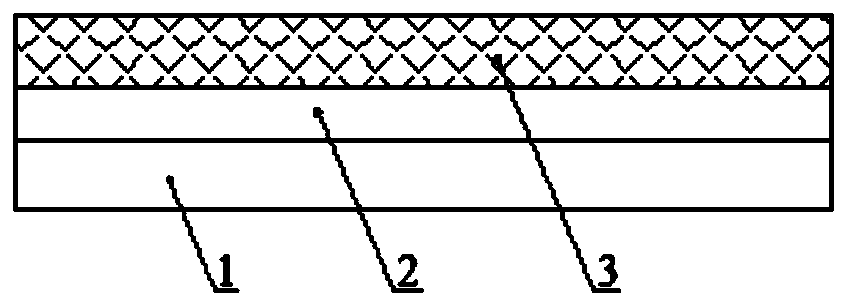

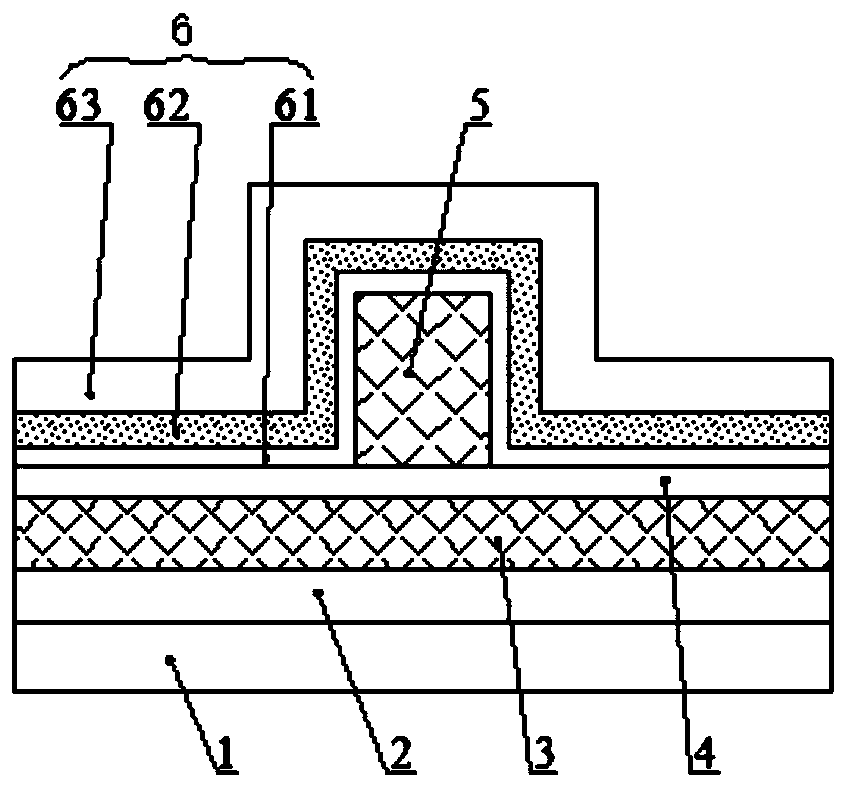

[0031] The inventor found that the channel length of polysilicon thin film transistors tends to be narrower compared with single crystal silicon thin film transistors. In order to solve the problem of narrowing the channel length of polysilicon thin film transistors, the inventors tried to reduce the dose of light doping by ion implantation , but it is found that since the gate, source and drain of the polysilicon thin film transistor are implanted with ions at the same time, if the dose of lightly doped ion implantation in the source and drain regions is reduced, the dose of lightly doped ion implanted in the gate will also be reduced, so First, it will cause the threshold voltage of the thin film transistor to drift.

[0032] In the embodiment of the present invention, the first ion implantation process is performed to implant ions into the polysilicon gate layer; the second ion implantation process is performed to inject ions into the polysilicon gate layer and the polysilic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More