gate drive circuit

A gate drive circuit and gate drive technology, applied in static indicators, instruments, etc., can solve problems such as threshold voltage drift easily and gate drive circuit failure.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to make the purpose, technical means and effects of the present invention clearer, the present invention will be further elaborated below in conjunction with the accompanying drawings. It should be understood that the embodiments described here are only some, not all, embodiments of the present invention, and are not intended to limit the present invention.

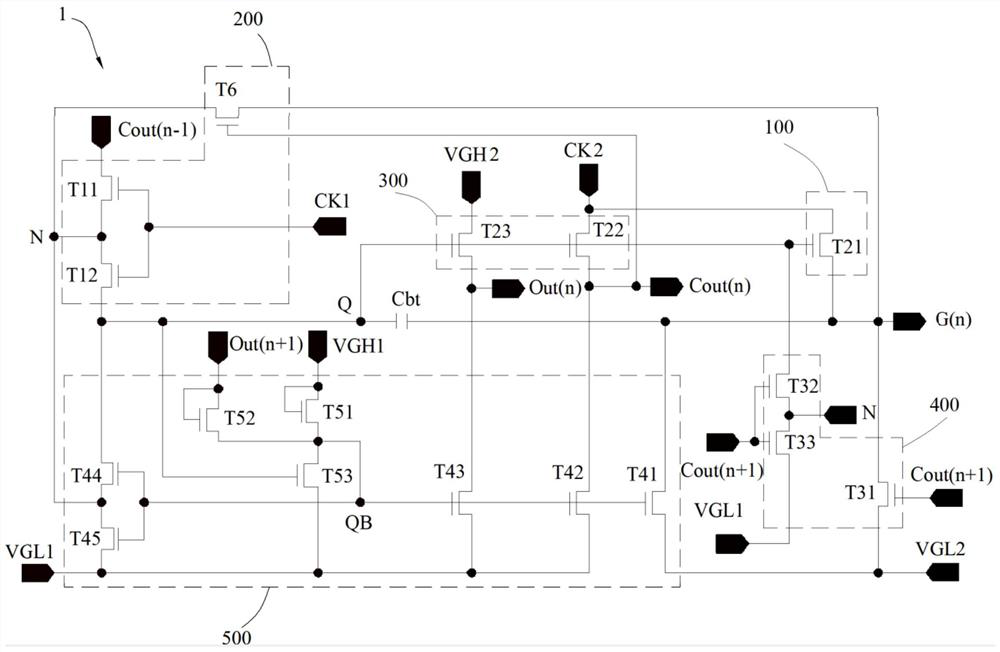

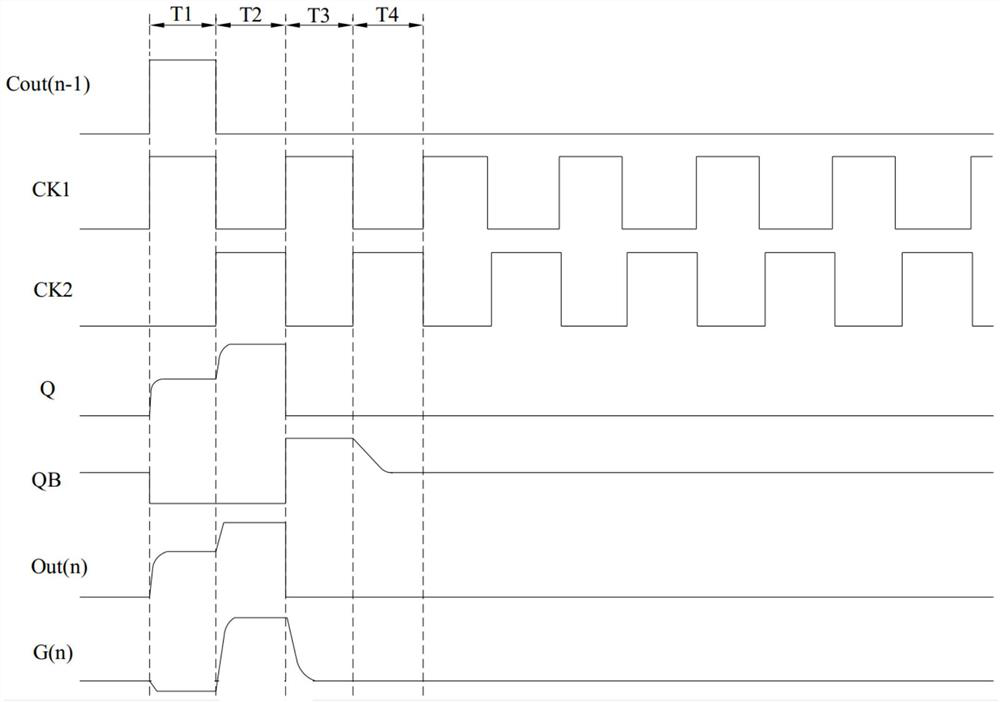

[0020] Please refer to figure 1 , which shows a schematic circuit structure diagram of a gate driving circuit according to an embodiment of the present invention. The gate drive circuit includes a plurality of cascaded gate drive units 1, and the gate drive unit 1 includes a pull-up unit 100, a pull-up control unit 200, a downlink unit 300, a pull-down unit 400, a pull-down sustain unit 500 and a bootstrap capacitor Cbt. In this embodiment, the first clock signal CK1 and the second clock signal CK2 are AC signals with opposite waveforms. Specifically, the second DC low voltage VGL2 is greater than the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More