An integrated semiconductor device and electronic device

A technology for semiconductors and devices, applied in the field of integrated semiconductor devices and electronic devices, can solve the problems of increased process cost, insufficient depletion, thermal burnout of devices, etc., to improve breakdown reliability, save chip area, and reduce switching loss. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0033] In the following, the integrated semiconductor device of the present invention will be illustrated by taking an integrated VDMOS semiconductor device as an example. It should be understood that the description of this embodiment by taking an example of an integrated VDMOS semiconductor device is only exemplary, and any integrated depletion-mode device and The manufacturing method of the integrated semiconductor device of the enhanced device is applicable to the present invention.

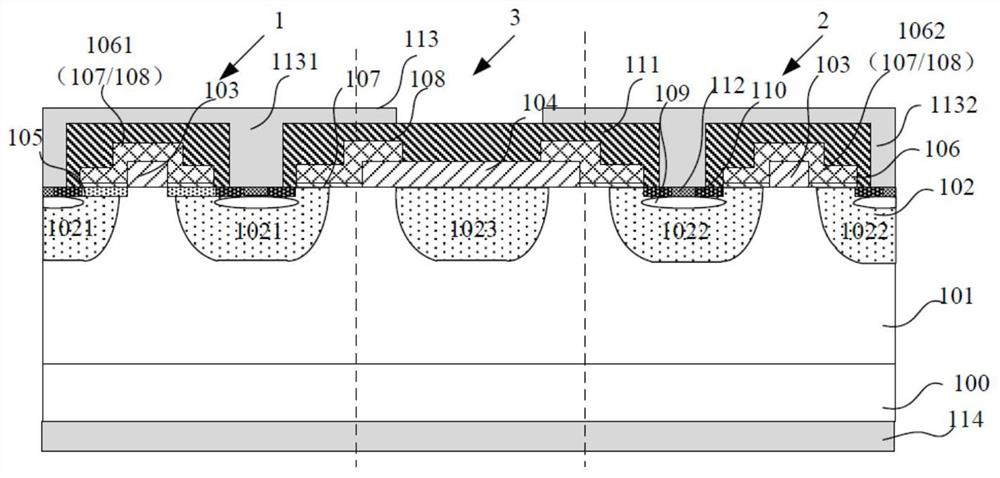

[0034] In order to solve the problems in the prior art, the present invention provides an integrated semiconductor device. face to face figure 1 The structure of the semiconductor device of the present invention is described exemplarily.

[0035] Integrated semiconductor device described in the present invention comprises:

[0036] semiconductor substrate;

[0037] a first doping type epitaxial layer, located on the front side of the semiconductor substrate, including a first region, a sec...

Embodiment 2

[0072] In this embodiment, an integrated IGBT device is also provided, and the integrated IGBT device includes a depletion-type IGBT device and an enhancement-type IGBT device. Specifically, the semiconductor substrate in Embodiment 1 is set to the second doping type, that is, the semiconductor substrate is a P-type substrate, while the formation positions and doping types of other components in Embodiment 1 remain unchanged. Specifically , the IGBT device includes:

[0073] a semiconductor substrate of a second doping type;

[0074] a first doping type epitaxial layer, located on the front side of the semiconductor substrate, including a first region, a second region and a third region, and an isolation structure is provided in the third region;

[0075] A second doping type deep well located in the first doping type epitaxial layer, including at least two located in the first region and at least two located in the second region;

[0076] a dielectric island, located on the...

Embodiment 3

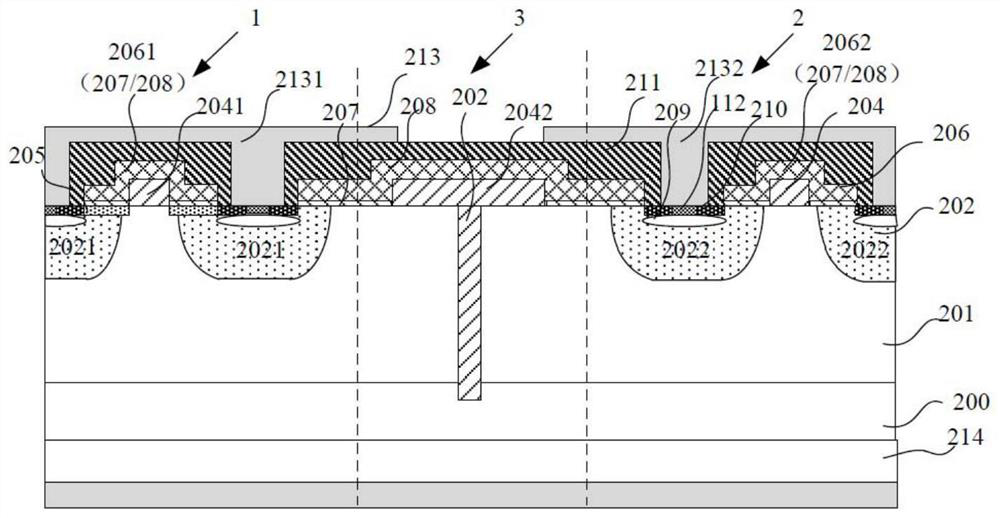

[0084] Refer below figure 2 The structure of another integrated semiconductor device according to the present invention will be described.

[0085] like figure 2 As shown, an integrated semiconductor device according to the present invention includes a semiconductor substrate 200 . The semiconductor substrate 200, specifically, may be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP, InGaAs or other III / V compound semiconductors, including these Multi-layer structure of semiconductor, or silicon on insulator (SOI), silicon on insulator (SSOI), silicon germanium on insulator (S-SiGeOI), silicon germanium on insulator (SiGeOI) and germanium on insulator ( GeOI) and so on. Exemplarily, the semiconductor substrate is of the first doping type.

[0086] It should be noted that, in this specification, the first doping type and the second doping type generally refer to P type or N type, wherein the first doping type is opposite to the seco...

PUM

| Property | Measurement | Unit |

|---|---|---|

| length | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More