A method of manufacturing a semiconductor device and an integrated semiconductor device

A manufacturing method and semiconductor technology, which is applied in the manufacture of semiconductor devices and the field of integrated semiconductor devices, can solve problems such as increased process costs, increased device power consumption, and insufficient depletion, so as to improve breakdown reliability and reduce gate Capacitance, process cost reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

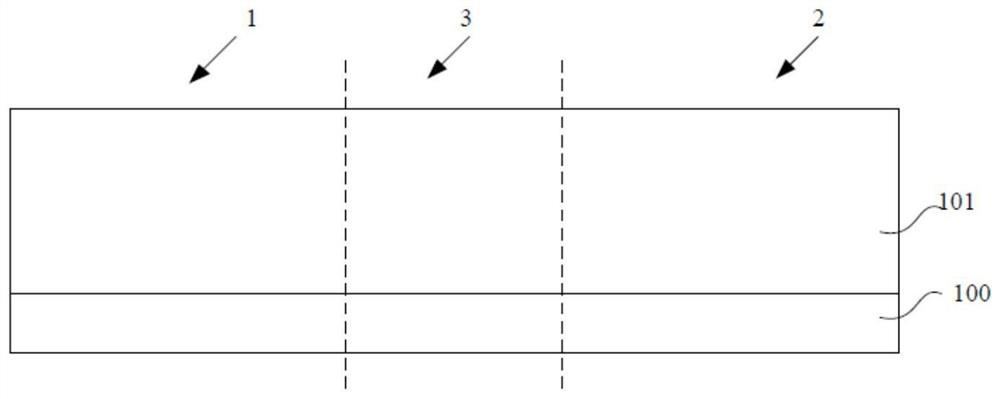

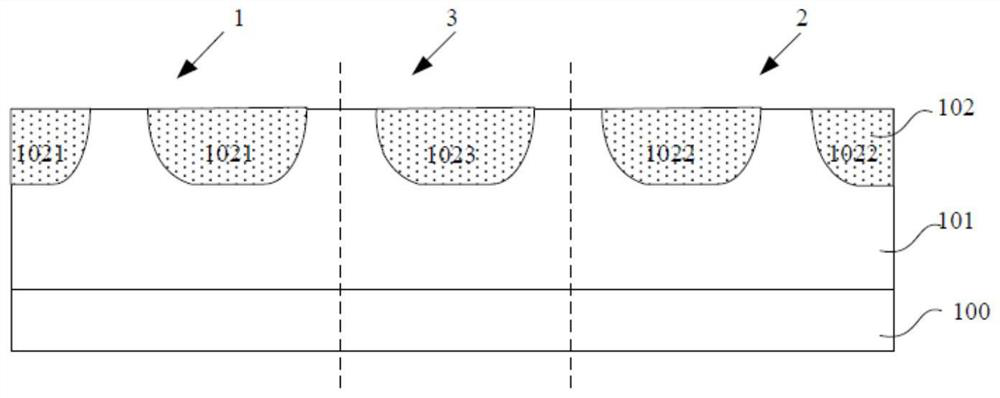

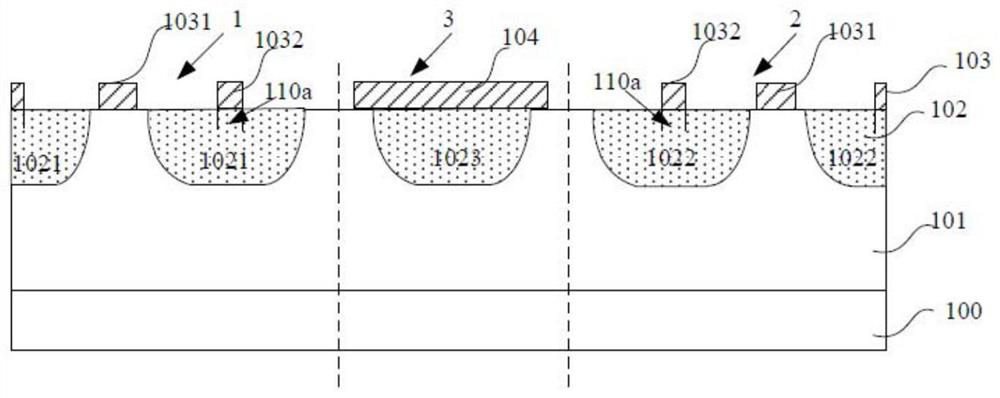

[0037] see below Figures 1A-1G , figure 2 A method for manufacturing a semiconductor device and a semiconductor device proposed in the present invention are exemplarily described. in, Figures 1A-1G is a schematic structural view of a semiconductor device formed in a method for manufacturing a semiconductor device according to an embodiment of the present invention, figure 2 It is a flowchart of a manufacturing method of a semiconductor device according to an embodiment of the present invention.

[0038] First, see figure 2 , performing step S1: providing a semiconductor substrate of the first doping type, and forming an epitaxial layer of the first doping type having a first region and a second region on the front surface of the semiconductor substrate of the first doping type.

[0039] Such as Figure 1AAs shown, the semiconductor substrate 100 of the first doping type is provided, specifically, it may be at least one of the materials mentioned below: Si, Ge, SiGe, ...

Embodiment 2

[0088] The present invention also provides an integrated semiconductor device, which includes the semiconductor device prepared according to the method in the first embodiment.

[0089] see below Figure 1G , to exemplarily describe the structure of the integrated semiconductor device of the present invention. The integrated semiconductor device includes: a semiconductor substrate 100 of a first doping type. The semiconductor substrate 100 of the first doping type, specifically, may be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP, InGaAs or other III / V Compound semiconductors, including multilayer structures composed of these semiconductors, or silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI), silicon-germanium-on-insulator (SiGeOI) ) and germanium on insulator (GeOI), etc.

[0090] It should be noted that, in this specification, the first doping type and the second doping type gen...

PUM

| Property | Measurement | Unit |

|---|---|---|

| length | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More