Self-adaptive adjusting circuit and self-adaptive adjusting method for evaluation phase duration of asynchronous SAR analog-to-digital converter

An analog-to-digital converter and self-adaptive adjustment technology, applied in the communication field, achieves the effect of low cost and increased chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

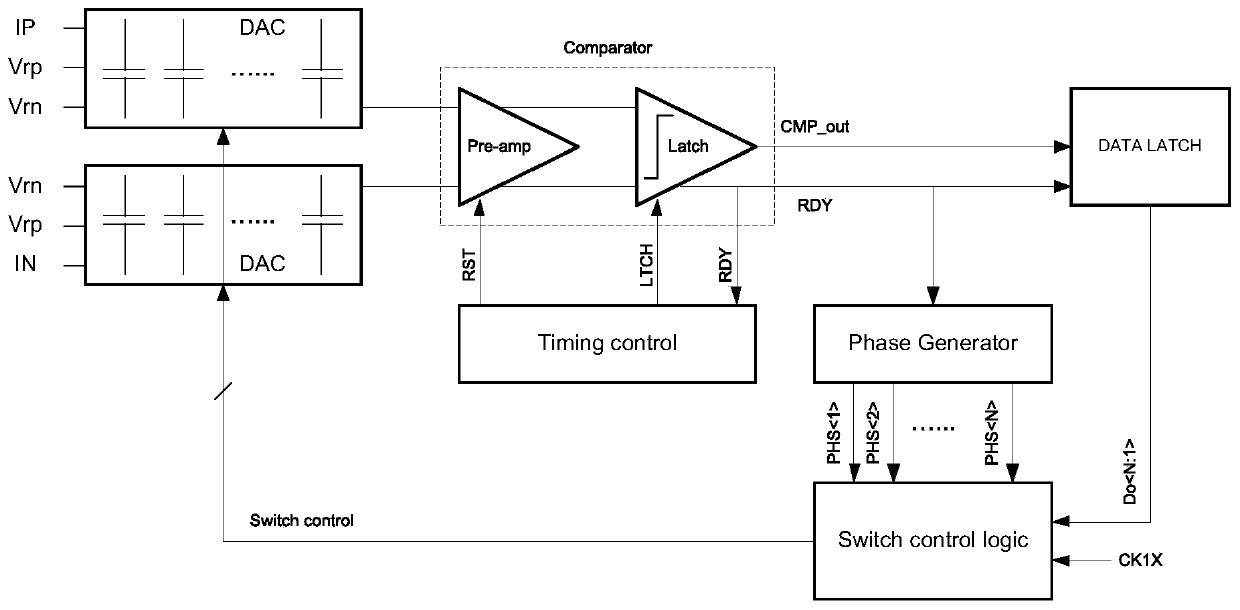

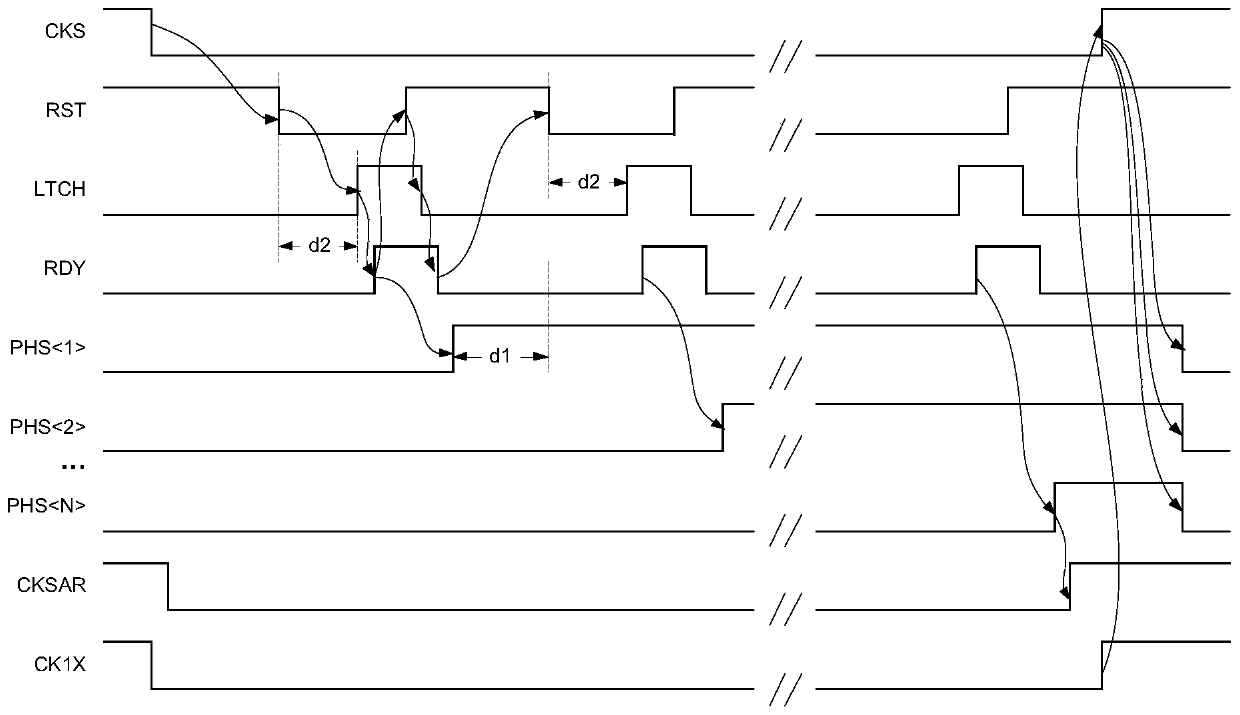

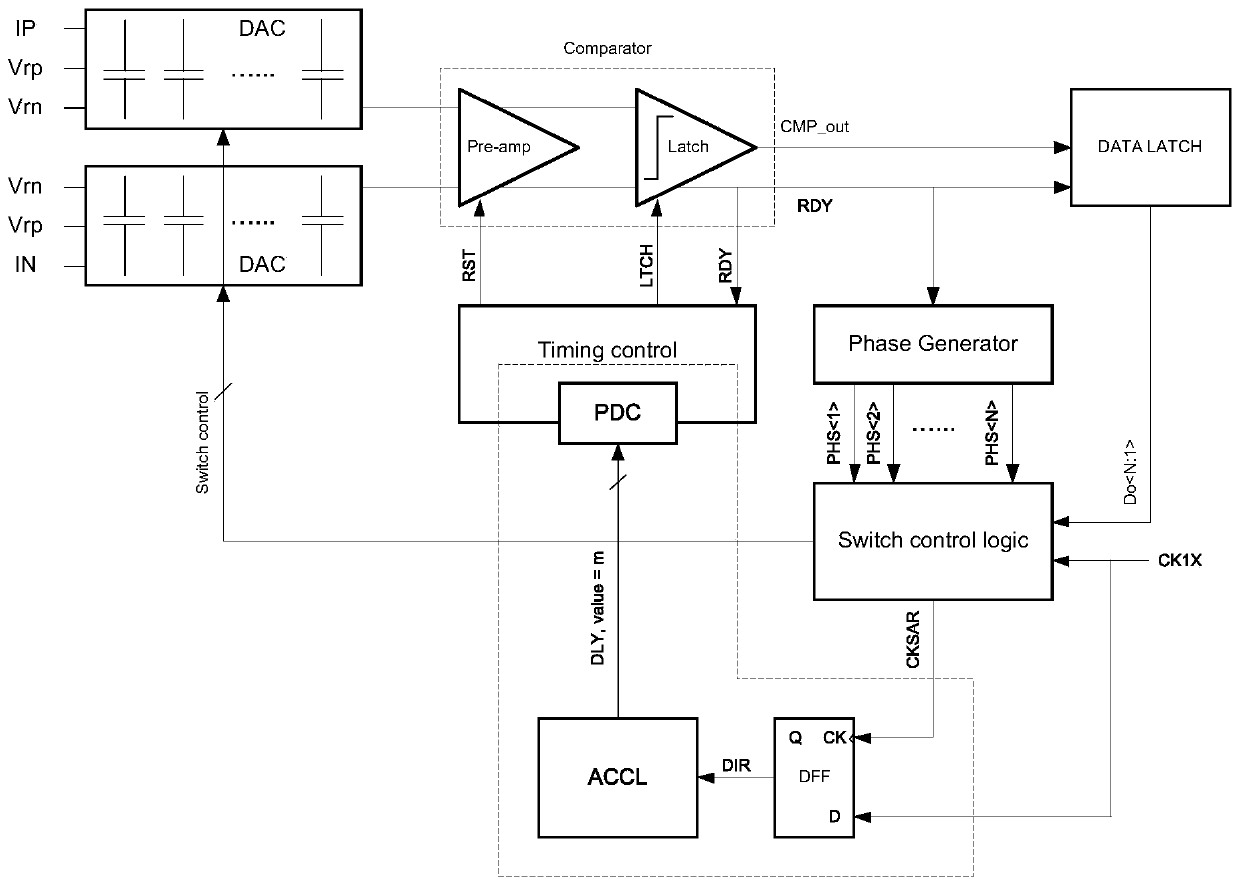

[0042] like image 3 As shown, on the basis of the structure of the usual asynchronous SARADC, this embodiment adds: a programmable delay unit, a clock edge comparator, and a comparison phase duration adaptive control logic, specifically:

[0043] 1) Programmable delay unit (PDC, programmable delay cell), such as Figure 4 As shown, it is used to provide the settling time of the DAC and Pre-amp. For the convenience of description, the input control and delay amount of the delay unit are simplified. The input is m, and the corresponding delay DLY(m) is generated. The larger m is, the greater the delay is, that is, the greater DLY(m) is. m has a maximum value m_max and a minimum value m_min, which is determined by its control word length. There are many ways to implement the PDC.

[0044] 2) Clock edge comparator (CEC, clock edge comparator), such as Figure 5 As shown, it uses the comparison completed flag bit CKSAR as input A, the externally provided sampling cloc...

Embodiment 2

[0059] This embodiment adopts PHS (k=1,2,...,N) as the input A of CEC, that is, use PHS To replace CKSAR, through the loop control of CEC+ACCL, PHS will eventually The rising edge of CK1X is roughly aligned with the rising edge of CK1X, and PHS has a total of N phases, resulting in a final SARADC comparison evaluation phase duration of about (N / k)*T / 2. In the design of high-speed SARADC, according to application requirements and design difficulty, a certain sampling time is sometimes borrowed to make up for the lack of comparison evaluation time.

[0060] like Figure 12 As shown, in this embodiment, a data selector (MUX) is added between the phase generator (PhaseGenerator) and the D-type flip-flop (DFF), and PHS_SEL is used to select the corresponding PHS output to the DFF, that is, PHS_SEL selects a certain channel of PHS To replace the CKSAR signal, extend the time of the comparison evaluation phase of the SARADC. The purpose of doing this is usually to improve th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More