High-density antifuse semiconductor memory

An anti-fuse, semiconductor technology, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve the problems of unfavorable IC integration, low utilization rate of silicon wafers, etc., and achieve the effect of increasing density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

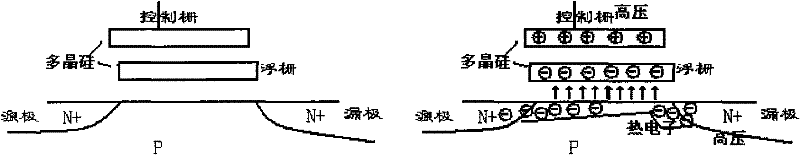

[0017] EEPROM / Flah (electrically erasable memory / flash memory) adopts a double-layer gate (two-layer poly) structure, the main structure is as follows image 3 shown. The basic principle is that when there is no electron injection in the floating gate, when the voltage is applied to the control gate, the electrons in the floating gate go to the upper layer, and holes appear in the lower layer. Due to the induction, electrons are attracted and the channel opens. If there is electron injection in the floating gate, that is, the threshold voltage of the tube is increased, the channel is in the closed state, storing logic '0', if there is no electron injection in the floating gate, the channel is in the open state, storing logic '1' '. In this way, the data storage function is realized.

[0018] In the EEPROM / Flash process, a double-layer gate (two-layer poly) process is adopted, that is, image 3 As shown in the control gate and floating gate, the present invention utilizes t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More