Function verification structure for artificial intelligence processor chip

A technology of artificial intelligence and functional verification, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of less consideration of vector and tensor support, lack of interconnection of artificial intelligence software models, etc., to save production resources, shorten the verification convergence cycle, and reduce the effect of development complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention is described in further detail now in conjunction with accompanying drawing.

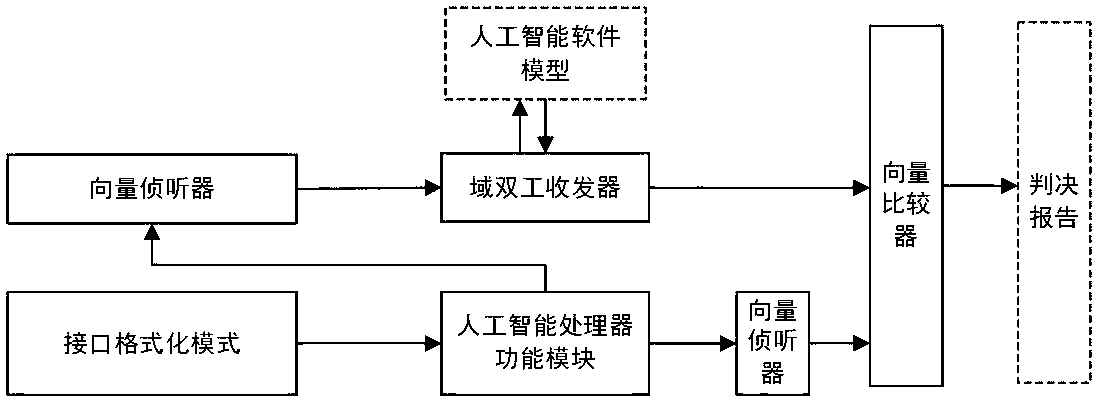

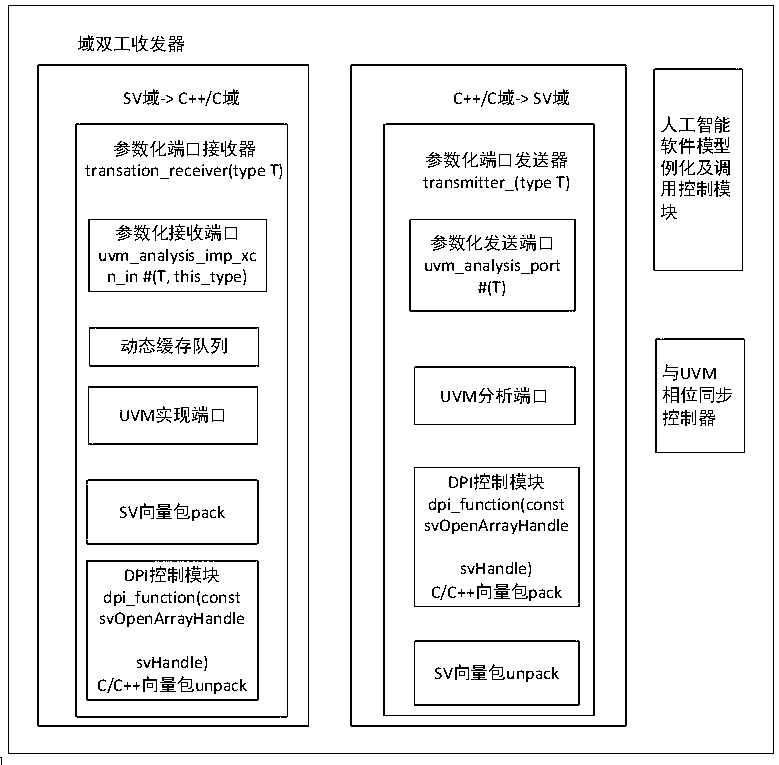

[0036] Such as figure 1 and Figure 8 As shown, a function verification structure for an artificial intelligence processor chip disclosed in the present invention includes a vector listener, a domain duplex transceiver, a vector comparator, and an interface formatting mode.

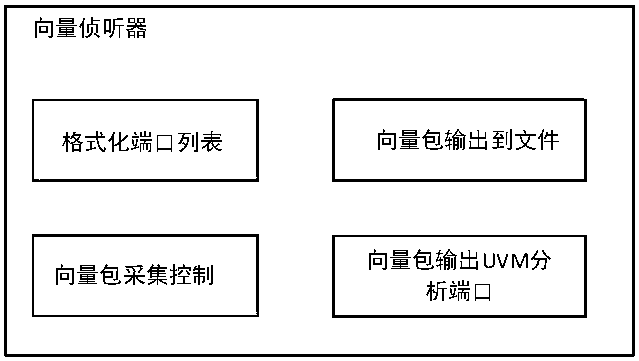

[0037] Such as Figure 8 As shown, in the vector listener and vector package generation integration process, the vector listener is connected to the interface of the artificial intelligence processor function module by the Bind connection module. The vector listener, vector package, and Bind connection modules are all based on the script program Figure 5The interface formatting pattern shown is automatically generated; the vector listener is automatically connected to the source code port of the artificial intelligence processor function module by the Bind connection module, which can significan...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More