Binary neural network accumulator circuit based on analog delay chain

A technology of binarizing neural and simulating delay, applied in biological neural network models, neural architectures, neural learning methods, etc., can solve problems such as excessive consumption of energy and hardware resources, achieve less area overhead and reduce overall power consumption , the effect of high power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical solution of the invention will be described in detail below in conjunction with the drawings, but the protection scope of the invention is not limited to the embodiments.

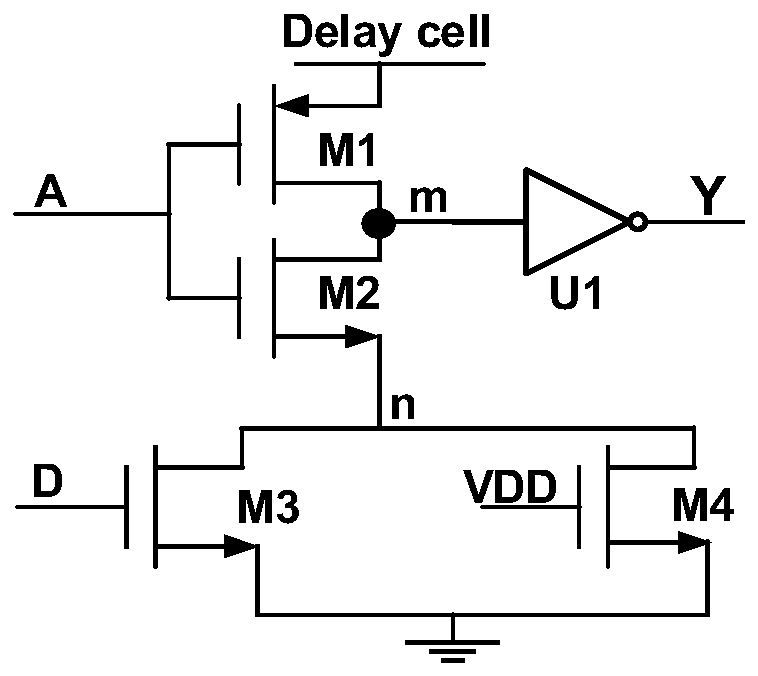

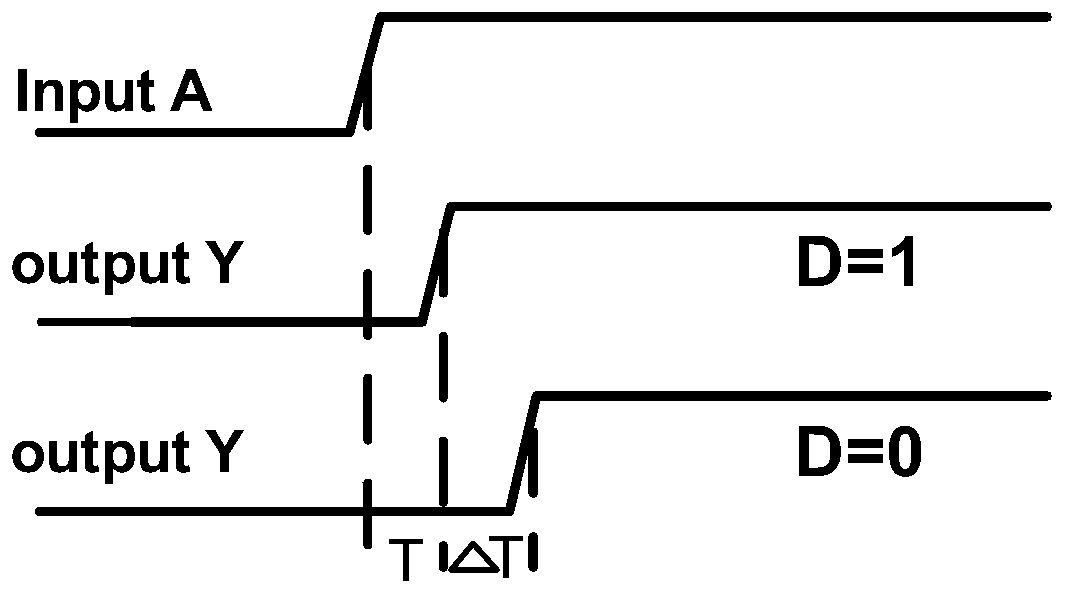

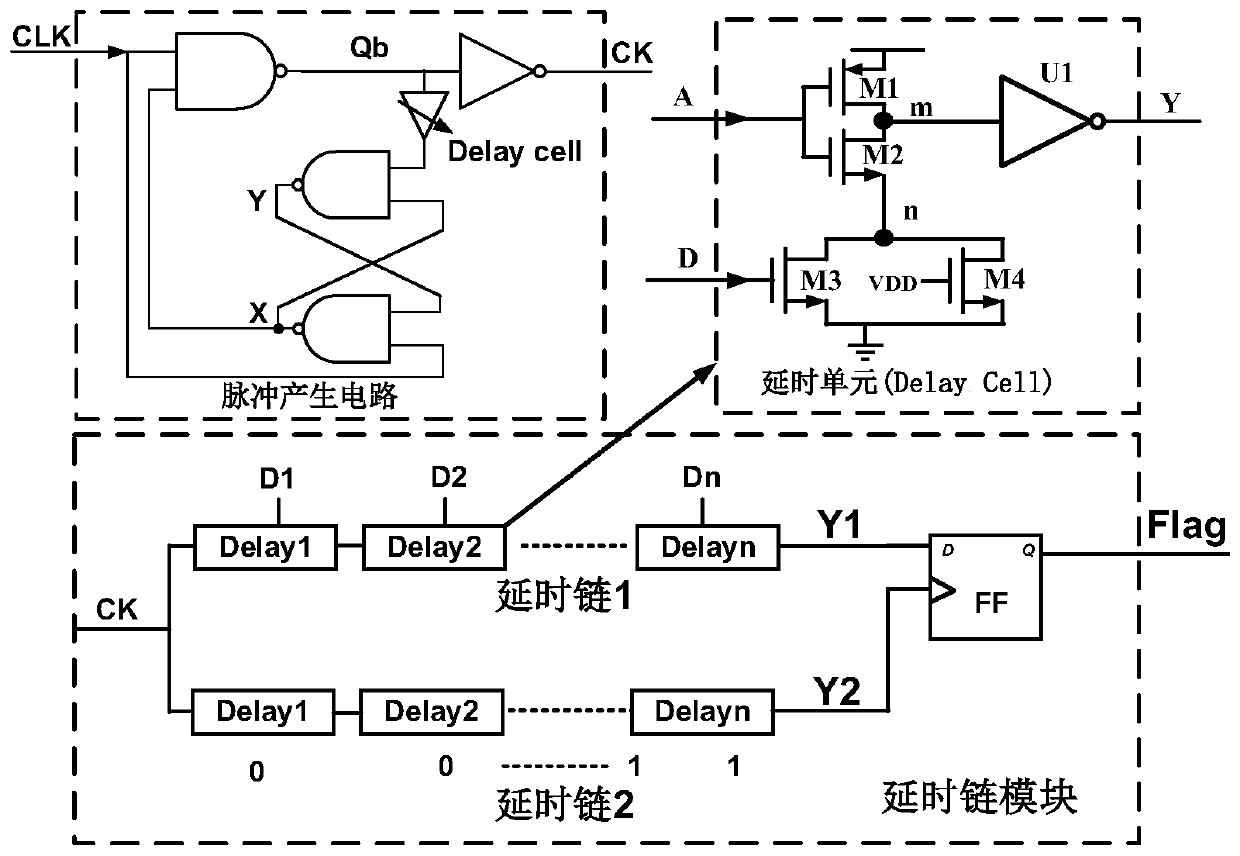

[0027] Delay unit of the present invention such as figure 1 As shown, it consists of 3 NMOS transistors, 1 PMOS transistor and an inverter. The peripheral input data A is connected to the gates of PMOS transistor M1 and NMOS transistor M2, and the peripheral input data D is connected to the gate of NMOS transistor M3. The source of the NMOS transistor M2 and the drains of the NMOS transistors M3 and M4 are connected to the node n, the sources of the NMOS transistors M3 and M4 are connected to the ground, the source of the PMOS transistor M1 and the gate of the third NMOS transistor M4 are both connected to the power supply, The drains of the PMOS transistor M1 and the NMOS transistor M2 are connected to the node m and serve as the input end of the inverter U1, and the output of the inve...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More