Warpage correction material and method for manufacturing fan out-type wafer level package

A wafer-level packaging and manufacturing method technology, applied in electrical components, electrical solid-state devices, circuits, etc., can solve problems such as warpage and deformation of circuit surfaces, and achieve the effect of reducing warpage and high quality reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0117] Next, the present invention will be described in more detail by giving examples, but the present invention is not limited to these examples.

[0118]

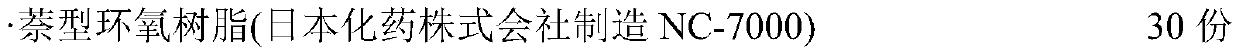

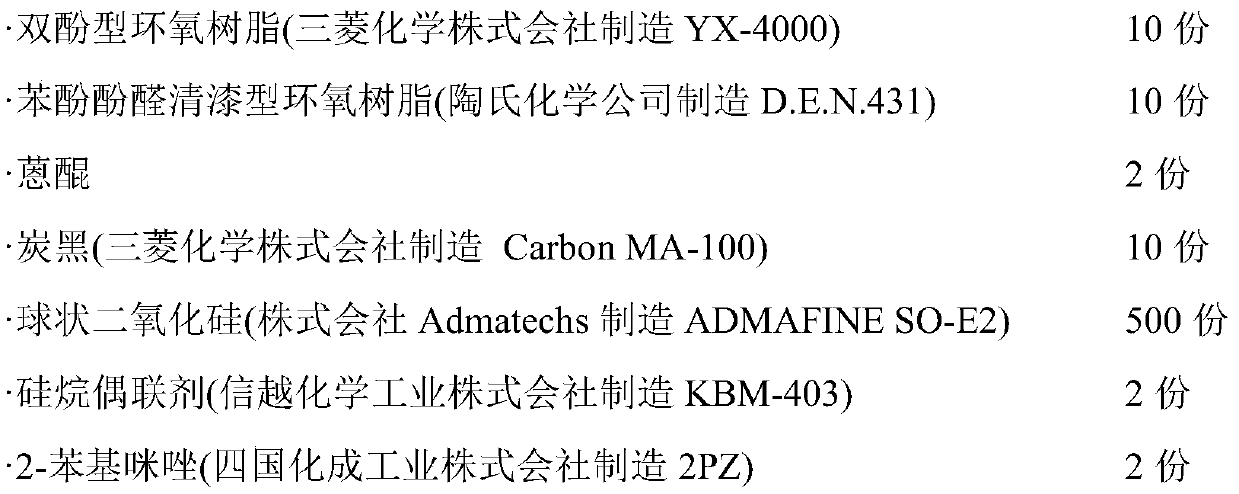

[0119] 100nm SiO formed on one side by Canosis Co., Ltd. 2 A 4-inch P-type silicon wafer with a thickness of 150 μm was diced with a dicing device to obtain semiconductor chips of 10 mm×10 mm square. Place a temporary fixing film on a flat substrate made of SUS, according to SiO 2 5 x 5 semiconductor chips were arranged vertically and horizontally in such a manner that the surface was in contact with the temporary fixing film and the semiconductor chips were spaced at 10 mm intervals in the vertical and horizontal directions. A 100 mm x 100 mm square sheet-shaped sealing material for semiconductors was laminated thereon so that the center positions were substantially aligned, and extrusion molding was performed at 150° C. for 1 hour using a heating press. As the encapsulant for semiconductors, the following material ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Epoxy equivalent | aaaaa | aaaaa |

| Acid value | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More