Level conversion circuit

A technology for converting circuits and levels, which is applied in the direction of logic circuits, logic circuit interface devices, logic circuit connection/interface layout, etc., and can solve the problem of weak pull-down capability of high-voltage NMOS transistors, inability to realize level conversion, and failure of level conversion circuits to work And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

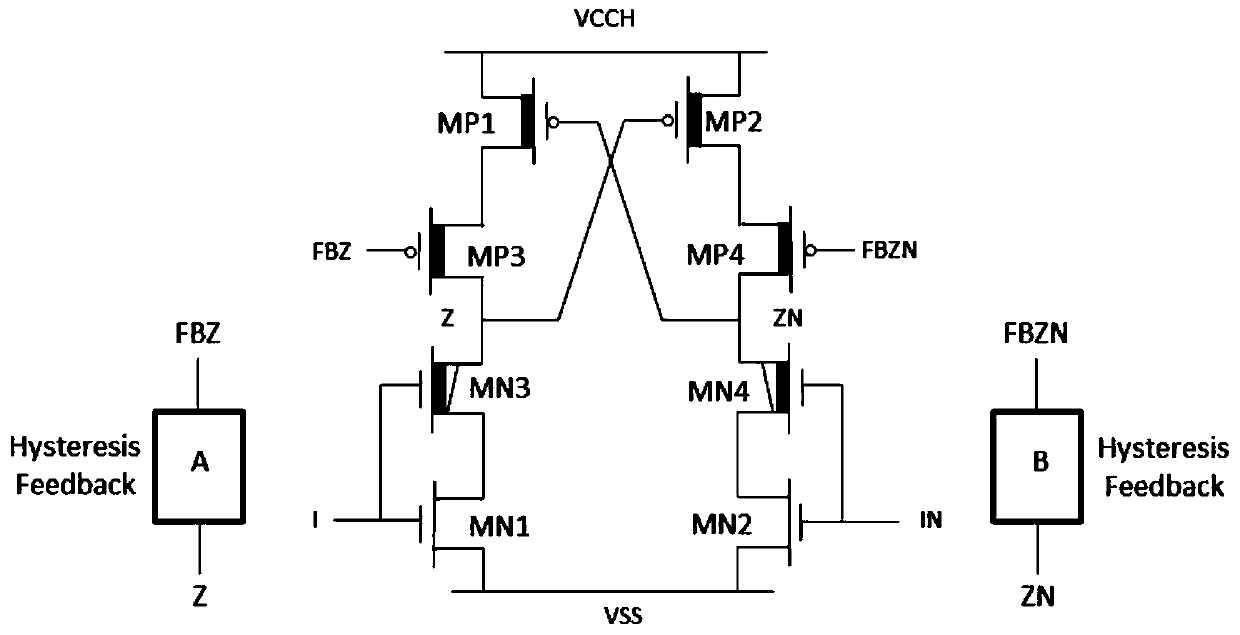

[0068] Such as figure 2 As shown, the first embodiment of the level conversion circuit provided by the present invention includes:

[0069] The source of the first NMOS transistor MN1 is grounded to VSS, its drain is connected to the source of the third NMOS transistor MN3, and its gate is connected to the gate of the third NMOS transistor MN3 as the first low-voltage input terminal I;

[0070] The source of the second NMOS transistor MN2 is grounded to VSS, its drain is connected to the source of the fourth NMOS transistor MN4, and its gate is connected to the gate of the fourth NMOS transistor MN4 as the second low-voltage input terminal IN,

[0071] The drain of the third NMOS transistor MN3 is connected to the gate of the second PMOS transistor MP2, the drain of the third PMOS transistor MP3 and the input terminal of the first hysteresis feedback circuit A, and serves as the first high voltage output terminal Z;

[0072] The fourth NMOS transistor MN4, the drain of which ...

no. 2 example

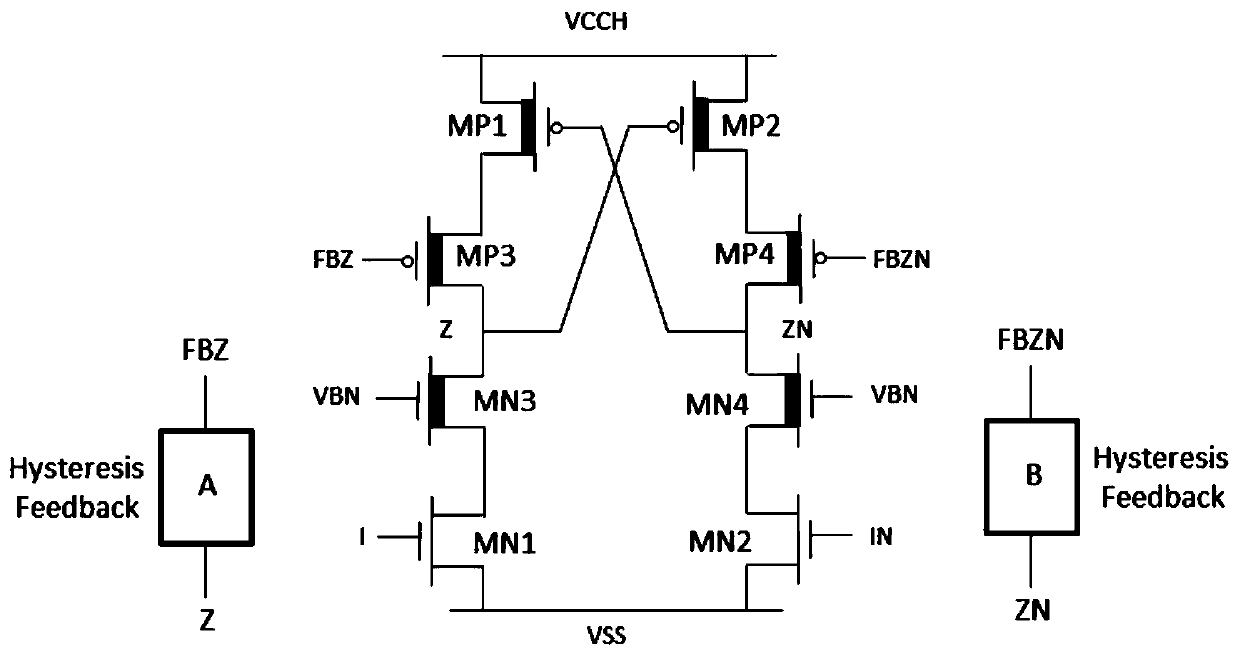

[0085] Such as image 3 As shown, the present invention provides a second embodiment of a level conversion circuit, including:

[0086] The source of the first NMOS transistor MN1 is grounded to VSS, its drain is connected to the source of the third NMOS transistor MN3, and its gate serves as the first low-voltage input terminal I;

[0087] The source of the second NMOS transistor MN2 is grounded to VSS, its drain is connected to the source of the fourth NMOS transistor MN4, and its gate is used as the second low-voltage input terminal IN;

[0088] The drain of the third NMOS transistor MN3 is connected to the gate of the second PMOS transistor MP2, the drain of the third PMOS transistor MP3 and the input terminal of the first hysteresis feedback circuit A and serves as the first high-voltage output terminal Z, and its gate is connected to the medium voltage bias Set potential VBN;

[0089] The fourth NMOS transistor MN4, its drain is connected to the gate of the first PMOS ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More