Gate and process method for improving filling ability of dielectric layer in zeroth layer

A technology of filling ability and process method, which is applied in the direction of circuits, electrical components, semiconductor devices, etc., can solve the problems of loss of isolation function, easy to be corroded by acid, and large trench aspect ratio, so as to reduce the formation of voids and improve filling The effect of limited ability and increased opening distance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings, but the technical content involved in the present invention is not limited to the specific embodiments given.

[0038] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that the drawings are all in a very simplified form and use imprecise ratios, which are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

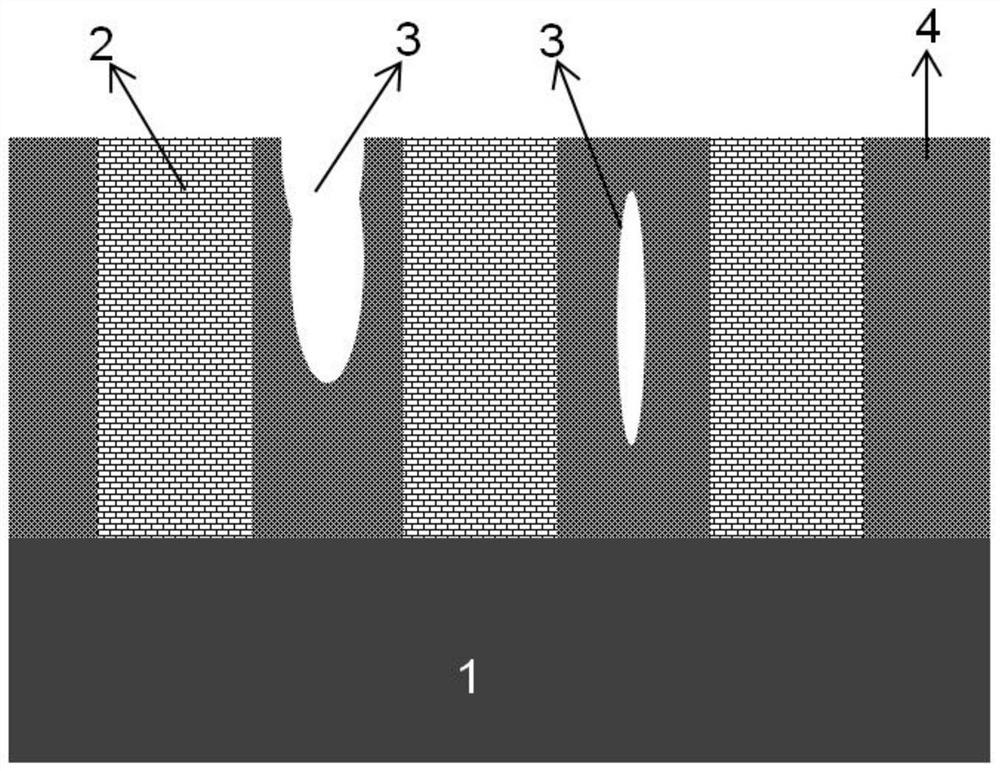

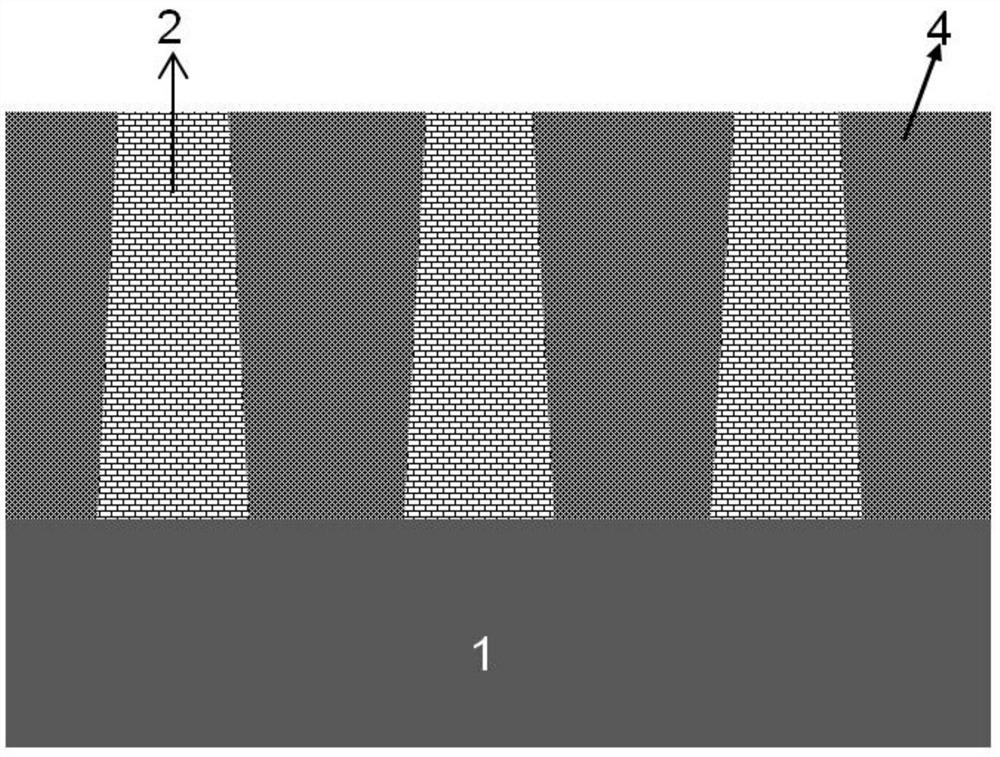

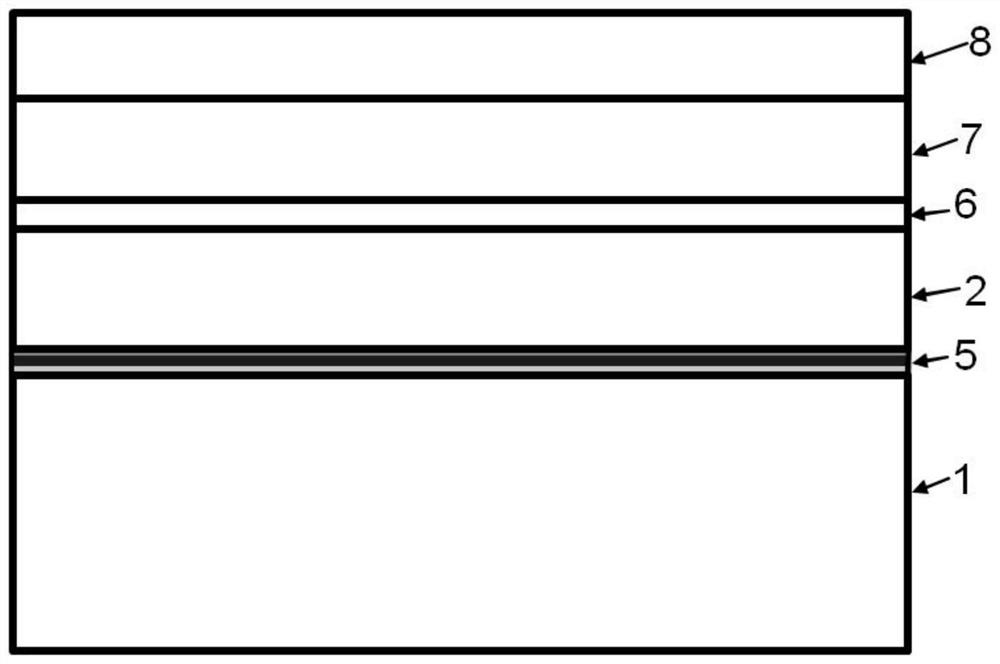

[0039] Such as figure 1 As shown, in the process node below 32nm, limited by the design rules, the gap between the gates is getting smaller and smaller, the aspect ratio ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More